DS90UB925Q-Q1

ZHCSCX8D –APRIL 2012–REVISED OCTOBER 2014

www.ti.com.cn

目目录录

7.4 Device Functional Modes........................................ 22

1 特特性性.......................................................................... 1

7.5 Programming .......................................................... 25

2 应应用用范范围围................................................................... 1

7.6 Register Maps ........................................................ 27

3 说说明明.......................................................................... 1

8 Application and Implementation ........................ 38

4 修修订订历历史史记记录录 ........................................................... 2

8.1 Application Information............................................ 38

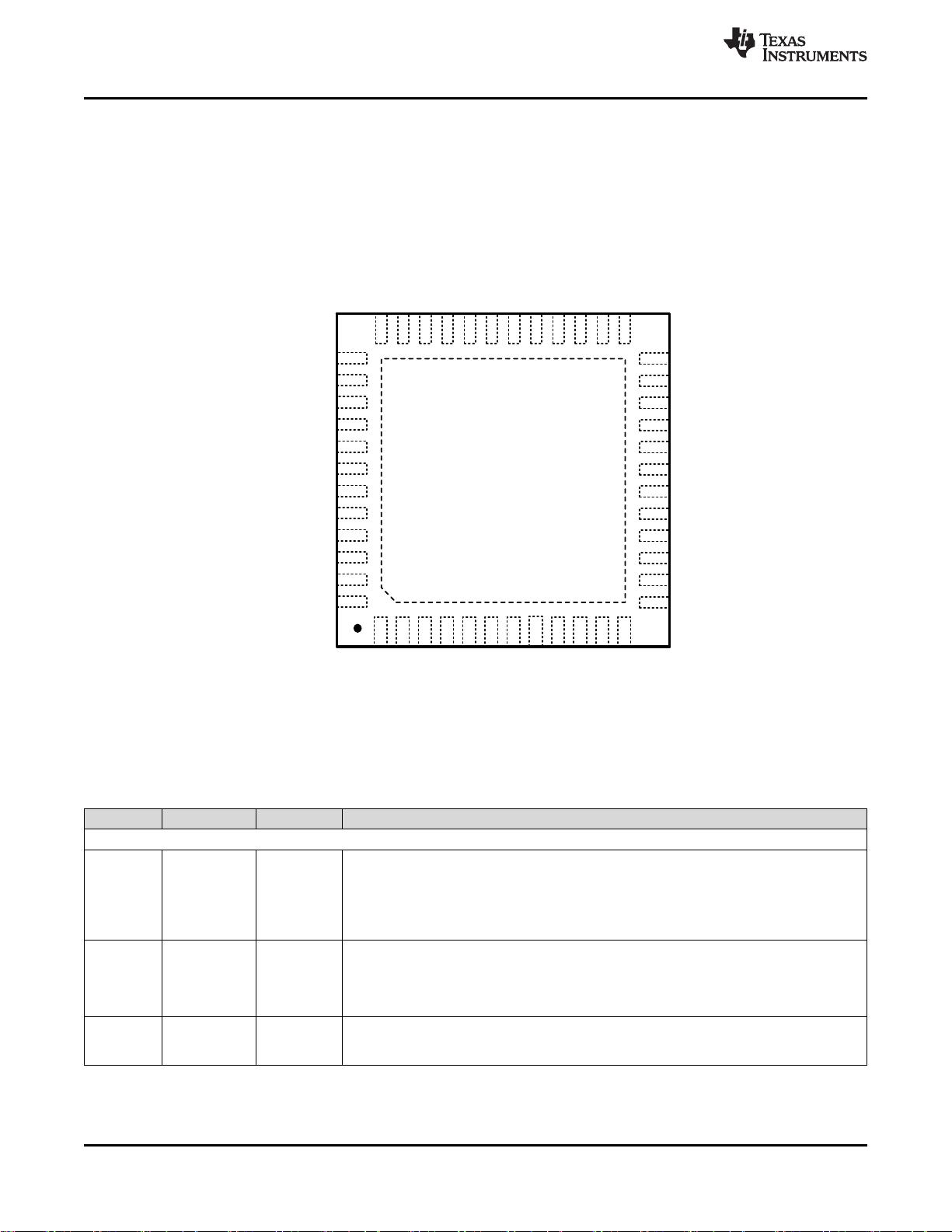

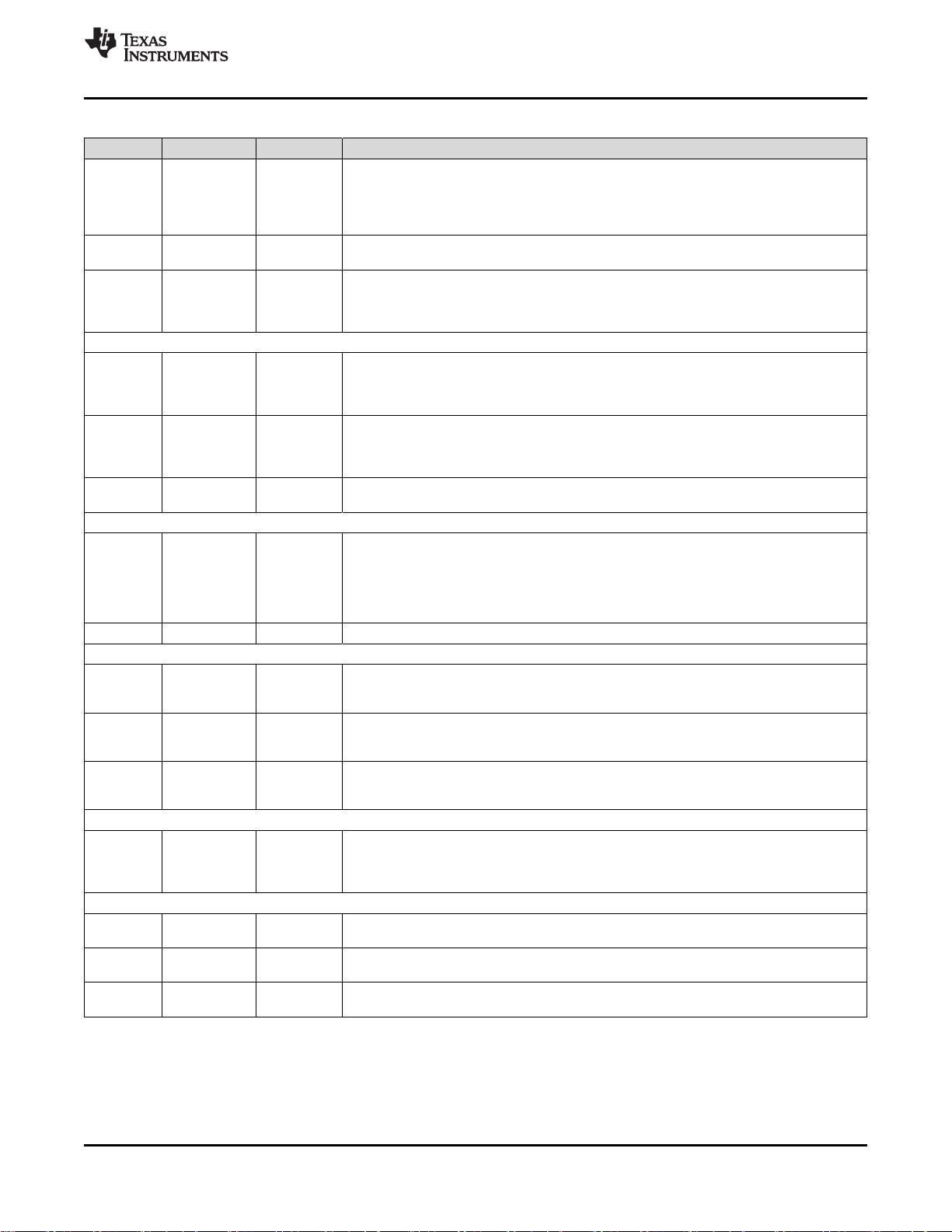

5 Pin Configuration and Functions......................... 4

8.2 Typical Application .................................................. 38

6 Specifications......................................................... 7

9 Power Supply Recommendations...................... 41

6.1 Absolute Maximum Ratings ..................................... 7

9.1 Power Up Requirements and PDB Pin................... 41

6.2 Handling Ratings....................................................... 7

9.2 CML Interconnect Guidelines.................................. 41

6.3 Recommended Operating Conditions....................... 7

10 Layout................................................................... 42

6.4 Thermal Information.................................................. 8

10.1 Layout Guidelines ................................................. 42

6.5 DC Electrical Characteristics .................................... 8

10.2 Layout Example .................................................... 43

6.6 AC Electrical Characteristics................................... 10

11 器器件件和和文文档档支支持持 ..................................................... 45

6.7 Recommended Timing for the Serial Control Bus .. 11

11.1 文档支持................................................................ 45

6.8 Switching Characteristics........................................ 13

11.2 商标 ....................................................................... 45

6.9 Typical Charateristics ............................................. 14

11.3 静电放电警告......................................................... 45

7 Detailed Description............................................ 15

11.4 术语表 ................................................................... 45

7.1 Overview ................................................................. 15

12 机机械械封封装装和和可可订订购购信信息息 .......................................... 45

7.2 Functional Block Diagram ....................................... 15

7.3 Feature Description................................................. 15

4 修修订订历历史史记记录录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision C (April 2013) to Revision D Page

• 已添加 数据表流程和版面布局,以符合全新 TI 标准。 已添加以下章节:处理额定值、器件功能模式;编程;电源建

议;布局布线;器件和文档支持;机械封装和订购信息 ......................................................................................................... 1

• 已添加 器件信息表 .................................................................................................................................................................. 1

• Fixed typo for GPIO configuration ........................................................................................................................................ 19

• Removed two MODE_SEL modes: I2S Channel B, and Backward Compatible.................................................................. 23

• Removed IDx addresses 0x22, 0x24, 0x2E, 0x30, 0x32, 0x34............................................................................................ 26

• Changed suggested resistor values for IDx addresses 0x1E, 0x20, 0x26, 0x28, 0x2A....................................................... 26

Changes from Revision B (August 2012) to Revision C Page

• 已更改 国家数据表布局至 TI 格式。 ....................................................................................................................................... 1

Changes from Revision A (July 2012) to Revision B Page

• Added typical charateristic graphics..................................................................................................................................... 14

• Added” Note: frequency range = 15 - 65MHz when LFMODE = 0 and frequency range = 5 - <15MHz when

LFMODE = 1.” under Functional Description. ...................................................................................................................... 16

• Reformatted Table 2 and added clarification to notes.......................................................................................................... 19

• Added clarification to notes on Table 6, address 0x04[3:0] (backwards compatible and LFMODE registers). .................. 27

Changes from Original (March 2012) to Revision A Page

• 已转换为混合 TI 格式。 .......................................................................................................................................................... 1

• Corrected typo in SCL from pin 6 to pin 8.............................................................................................................................. 4

• Corrected typo in SDA from pin 7 to pin 9.............................................................................................................................. 4

2 Copyright © 2012–2014, Texas Instruments Incorporated

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功