没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS90UB949A-Q1.pdf

需积分: 9 0 下载量 117 浏览量

2023-02-01

22:52:27

上传

评论 4

收藏 2.1MB PDF 举报

温馨提示

试读

84页

FPD-Link串行器

资源推荐

资源详情

资源评论

FPD-Link III

2 Lane

VDDIO

1.8 V

IDx

DOUT0+

DOUT0-

1.1V

IN_CLK-/+

HDMI

HPD

DDC

CEC

DOUT1+

DOUT1-

RIN0+

RIN0-

RIN1+

RIN1-

CLK1+/-

CLK2+/-

oLDI

D0+/-

D1+/-

D2+/-

D3+/-

D4+/-

D5+/-

D6+/-

D7+/-

DS90UB949A-Q1

Serializer

DS90UB948-Q1

Deserializer

IDx

D_GPIO

(SPI)

D_GPIO

(SPI)

LVDS Display

(2880x1080)

or Graphic

Processor

Graphics

Processor

IN_D0-/+

IN_D1-/+

IN_D2-/+

I2C

VDDIO

(3.3 V / 1.8 V)

3.3 V

I2C

1.25 V

1.8V

HDMI ± High Definition Multimedia Interface

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

本文档旨在为方便起见,提供有关 TI 产品中文版本的信息,以确认产品的概要。 有关适用的官方英文版本的最新信息,请访问 www.ti.com,其内容始终优先。 TI 不保证翻译的准确

性和有效性。 在实际设计之前,请务必参考最新版本的英文版本。

English Data Sheet: SNLS650

DS90UB949A-Q1

ZHCSJR7 –MAY 2019

DS90UB949A-Q1 2K HDMI 转转 FPD-Link III 桥桥接接器器串串行行器器

1

1 特特性性

1

• 符合面向汽车应用的 AEC-Q100 标准AEC-Q100

标准:

– 器件温度等级 2:–40°C 至 105°C,T

A

• 支持高达 210MHz 的 TMDS 时钟频率,可实现 3K

(2880x1620)(30Hz 频率)、QXGA

(2048x1536)、2K (2880x1080)、WUXGA

(1920x1200) 或 1080p60(24 位色深)

• 单路和双路 FPD-Link III 输出,支持 STP 或 STQ

或同轴电缆

• 高清多媒体 (HDMI) v1.4b 兼容输入

• HDMI 模式 DisplayPort (DP++) 输入

• 最多支持 8 通道的 HDMI 音频提取

• 高速反向通道,支持高达 2Mbps 的 GPIO

• 可跟踪扩频输入时钟以降低 EMI

• 具有 1Mbps 快速模式增强版的 I2C(主/从)

• SPI 直通接口

• 向后兼容 DS90UB926Q-Q1、DS90UB928Q-Q1

和 DS90UB924-Q1 FPD-Link III 解串器

2 应应用用

• 汽车信息娱乐系统和仪表组

– 汽车音响主机

– 汽车后座娱乐显示屏

– 汽车中心信息显示屏

– 商用车辆仪表组

– 汽车媒体中心

• 音频/视频控制系统

3 说说明明

DS90UB949A-Q1 是一款 HDMI 转 FPD-Link III 桥接

器件,当与 FPD-Link III DS90UB940-

Q1/DS90UB948-Q1 解串器配合使用时,可通过具有

成本效益的 50Ω 单端同轴电缆或 100Ω 差分屏蔽双绞

线 (STP) 和屏蔽四路绞线 (STQ) 电缆提供单通道或双

通道高速串行流。该器件可对 HDMI v1.4b 输入进行序

列化,从而支持在 60Hz 下实现高达 2880x1080 且具

有 24 位色深的视频分辨率。

FPD-Link III 接口支持通过同一条差分链路进行视频和

音频数据传输以及全双工控制(包括 I2C 和 SPI 通

信)。通过两个差分对进行视频数据整合和控制,有助

于减小应用的互连线尺寸和重量,并简化系统设计。通

过使用低压差分信令、数据换序和随机生成最大限度减

少了 EMI。在向后兼容模式中,当 DS90UB949A-Q1

与 DS90Ux92x-Q1 解串器配合使用时,可通过在单一

差分链路支持高达 1920x720 且具有 24 位色深的分辨

率。

DS90UB949A-Q1 支持通过 外部 I2S 接口接收多通道

音频。该器件还具有可选的辅助音频接口。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

DS90UB949A-Q1 VQFN (64) 9.00mm x 9.00mm

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

录。

应应用用 图图

2

DS90UB949A-Q1

ZHCSJR7 –MAY 2019

www.ti.com.cn

Copyright © 2019, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 7

6.1 Absolute Maximum Ratings ..................................... 7

6.2 ESD Ratings ............................................................ 7

6.3 Recommended Operating Conditions....................... 7

6.4 Thermal Information.................................................. 8

6.5 DC Electrical Characteristics .................................... 8

6.6 AC Electrical Characteristics..................................... 9

6.7 DC and AC Serial Control Bus Characteristics....... 10

6.8 Recommended Timing for the Serial Control Bus .. 11

6.9 Timing Diagrams..................................................... 12

6.10 Typical Characteristics.......................................... 14

7 Detailed Description............................................ 15

7.1 Overview ................................................................. 15

7.2 Functional Block Diagram ....................................... 15

7.3 Feature Description................................................. 16

7.4 Device Functional Modes........................................ 30

7.5 Programming........................................................... 33

7.6 Register Maps......................................................... 36

8 Application and Implementation ........................ 67

8.1 Applications Information.......................................... 67

8.2 Typical Applications ................................................ 67

9 Power Supply Recommendations...................... 72

9.1 Power-Up Requirements and PDB Pin................... 72

10 Layout................................................................... 75

10.1 Layout Guidelines ................................................. 75

10.2 Layout Example .................................................... 75

11 器器件件和和文文档档支支持持 ..................................................... 76

11.1 文档支持 ............................................................... 76

11.2 接收文档更新通知 ................................................. 76

11.3 社区资源................................................................ 76

11.4 商标 ....................................................................... 76

11.5 静电放电警告......................................................... 76

11.6 Glossary................................................................ 76

12 机机械械、、封封装装和和可可订订购购信信息息....................................... 76

4 修修订订历历史史记记录录

注:之前版本的页码可能与当前版本有所不同。

日日期期 修修订订版版本本 说说明明

2019 年 5 月 * 初始发行版

VDD18

VDDIO

SDIN / GPIO0

RES0

IN_D0-

VTERM

IN_D0+

VDDHA11

IN_D1-

IN_D1+

SCL

VDDHS11

VDD18

RES2

PDB

VDDA11

D_GPIO0 / MOSI

DOUT0-

DOUT0+

MCLK

VDDS11

DOUT1-

DOUT1+

IN_D2-

VDDHA11

CEC

IN_D2+

VDD18

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

VDDHA11

I2S_DC / GPIO2

I2S_DD / GPIO3

VDDHA11

LFT

MODE

_SEL0

IDx

RX_5V

IN_CLK-

IN_CLK+

VDDL11

X1

REM_INTB

SCLK / I2CSEL

VDDL11

RES1

VDDHS11

DDC_SDA

NC1

DDC_SCL

NC0

SDA

INTB

D_GPIO3 / SS

D_GPIO2 / SPLK

I2S_WC / GPIO7_REG

I2S_DB / GPIO5_REG

I2S_CLK / GPIO8_REG

I2S_DA / GPIO6_REG

D_GPIO1 / MISO

MODE_SEL1

NC2

HPD

SWC / GPIO1

DS90UB949A-Q1

DAP = GND

VDDP11

VDDIO

64 VQFN

Top View

3

DS90UB949A-Q1

www.ti.com.cn

ZHCSJR7 –MAY 2019

Copyright © 2019, Texas Instruments Incorporated

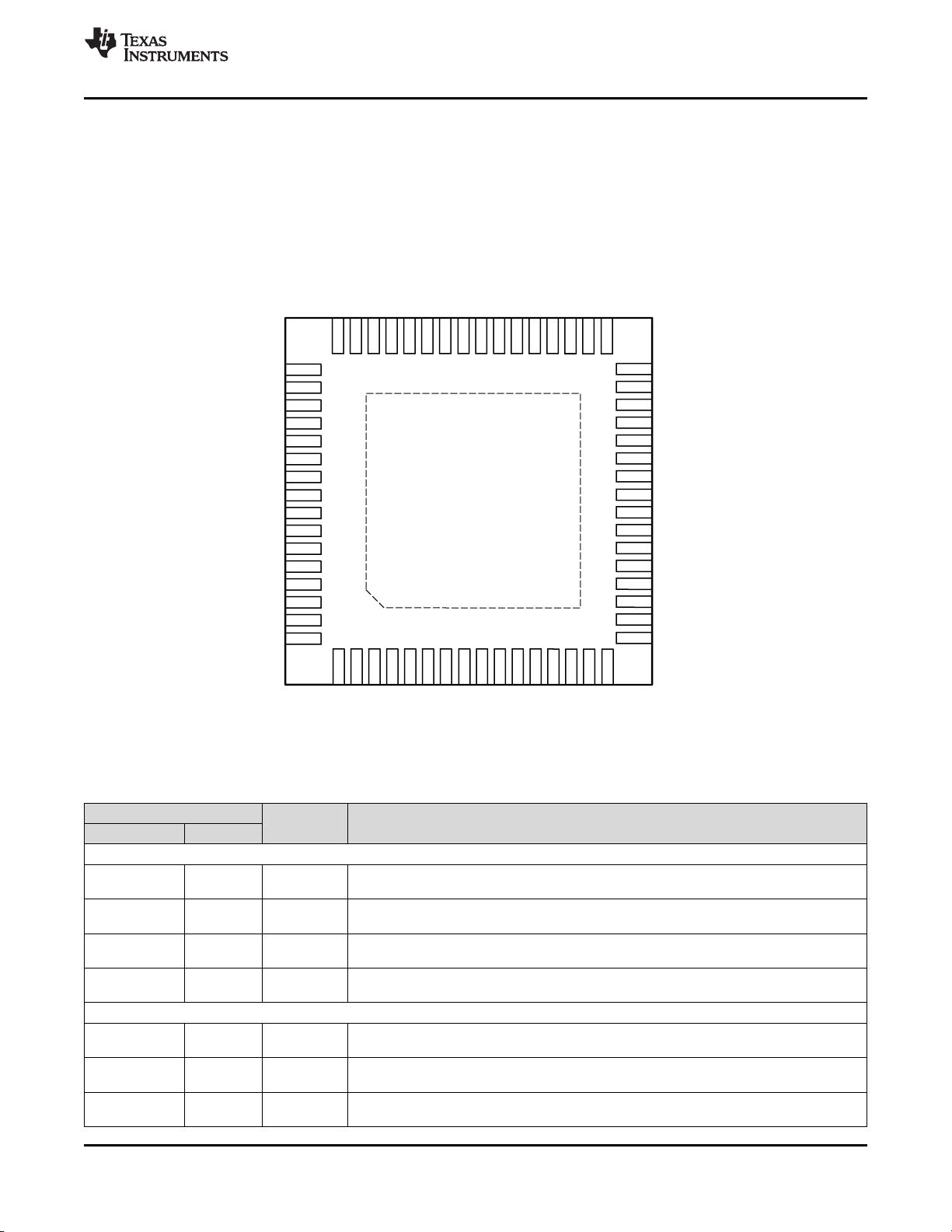

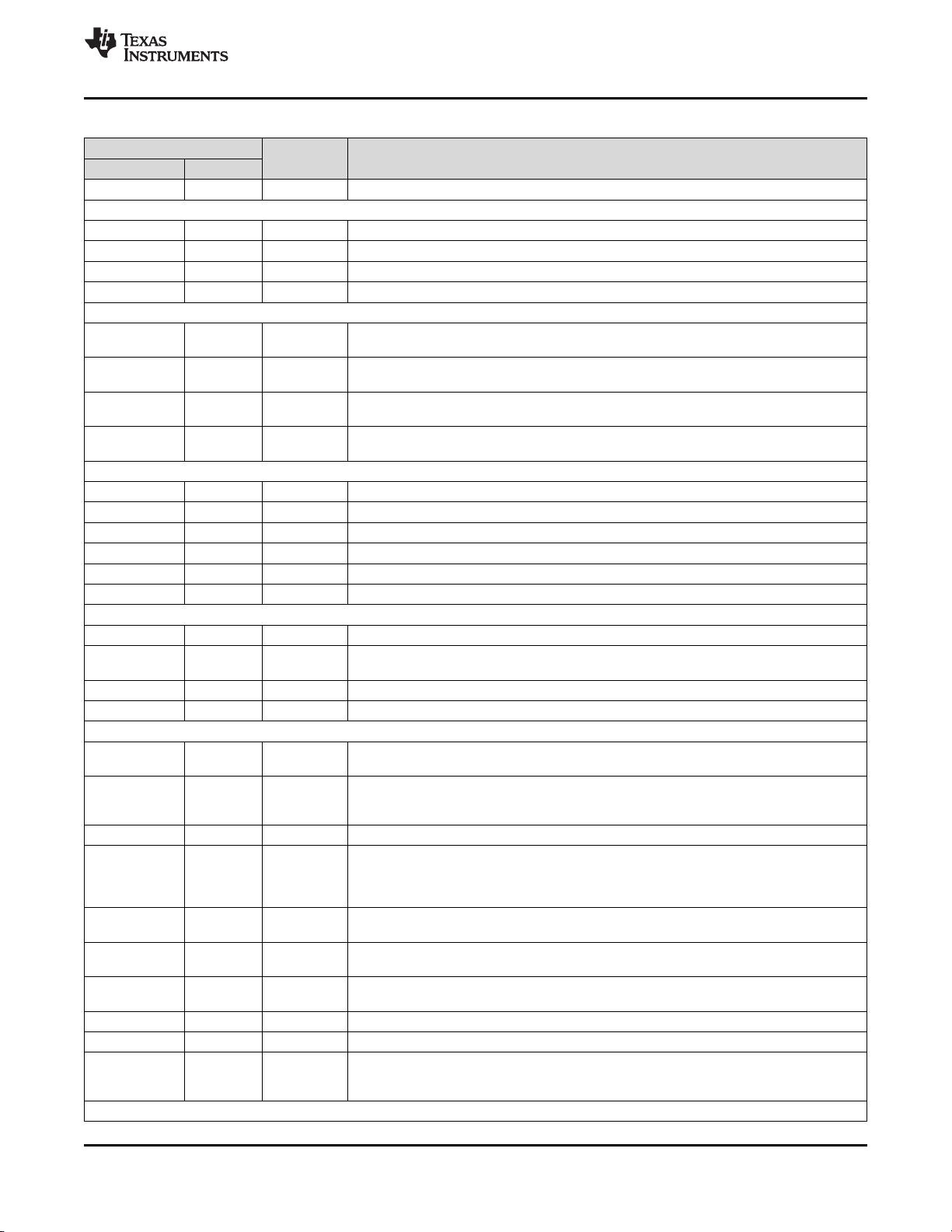

5 Pin Configuration and Functions

RGC Package

64-Pin VQFN

Top View

Pin Functions

PIN

I/O, TYPE DESCRIPTION

NAME NO.

HDMI TMDS INPUT

IN_CLK–

IN_CLK+

49

50

I, TMDS TMDS Clock Differential Input

IN_D0–

IN_D0+

55

56

I, TMDS TMDS Data Channel 0 Differential Input

IN_D1–

IN_D1+

59

60

I, TMDS TMDS Data Channel 1 Differential Input

IN_D2–

IN_D2+

62

63

I, TMDS TMDS Data Channel 2 Differential Input

OTHER HDMI

CEC 1

IO, Open-

Drain

Consumer Electronic Control Channel Input/Output Interface.

Pullup with a 27-kΩ resistor to 3.3 V

DDC_SDA 44

IO, Open-

Drain

DDC Slave Serial Data

Pull up to RX_5V with a 47-kΩ resistor

DDC_SCL 45 I, Open-Drain

DDC Slave Serial Clock

Pull up to RX_5V with a 47-kΩ resistor

4

DS90UB949A-Q1

ZHCSJR7 –MAY 2019

www.ti.com.cn

Copyright © 2019, Texas Instruments Incorporated

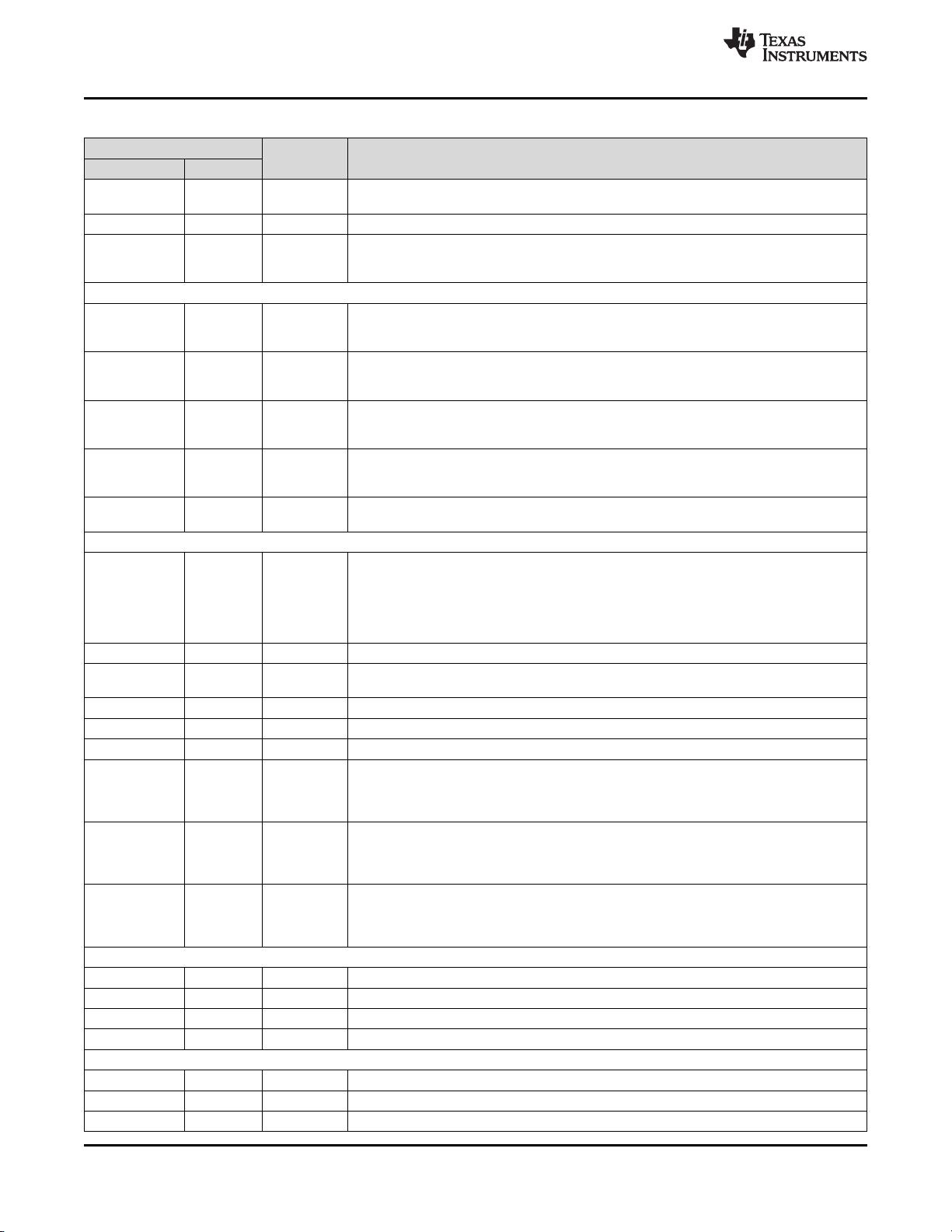

Pin Functions (continued)

PIN

I/O, TYPE DESCRIPTION

NAME NO.

HPD 42

O, Open-

Drain

Hot Plug Detect Output. Pull up to RX_5V with a 1-kΩ resistor

RX_5V 43 I HDMI 5-V Detect Input

X1 39 I, LVCMOS

Optional Oscillator Input: This pin is the optional reference clock for CEC. It must be

connected to a 25 MHz 0.1% (1000ppm), 45-55% duty cycle clock source at CMOS-level

1.8 V. Leave it open if unused.

FPD-LINK III SERIAL

DOUT0– 26 O

FPD-Link III Inverting Output 0

The output must be AC-coupled with a 0.1-μF capacitor for interfacing with DS90Ux92x-Q1

deserializers and 0.1-μF or 33-nF capacitor for 94x deserializers

DOUT0+ 27 O

FPD-Link III True Output 0

The output must be AC-coupled with a 0.1-µF capacitor for interfacing with DS90Ux92x-Q1

deserializers and 0.1-μF or 33-nF capacitor for 94x deserializers

DOUT1– 22 O

FPD-Link III Inverting Output 1

The output must be AC-coupled with a 0.1-µF capacitor for interfacing with DS90Ux92x-Q1

deserializers and 0.1-μF or 33-nF capacitor for 94x deserializers

DOUT1+ 23 O

FPD-Link III True Output 1

The output must be AC-coupled with a 0.1-µF capacitor for interfacing with DS90Ux92x-Q1

deserializers and 0.1-μF or 33-nF capacitor for 94x deserializers

LFT 20 Analog

FPD-Link III Loop Filter

Connect with a 10-nF capacitor to GND.

CONTROL

I2CSEL 6 I, LVCMOS

I2C Voltage Level Strap Option

Tie to V

DDIO

with a 10-kΩ resistor for 1.8-V I2C operation.

Leave floating for 3.3-V I2C operation.

This pin is read as an input at power up.

Issuing either of the digital resets via register 0x01 will cause the I2C_VSEL value to be

reset to 3.3-V operation.

IDx 19 Analog I2C Serial Control Bus Device ID Address Select

INTB 13

O, Open-

Drain

Open-Drain. Remote interrupt. Active LOW.

Pull up to VDDIO with a 4.7-kΩ resistor.

MODE_SEL0 18 Analog Mode Select 0. See 表 6.

MODE_SEL1 32 Analog Mode Select 1. See 表 6.

PDB 31 I, LVCMOS Power-Down Mode Input Pin

REM_INTB 40

O, Open-

Drain

Remote interrupt. Mirrors status of INTB_IN from the deserializer.

Note: External pullup to 1.8 V required. Recommended pullup: 4.7 kΩ.

INTB = H, Normal Operation

INTB = L, Interrupt Request

SCL 15

IO, Open-

Drain

I2C Clock Input / Output Interface

Open-drain. Must have an external pullup resistor to 1.8 V or 3.3 V. See I2CSEL pin. DO

NOT FLOAT.

Recommended pullup: 4.7 kΩ.

SDA 14

IO, Open-

Drain

I2C Data Input / Output Interface

Open-drain. Must have an external pullup to resistor to 1.8 V or 3.3 V. See I2CSEL pin. DO

NOT FLOAT.

Recommended pullup: 4.7 kΩ.

SPI PINS (DUAL LINK MODE ONLY)

MOSI 8 IO, LVCMOS SPI Master Out Slave In. Shared with D_GPIO0

MISO 10 IO, LVCMOS SPI Master In Slave Out. Shared with D_GPIO1

SPLK 11 IO, LVCMOS SPI Clock. Shared with D_GPIO2

SS 12 IO, LVCMOS SPI Slave Select. Shared with D_GPIO3

HIGH-SPEED (HS) BIDIRECTIONAL CONTROL CHANNEL GPIO PINS (DUAL LINK MODE ONLY)

D_GPIO0 8 IO, LVCMOS HS GPIO0. Shared with MOSI

D_GPIO1 10 IO, LVCMOS HS GPIO1. Shared with MISO

D_GPIO2 11 IO, LVCMOS HS GPIO2. Shared with SPLK

5

DS90UB949A-Q1

www.ti.com.cn

ZHCSJR7 –MAY 2019

Copyright © 2019, Texas Instruments Incorporated

Pin Functions (continued)

PIN

I/O, TYPE DESCRIPTION

NAME NO.

D_GPIO3 12 IO, LVCMOS HS GPIO3. Shared with SS

BIDIRECTIONAL CONTROL CHANNEL (BCC) GPIO PINS

GPIO0 4 IO, LVCMOS BCC GPIO0. Shared with SDIN

GPIO1 5 IO, LVCMOS BCC GPIO1. Shared with SWC

GPIO2 37 IO, LVCMOS BCC GPIO2. Shared with I2S_DC

GPIO3 38 IO, LVCMOS BCC GPIO3. Shared with I2S_DD

REGISTER-ONLY GPIO

GPIO5_REG 36 IO, LVCMOS

General-Purpose Input/Output 5

Local register control only. Shared with I2S_DB

GPIO6_REG 35 IO, LVCMOS

General-Purpose Input/Output 6

Local register control only. Shared with I2S_DA

GPIO7_REG 33 IO, LVCMOS

General-Purpose Input/Output 7

Local register control only. Shared with I2S_WC

GPIO8_REG 34 IO, LVCMOS

General-Purpose Input/Output 8

Local register control only. Shared with I2S_CLK

SLAVE MODE LOCAL I2S CHANNEL PINS

I2S_CLK 34 I, LVCMOS Slave Mode I2S Clock Input. Shared with GPIO8_REG

I2S_DA 35 I, LVCMOS Slave Mode I2S Data Input. Shared with GPIO6_REG

I2S_DB 36 I, LVCMOS Slave Mode I2S Data Input. Shared with GPIO5_REG

I2S_DC 37 I, LVCMOS Slave Mode I2S Data Input. Shared with GPIO2

I2S_DD 38 I, LVCMOS Slave Mode I2S Data Input. Shared with GPIO3

I2S_WC 33 I, LVCMOS Slave Mode I2S Word Clock Input. Shared with GPIO7_REG

AUXILIARY I2S CHANNEL PINS

MCLK 16 IO, LVCMOS Master Mode I2S System Clock Input/Output

SCLK 6 O, LVCMOS

Master Mode I2S Clock Ouput. Shared with I2CSEL. This pin is sampled following power-up

as I2CSEL, then it will switch to SCLK operation as an output.

SDIN 4 I, LVCMOS Master Mode I2S Data Input. Shared with GPIO0

SWC 5 O, LVCMOS Master Mode I2S Word Clock Ouput. Shared with GPIO1

POWER AND GROUND

GND

Thermal

Pad

GND Ground. Connect to Ground plane with at least 9 vias.

VDD18

24

51

64

Power 1.8-V (±5%) Analog supply. Refer to 图 25 or 图 26.

VDDA11 9 Power 1.1-V (±5%) Analog supply. Refer to 图 25 or 图 26.

VDDHA11

52

54

58

61

Power 1.1-V (±5%) TMDS supply. Refer to 图 25 or 图 26.

VDDHS11

21

28

Power 1.1-V (±5%) supply. Refer to 图 25 or 图 26.

VDDIO

3

46

Power 1.8-V (±5%) IO supply. Refer to 图 25 or 图 26.

VDDL11

7

41

Power 1.1-V (±5%) Digital supply. Refer to 图 25 or 图 26.

VDDP11 17 Power 1.1-V (±5%) PLL supply. Refer to 图 25 or 图 26.

VDDS11 25 Power 1.1-V (±5%) Serializer supply. Refer to 图 25 or 图 26.

VTERM 57 Power

3.3-V (±5%) Supply for DC-coupled internal termination OR

1.8-V (±5%) Supply for AC-coupled internal termination

Refer to 图 25 or 图 26.

OTHER

剩余83页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3102

- 资源: 5337

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功