没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS90UB935-Q1.pdf

温馨提示

试读

94页

FPD-Link串行器

资源推荐

资源详情

资源评论

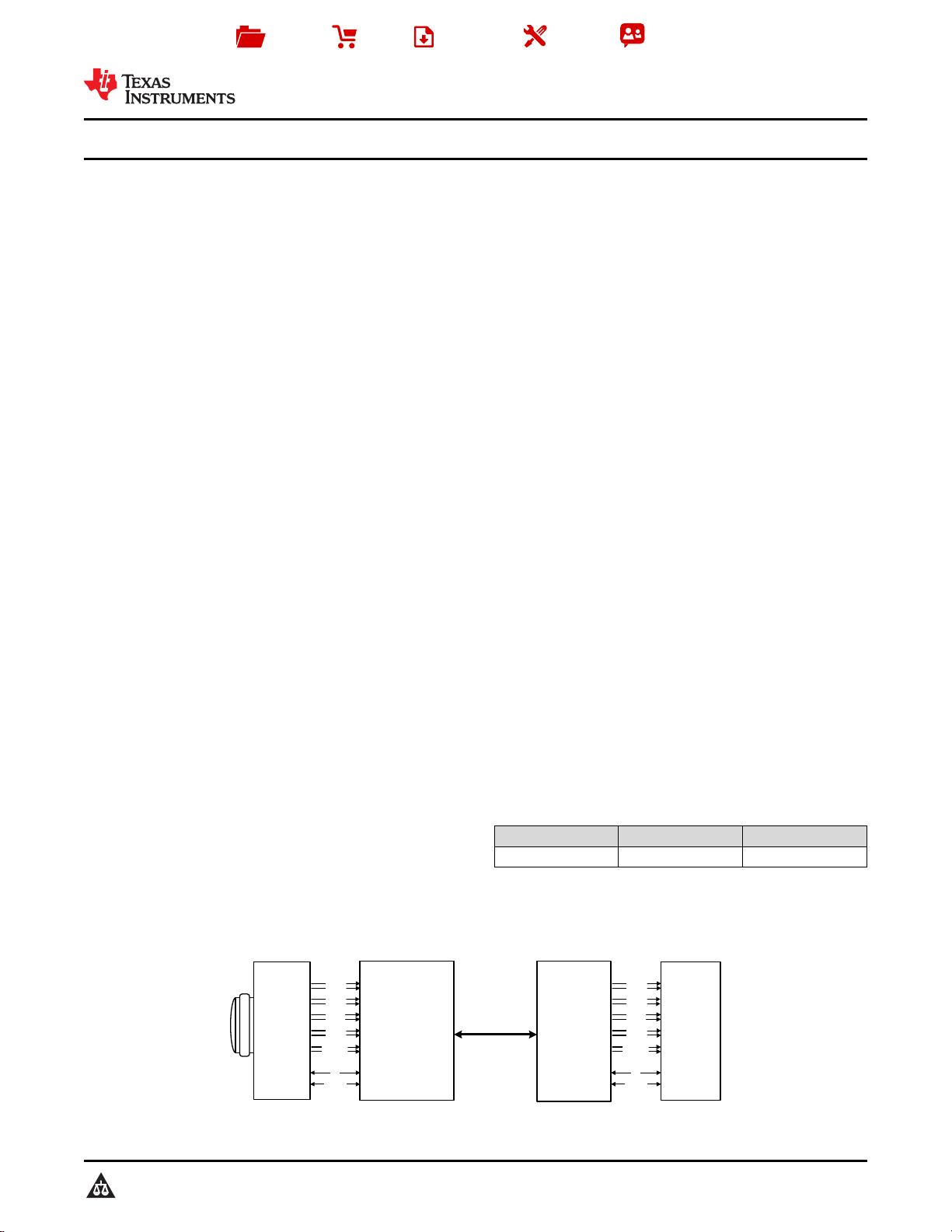

Image

Signal

Processor

(ISP)

Full HD

Image Sensor

FPD-Link III

(over Coax or STP)

DS90UB935-Q1

Serializer

DS90UB936-Q1

Deserializer

DOUT+/-

RIN+/-

MIPI CSI-2

D3P/N

CLKP/N

D2P/N

D1P/N

D0P/N

I2C

HS-GPIO

MIPI CSI-2

D3P/N

CLKP/N

D2P/N

D1P/N

D0P/N

I2C

HS-GPIO

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: SNLS605

DS90UB935-Q1

ZHCSIJ2 –JULY 2018

DS90UB935-Q1 具具有有 CSI-2 接接口口的的 FPD-Link III 3Gbps 串串行行器器

1

1 特特性性

1

• 符合面向汽车应用的 AEC-Q100 标准:

– 器件温度等级 2:环境工作温度范围为 –40°C

至 +105°C

• 符合 ISO 10605 和 IEC 61000-4-2 ESD 标准

• 同轴电缆供电 (PoC) 兼容收发器

• 3Gbps 级串行器支持高速传感器

• 符合 D-PHY v1.2 和 CSI-2 v1.3 标准的系统接口

– 高达 2.528Gbps 的 CSI-2 带宽

– 支持多达四个虚拟通道

• 精密多传感器时钟和同步

• 灵活的可编程输出时钟发生器

• 高级数据保护和诊断,包括 CRC 数据保护、传感

器数据完整性检查、I2C 写保护、电压和温度测

量、可编程警报器以及线路故障检测

• 支持单端同轴或屏蔽双绞线 (STP) 电缆

• 超低延迟双向 I2C 和 GPIO 控制通道支持从 ECU

侧进行 ISP 控制,

• 1.8V 单电源

• 低功耗(0.25W 典型值)

• 兼容 DS90UB936-Q1、DS90UB954-Q1、

DS90UB960-Q1、DS90UB934-Q1、

DS90UB914A-Q1 解串器

• 宽温度范围:–40°C 至 105°C

• 小型 5mm × 5mm VQFN 封装和 PoC 解决方案尺

寸,适合紧凑型摄像头模块设计

2 应应用用

• 汽车驾驶员辅助系统 (ADAS)

– 环视系统 (SVS)

– 摄像头监控系统 (CMS)

– 前视摄像头 (FC)

– 驾驶员监控系统 (DMS)

– 后视摄像头 (RVC)

– 汽车卫星雷达和激光雷达模块

– 飞行时间 (ToF) 传感器

• 安防和监控摄像头

• 工业和医疗成像

3 说说明明

DS90UB935-Q1 串行器是 TI FPD-Link III 器件系列的

一部分,旨在支持高速原始数据传感器,包括摄像头、

卫星雷达、激光雷达和飞行时间 (ToF) 传感器。该芯

片提供高速正向通道和超低延迟双向控制通道,并支持

通过单根同轴 (PoC) 或 STP 电缆进行供电。

DS90UB935-Q1 具有 高级数据保护和诊断 特性 ,可

支持 ADAS 和自主驾驶。在配套解串器的配合

下,DS90UB935-Q1 可提供精确的多摄像头传感器时

钟和传感器

同步。

DS90UB935-Q1 完全符合 AEC-Q100 标准,具有

–40°C 至 105°C 的宽温度范围。AECQ100 认证包括

HBM ESD 分类等级 3A 和 CDM ESD 分类等级 C6。

该串行器采用 5mm × 5mm 的小型 VQFN 封装,非常

适合空间受限型传感器 应用。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

DS90UB935-Q1 VQFN (32) 5.00mm × 5.00mm

(1) 要了解所有可用封装,请见产品说明书末尾的可订购产品附

录。

典典型型应应用用

2

DS90UB935-Q1

ZHCSIJ2 –JULY 2018

www.ti.com.cn

Copyright © 2018, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 5

6.1 Absolute Maximum Ratings ...................................... 5

6.2 ESD Ratings.............................................................. 5

6.3 Recommended Operating Conditions....................... 5

6.4 Thermal Information.................................................. 6

6.5 Electrical Characteristics........................................... 7

6.6 Recommended Timing for the Serial Control Bus .. 11

6.7 Timing Diagrams..................................................... 12

6.8 Typical Characteristics............................................ 12

7 Detailed Description............................................ 13

7.1 Overview ................................................................. 13

7.2 Functional Block Diagram ....................................... 13

7.3 Feature Description................................................. 14

7.4 Device Functional Modes........................................ 20

7.5 Programming........................................................... 24

7.6 Pattern Generation ................................................. 26

7.7 Register Maps ........................................................ 30

8 Application and Implementation ........................ 67

8.1 Application Information............................................ 67

8.2 Typical Applications ................................................ 70

9 Power Supply Recommendations...................... 73

9.1 Power-Up Sequencing ............................................ 73

9.2 Power Down (PDB)................................................. 74

10 Layout................................................................... 74

10.1 Layout Guidelines ................................................. 74

10.2 Layout Examples................................................... 75

11 器器件件和和文文档档支支持持 ..................................................... 78

11.1 器件支持................................................................ 78

11.2 文档支持 ............................................................... 78

11.3 接收文档更新通知 ................................................. 78

11.4 社区资源................................................................ 78

11.5 商标 ....................................................................... 78

11.6 静电放电警告......................................................... 78

11.7 术语表 ................................................................... 78

12 机机械械、、封封装装和和可可订订购购信信息息....................................... 79

4 修修订订历历史史记记录录

日日期期 修修订订版版本本 说说明明

2016 年 4 月 * 初始发行版。

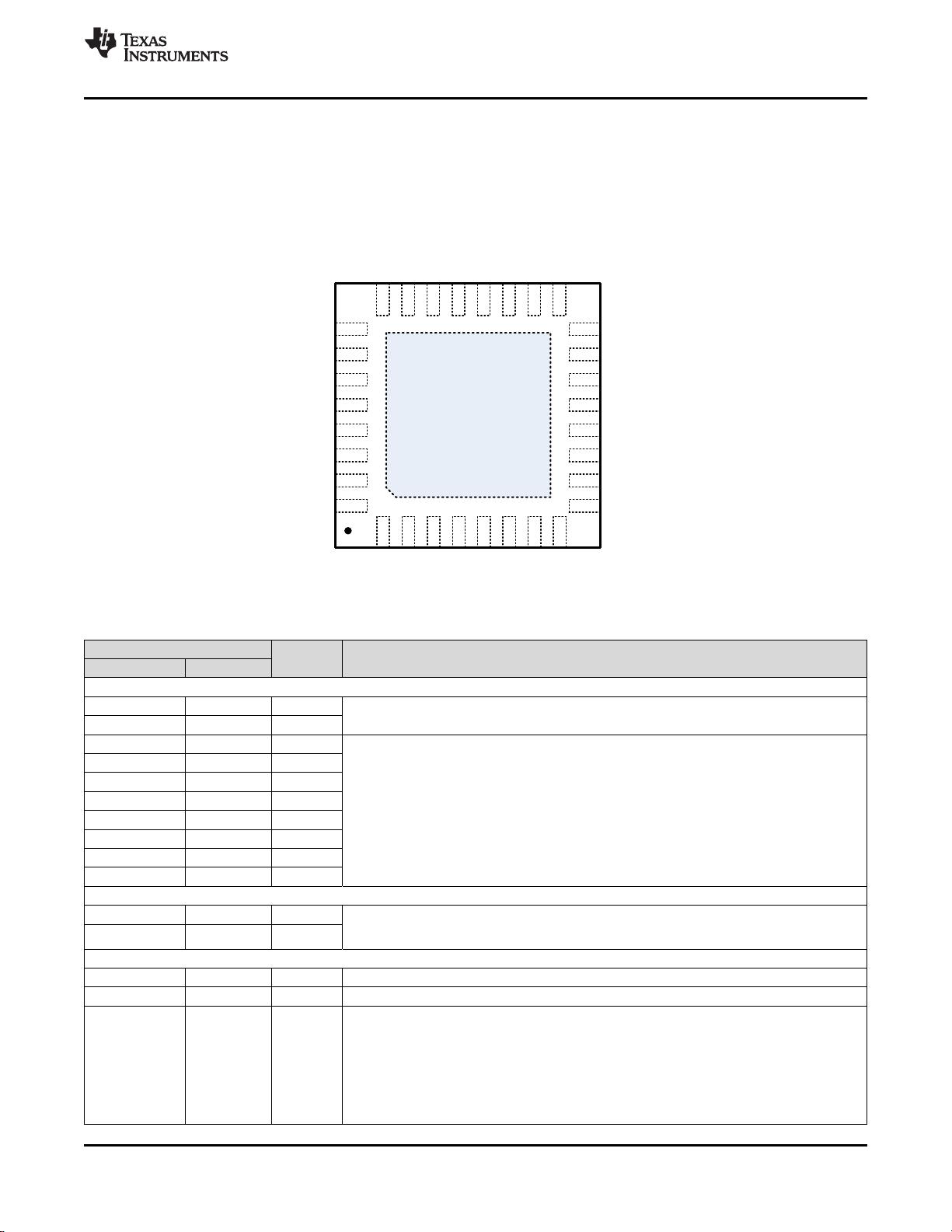

DS90UB935-Q1

32L QFN

(Top View)

32

31

30

29

28

27

26

25

CSI_D2P

CSI_D3N

CSI_D3P

GPIO_3

GPIO_2

VDDD_CAP

VDDD

DAP = GND

CSI_D2N

9

10

11

12

13

14

15

16

LPF1

VDDDRV

VDDPLL_CAP

VDDPLL

LPF2

DOUT-

VDDDRV_CAP

DOUT+

24

23

22

21

20

19

18

17

GPIO_1

CLK_OUT/IDX

RES1

I2C_SDA

GPIO_0

MODE

I2C_SCL

CLKIN

1

2

3

4

5

6

7

8

RES0

CSI_CLKN

CSI_D0P

CSI_D1N

CSI_D1P

CSI_D0N

CSI_CLKP

PDB

3

DS90UB935-Q1

www.ti.com.cn

ZHCSIJ2 –JULY 2018

Copyright © 2018, Texas Instruments Incorporated

5 Pin Configuration and Functions

RHB Package

32-Pin VQFN

Top View

Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

CSI INTERFACE

CSI_CLKP 5 I, DPHY

CSI-2 clock input pins. Connect to a CSI-2 clock source with matched 100-Ω (±5%) impedance

interconnects.

CSI_CLKN 6 I, DPHY

CSI_D0P 3 I, DPHY

CSI-2 data input pins. Connect to a CSI-2 data sources with matched 100-Ω (±5%) impedance

interconnects. If unused, these pins may be left floating.

CSI_D0N 4 I, DPHY

CSI_D1P 1 I, DPHY

CSI_D1N 2 I, DPHY

CSI_D2P 31 I, DPHY

CSI_D2N 32 I, DPHY

CSI_D3P 29 I, DPHY

CSI_D3N 30 I, DPHY

SERIAL CONTROL INTERFACE

I2C_SDA 23 OD I2C Data and Clock Pins. Typically pulled up by 470-Ω to 4.7-k Ω resistors to either 1.8-V or 3.3-V supply

rail depending on IDX setting. See I2C Interface Configuration for further details on the I2C

implementation of the DS90UB935-Q1.

I2C_SCL 24 OD

CONFIGURATION and CONTROL

RES0 7 I Reserved pin – Connect to GND

RES1 22 I Reserved pin – Do not connect (leave floating)

PDB 8 I, PD

Power-down inverted Input Pin. Internal 1-MΩ pulldown. Typically connected to processor GPIO with pull

down. When PDB input is brought HIGH, the device is enabled and internal register and state machines

are reset to default values. Asserting PDB signal low will power down the device and consume minimum

power. The default function of this pin is PDB = LOW; POWER DOWN. PDB should remain low until after

power supplies are applied and reach minimum required levels. See Power Down (PDB) for further details

on the function of PDB.

PDB INPUT IS NOT 3.3-V TOLERANT.

PDB = 1.8 V, device is enabled (normal operation)

PDB = 0, device is powered down.

4

DS90UB935-Q1

ZHCSIJ2 –JULY 2018

www.ti.com.cn

Copyright © 2018, Texas Instruments Incorporated

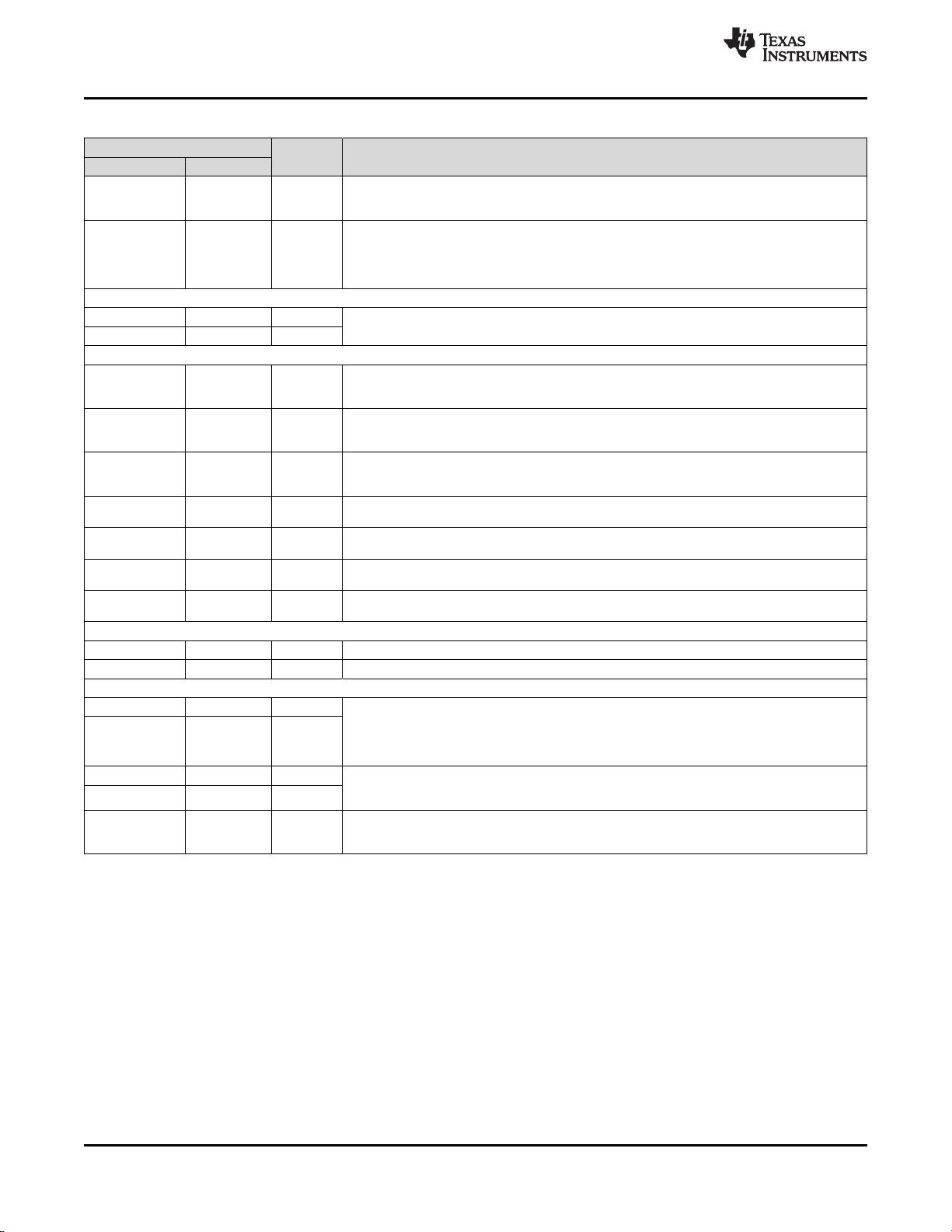

Pin Functions (continued)

PIN

I/O DESCRIPTION

NAME NO.

MODE 21 I, S

Mode select configuration input. Default operational mode will be strapped at start-up based on the MODE

input voltage when PDB transitions LOW to HIGH. Typically connected to voltage divider through external

pullup to VDD18 and pulldown to GND applying an appropriate bias voltage. See MODE for detail.

CLK_OUT/IDX 19 I/O, S

IDX pin sets the I2C pullup voltage and device address; connect to external pullup to VDD and pulldown

to GND to create a voltage divider. When PDB transitions LOW to HIGH, the strap input voltage is sensed

at the CLOCK_OUT/IDX pin to determine functionality and then converted to CLK_OUT. See I2C Interface

Configuration for detail. If CLK_OUT is used, the minimum resistance on the pin is 35 kΩ. If unused,

CLK_OUT/IDX may be tied to GND.

FPD-LINK III INTERFACE

DOUT- 13 I/O

FPD-Link III Input/Output pins. These pins must be AC-coupled. See 图 19 and 图 20 for typical

connection diagrams and 表 178 for recommended capacitor values.

DOUT+ 14 I/O

POWER AND GROUND

VDDD_CAP 26 D, P

A connection for internal analog regulator decoupling capacitor. Typically connected to 10-µF, 0.1-µF, and

0.01-µF capacitors to GND. Do not connect to an external supply rail. See Typical Application for more

details.

VDDDRV_CAP 15 D, P

A connection for internal analog regulator decoupling capacitor. Typically connected to 10-µF, 0.1-µF, and

0.01-µF capacitors to GND. Do not connect to an external supply rail. See Typical Application for more

details.

VDDPLL_CAP 10 D, P

A connection for internal analog regulator decoupling capacitor. Typically connected to 10-µF, 0.1-µF, and

0.01-µF capacitors to GND. Do not connect to an external supply rail. See Typical Application for more

details.

VDDD 25 P

1.8-V (±5%) Power Supply pin.

Typically connected to 1-µF and 0.01-µF capacitors to GND.

VDDDRV 16 P

1.8-V (±5%) Analog Power Supply pin.

Typically connected to 1-µF and 0.01-µF capacitors to GND.

VDDPLL 11 P

1.8-V (±5%) Analog Power Supply pin.

Typically connected to 1-µF and 0.01-µF capacitors to GND.

GND DAP G

DAP is the large metal contact at the bottom side, located at the center of the VQFN package. Connect to

the ground plane (GND).

LOOP FILTER

LPF1 9 P Loop Filter 1: Connect as described in Loop Filter Decoupling.

LPF2 12 P Loop Filter 2: Connect as described in Loop Filter Decoupling.

CLOCK INTERFACE and GPIO

GPIO_0 17 I/O, PD General-Purpose Input/Output pins. These pins can also be configured to sense the voltage at their

inputs. See Voltage and Temperature Sensing. At power-up these GPIO pins default to inputs with a 300

kΩ (typical) internal pulldown resistor. If unused, these pins may be left floating, however, it is

recommended to disable them by setting the GPIOx_INPUT_EN to 0. See GPIO Support for

programmability.

GPIO_1 18 I/O, PD

GPIO_2 27 I/O, PD General-Purpose Input/Output pins. At power-up these GPIO pins default to inputs with a 300 kΩ (typical)

internal pulldown resistor. If unused, these pins may be left floating, however, it is recommended to

disable them by setting the GPIOx_INPUT_EN to 0. See GPIO Support for programmability.

GPIO_3 28 I/O. PD

CLKIN 20 I

Reference Clock Input pin. If operating in Non Sync external clock mode, connect this pin to a local clock

source. If unused (other clocking modes), this pin may be left open. See 表 6 for more information on

clocking modes.

5

DS90UB935-Q1

www.ti.com.cn

ZHCSIJ2 –JULY 2018

Copyright © 2018, Texas Instruments Incorporated

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6 Specifications

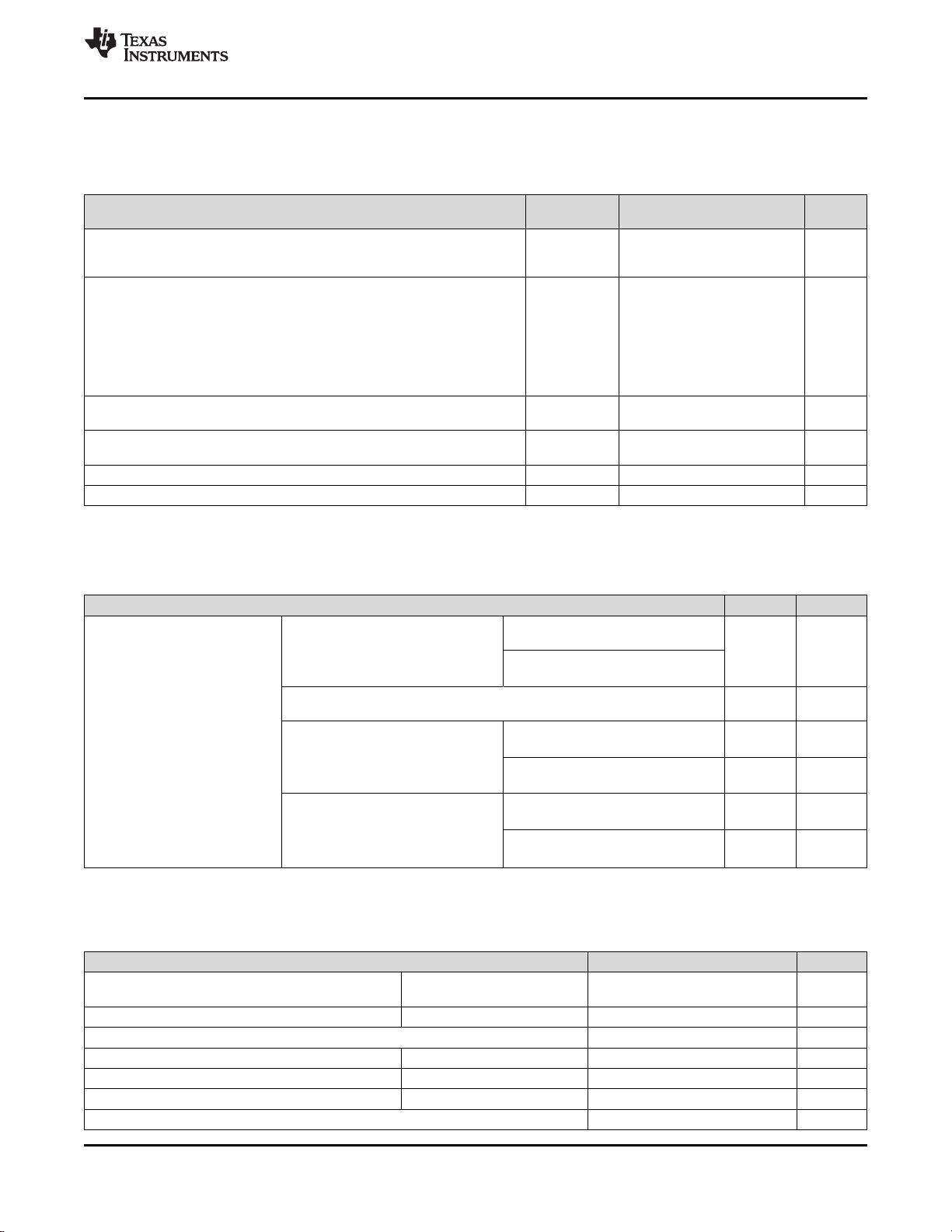

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)

PIN OR

FREQUENCY

MIN MAX UNIT

Supply voltage, VDD

VDDD,

VDDDRV,

VDDPLL

–0.3 2.16 V

Input voltage

GPIO[3:0],

PDB, CLKIN,

IDX, MODE,

CSI_CLKP/N,

CSI_D0P/N,

CSI_D1P/N,

CSI_D2P/N,

CSI_D3P/N

–0.3 V

DD

+ 0.3 V

FPD-Link III output voltage DOUT+,

DOUT-

–0.3 1.21 V

Open-drain voltage I2C_SDA,

I2C_SCL

–0.3 3.96 V

Junction temperature, T

J

150 °C

Storage termperature, T

stg

–65 150 °C

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic

discharge

Human body model (HBM) ESD

Classification Level 3A, per AEC

Q100-002

(1)

All pins except Media Dependent

Interface Pins

±4000 V

Media Dependent Interface

Pins

Charged-device model (CDM) ESD Classification Level C6, per AEC Q100-

011

±1500 V

IEC 61000-4-2

R

D

= 330 Ω, C

S

= 150 pF

Contact Discharge

(DOUT+ and DOUT-)

±8000 V

Air Discharge

(DOUT+ and DOUT-)

±18000 V

ISO 10605

R

D

= 330 Ω, C

S

= 150 pF and 330 pF

R

D

= 2 kΩ, C

S

= 150 pF and 330 pF

Contact Discharge

(DOUT+ and DOUT-)

±8000 V

Air Discharge

(DOUT+ and DOUT-)

±18000 V

6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

Supply voltage

VDD (VDDD, VDDDRV,

VDDPLL)

1.71 1.8 1.89 V

Open-drain voltage I2C_SDA, I2C_SCL = V

(I2C)

1.71 3.6 V

Operating free-air temperature (T

A

) –40 25 105 °C

Mipi data rate (per CSI-2 lane) 80 832 Mbps

Mipi combined data rate 2.5 Gbps

Reference clock input frequency 25 104 MHz

Local I

2

C frequency (f

I2C

) 1 MHz

剩余93页未读,继续阅读

资源评论

qq_335607272023-02-02#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

qq_335607272023-02-02#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 m0_745259962023-02-02#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

m0_745259962023-02-02#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

不觉明了

- 粉丝: 3100

- 资源: 5313

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功