没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS92LV2411.pdf

需积分: 8 0 下载量 171 浏览量

2023-02-08

23:01:50

上传

评论 4

收藏 1.69MB PDF 举报

温馨提示

试读

58页

LVDS串行器

资源推荐

资源详情

资源评论

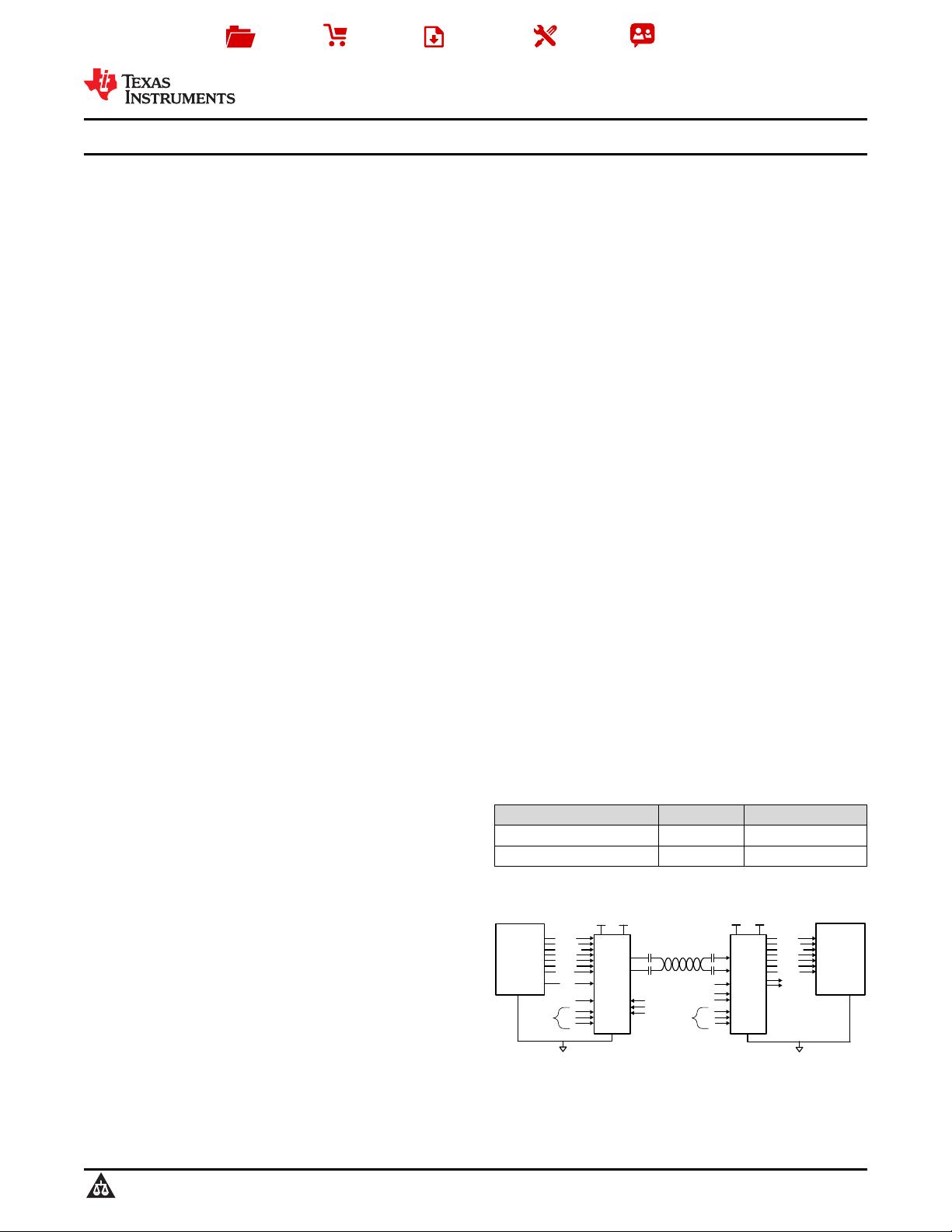

DI[7:0]

CI2

CI3

CLKIN

PDB

Serializer Deserializer

CI1

Graphic

Processor

Channel Link II

1 Pair / AC Coupled

DS92LV2411 DS92LV2412

100 ohm STP Cable

PASS

V

DDIO

PDB

SCL

SDA

RFB

VODSEL

DeEmph

BISTEN

BISTEN

LOCK

ID[x]

DAP DAP

CMF

0.1 PF 0.1 PF

SCL

SDA

ID[x]

STRAP pins

not shown

RIN+

RIN-

DOUT+

DOUT-

Optional Optional

(1.8V or 3.3V)(1.8V or 3.3V)

1.8V

1.8V

V

DDIO

V

DDn

V

DDn

ASIC/FPGA

OR

24-bit RGB

Display

ASIC/FPGA

OR

DI[15:8]

DI[23:16]

DO[7:0]

CO2

CO3

CLKOUT

CO1

DO[15:8]

DO[23:16]

Video

Imager

OR

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

DS92LV2411

,

DS92LV2412

SNLS302E –MAY 2010–REVISED FEBRUARY 2015

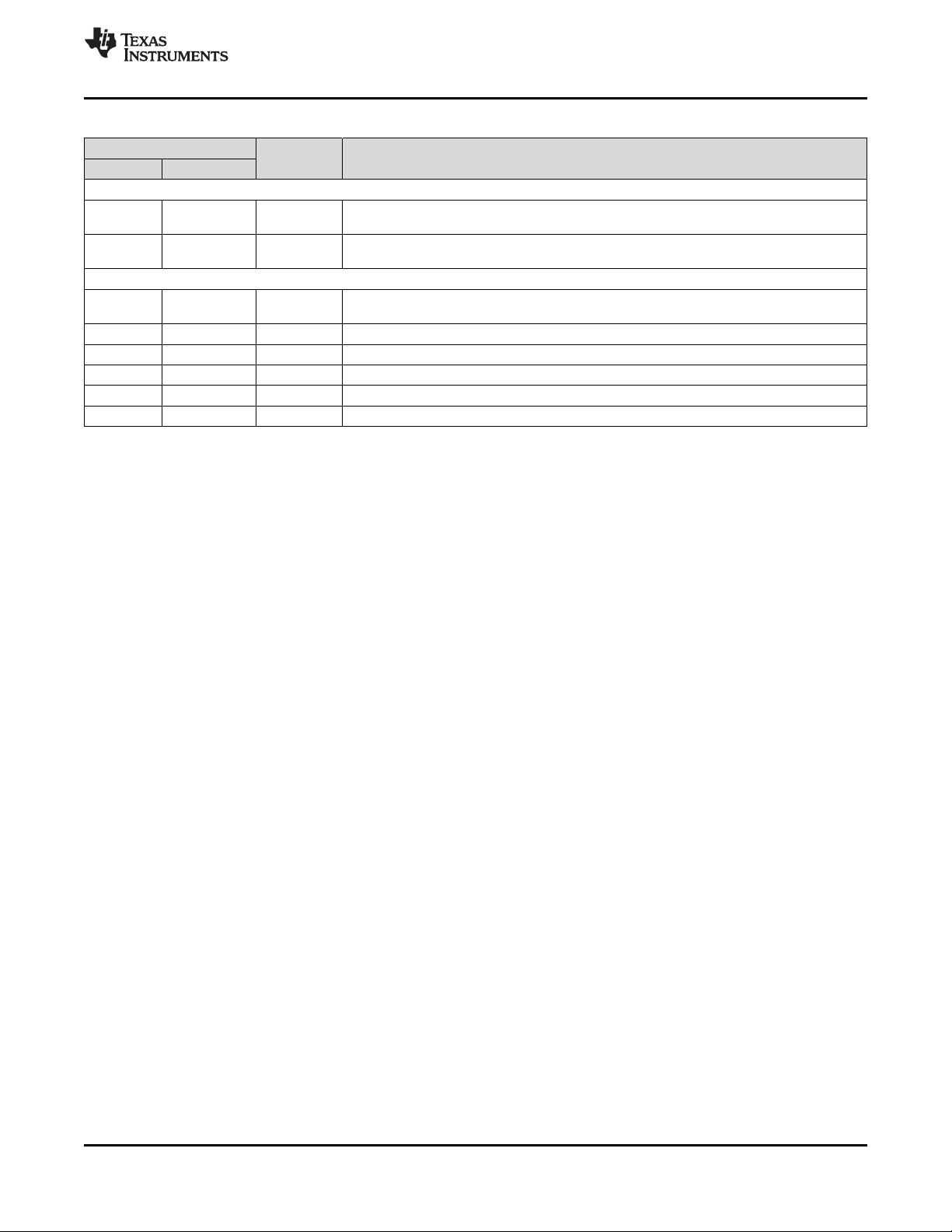

DS92LV241x 5 to 50 MHz 24-Bit Channel Link II Serializer And Deserializer

1 Features 3 Description

The DS92LV2411 (Serializer) and DS92LV2412

1

• 24-Bit Data, 3–Bit Control, 5 to 50 MHz Clock

(Deserializer) chipset translates a parallel 24–bit

• Application Payloads up to 1.2 Gbps

LVCMOS data interface into a single high-speed CML

• AC Coupled Interconnects: STP up to 10 m or

serial interface with embedded clock information. This

Coax 20+ m

single serial stream eliminates skew issues between

clock and data, reduces connector size and

• 1.8 V or 3.3 V Compatible LVCMOS I/O Interface

interconnect cost for transferring a 24-bit, or less, bus

• Integrated Terminations on Ser and Des

over FR-4 printed circuit board backplanes,

• AT-SPEED BIST Mode and Reporting Pin

differential or coax cables.

• Configurable by Pins or I2C Compatible Serial

In addition to the 24-bit data bus interface, the

Control Bus

DS92LV2411/12 also features a 3-bit control bus for

• Power Down Mode Minimizes Power Dissipation

slow speed signals. This allows implementing video

and display applications with up to 24–bits per pixel

• >8 kV HBM ESD Rating

(RGB888).

• SERIALIZER — DS92LV2411

Programmable transmit de-emphasis, receive

– Supports Spread Spectrum Clocking (SSC) on

equalization, on-chip scrambling and DC balancing

Inputs

enables long distance transmission over lossy cables

– Data Scrambler for Reduced EMI

and backplanes. The DS92LV2412 automatically

locks to incoming data without an external reference

– DC-Balance Encoder for AC Coupling

clock or special sync patterns, providing easy “plug-

– Selectable Output V

OD

and Adjustable De-

and-go” or “hot plug” operation. EMI is minimized by

emphasis

the use of low voltage differential signaling, receiver

• DESERIALIZER — DS92LV2412

drive strength control, and spread spectrum clocking

capability.

– Random Data Lock; no Reference Clock

Required

The DS92LV2411/12 chipset is programmable though

– Adjustable Input Receiver Equalization

an I2C interface as well as through Pins. A built-in

AT-SPEED BIST feature validates link integrity and

– LOCK (Real Time Link Status) Reporting Pin

may be used for system diagnostics.

– Selectable Spread Spectrum Clock Generation

The DS92LV2411 is offered in a 48-Pin WQFN and

(SSCG) and Output Slew Rate Control (OS) to

the DS92LV2412 is offered in a 60-Pin WQFN

Reduce EMI

package. Both devices operate over the full industrial

temperature range of -40°C to +85°C.

2 Applications

• Embedded Video and Display

Device Information

• Medical Imaging

PART NUMBER PACKAGE BODY SIZE (NOM)

• Factory Automation

DS92LV2411 WQFN (48) 7.00 mm × 7.00 mm

DS92LV2412 WQFN (60) 9.00 mm × 9.00 mm

• Office Automation — Printer, Scanner

• Security and Video Surveillance

4 Typical Application Schematic

• General Purpose Data Communication

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

DS92LV2411

,

DS92LV2412

SNLS302E –MAY 2010–REVISED FEBRUARY 2015

www.ti.com

Table of Contents

8.1 Overview ................................................................. 22

1 Features.................................................................. 1

8.2 Functional Block Diagrams ..................................... 22

2 Applications ........................................................... 1

8.3 Feature Description................................................. 23

3 Description ............................................................. 1

8.4 Device Functional Modes........................................ 34

4 Typical Application Schematic............................. 1

8.5 Programming........................................................... 34

5 Revision History..................................................... 2

8.6 Register Maps......................................................... 37

6 Pin Configuration and Functions......................... 3

9 Applications and Implementation ...................... 40

7 Specifications....................................................... 10

9.1 Application Information............................................ 40

7.1 Absolute Maximum Ratings .................................... 10

9.2 Typical Applications ................................................ 40

7.2 ESD Ratings............................................................ 10

10 Power Supply Recommendations ..................... 44

7.3 Recommended Operating Conditions..................... 10

11 Layout................................................................... 44

7.4 Thermal Information................................................ 11

11.1 Layout Guidelines ................................................. 44

7.5 Serializer DC Electrical Characteristics .................. 11

11.2 Layout Example .................................................... 44

7.6 Deserializer DC Electrical Characteristics .............. 12

12 Device and Documentation Support ................. 47

7.7 DC and AC Serial Control Bus Characteristics....... 13

12.1 Related Links ........................................................ 47

7.8 Recommended Timing For The Serial Control Bus 14

12.2 Trademarks ........................................................... 47

7.9 Recommended Serializer Timing For CLKIN.......... 18

12.3 Electrostatic Discharge Caution............................ 47

7.10 Serializer Switching Characteristics...................... 19

12.4 Glossary ................................................................ 47

7.11 Deserializer Switching Characteristics.................. 20

13 Mechanical, Packaging, and Orderable

7.12 Typical Characteristics.......................................... 21

Information ........................................................... 47

8 Detailed Description............................................ 22

5 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision D (April 2014) to Revision E Page

• Changed "Terminal" terminology back to "Pin" ..................................................................................................................... 1

• Added statement about checkerboard pattern from deserializer data output when in BIST mode ..................................... 32

• Added note that BISTEN pin must be high and REG = 0 to use BIST mode. .................................................................... 32

• Changed deserializer Reg 0x02[6] definition to match correct OSS_SEL behavior ............................................................ 38

Changes from Revision C (April 2013) to Revision D Page

• Added Handling Ratings and Thermal Characteristics and updated datasheet to new layout. ............................................ 1

• Changed Serializer Supply current power down test condition from V

DDIO

from 13.6V to 3.6V .......................................... 12

• Added DC to "Deserializer Electrical Characteristics".......................................................................................................... 12

• Changed typical value to 36mA instead of 37mA ............................................................................................................... 12

• Changed Test condition of V

OUT

for determining I

OZ

........................................................................................................... 12

• Added max value for V

IL

when using 1.8V I/O LVCMOS .................................................................................................... 12

• Changed IOL from 3mA to 1.25mA ..................................................................................................................................... 13

• Changed parentheses location of UI equation for clarification ............................................................................................ 20

• Added characteristic graphics for serializer CML driver output and deserializer LVCMOS clock output ............................ 21

• Added applications graphics of the serializer output with and without de-emphasis .......................................................... 43

• Added layout example and stencil diagram graphics........................................................................................................... 44

Changes from Revision B (April 2013) to Revision C Page

• Changed layout of National Data Sheet to TI format ........................................................................................................... 43

2 Submit Documentation Feedback Copyright © 2010–2015, Texas Instruments Incorporated

Product Folder Links: DS92LV2411 DS92LV2412

37

38

39

40

41

42

43

44

45

46

47

48

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

36

35

34

33

32

31

30

29

28

27

26

25

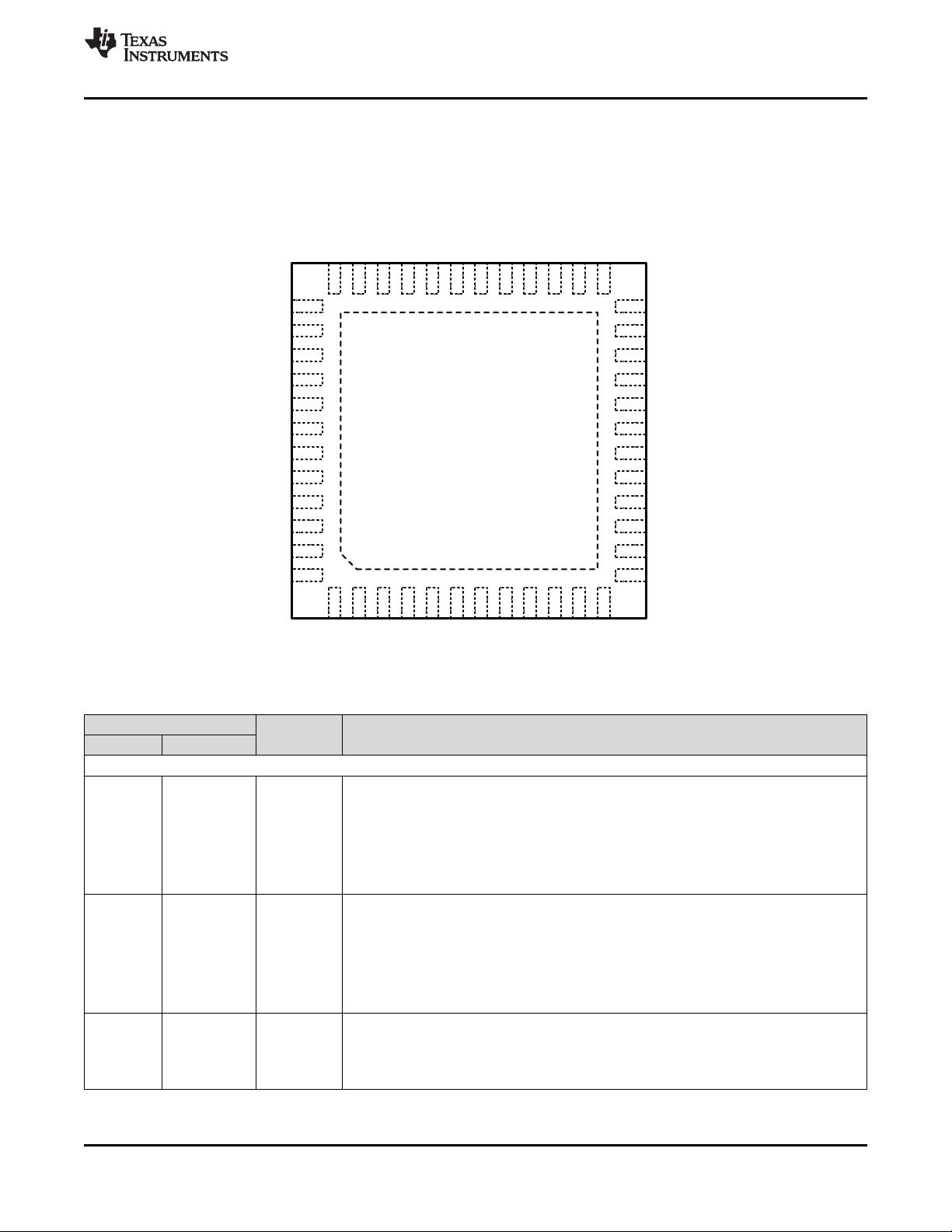

DS92LV2411

TOP VIEW

DAP = GND

DI21

DI20

DI18

DI17

DI14

DI13

DI11

DI10

CONFIG[1]

VDDP

RES1

VDDHS

DOUT+

PDB

De-Emph

VODSEL

DI12

DI15

DI16

DI19 RES0

RES2

DOUT-

VDDTX

DI22

CI2

CLKIN

CONFIG[0]

DI23

DI8

DI7

DI6

DI5

BISTEN

VDDIO

DI4

DI3

DI2

DI1

DI9

VDDL

SCL

RFB

DI0

SDA

CI3

CI1

ID[x]

DS92LV2411

,

DS92LV2412

www.ti.com

SNLS302E –MAY 2010–REVISED FEBRUARY 2015

6 Pin Configuration and Functions

48-Pin WQFN

Package RHS

Top View

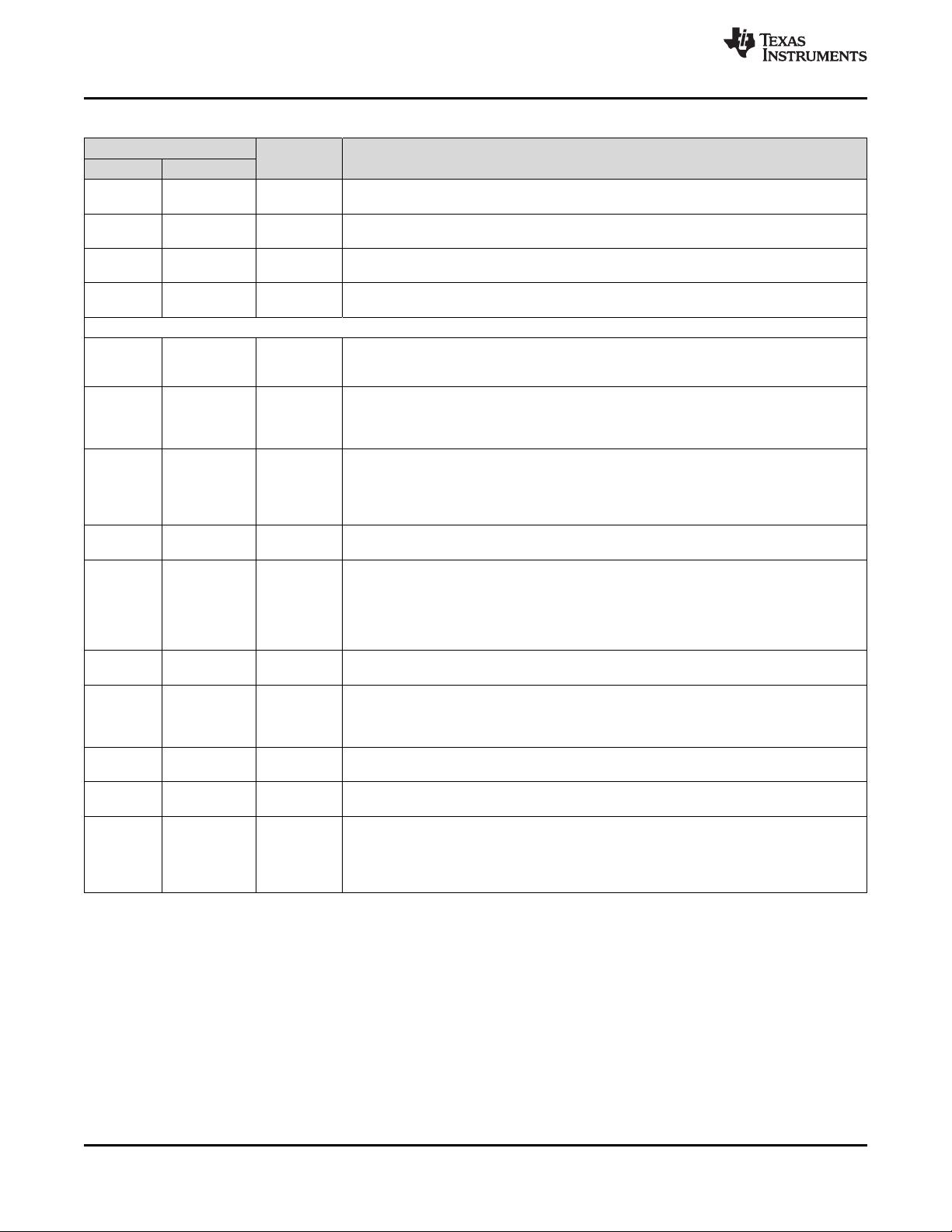

Pin Functions, DS92LV2411 Serializer

(1)

PIN

TYPE DESCRIPTION

NAME NO.

LVCMOS PARALLEL INTERFACE

CI1 5 I, LVCMOS Control Signal Input

w/ pull-down For Display/Video Application:

CI1 = Data Enable Input

Control signal pulse width must be 3 clocks or longer to be transmitted when the Control

Signal Filter is enabled (CONFIG[1:0] = 01). There is no restriction on the minimum transition

pulse when the Control Signal Filter is disabled (CONFIG[1:0] = 00).

The signal is limited to 2 transitions per 130 clocks regardless of the Control Signal Filter

setting.

CI2 3 I, LVCMOS Control Signal Input

w/ pull-down For Display/Video Application:

CI2 = Horizontal Sync Input

Control signal pulse width must be 3 clocks or longer to be transmitted when the Control

Signal Filter is enabled (CONFIG[1:0] = 01). There is no restriction on the minimum transition

pulse when the Control Signal Filter is disabled (CONFIG[1:0] = 00).

The signal is limited to 2 transitions per 130 clocks regardless of the Control Signal Filter

setting.

CI3 4 I, LVCMOS Control Signal Input

w/ pull-down For Display/Video Application:

CI3 = Vertical Sync Input

CI3 is limited to 1 transition per 130 clock cycles. Thus, the minimum pulse width allowed is

130 clock cycle wide.

(1) NOTE: 1 = HIGH, 0 = LOW

The VDD (V

DDn

and V

DDIO

) supply ramp should be faster than 1.5 ms with a monotonic rise. If slower then 1.5 ms then a capacitor on

the PDB Pin is needed to ensure PDB arrives after all the VDD have settled to the recommended operating voltage.

Copyright © 2010–2015, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: DS92LV2411 DS92LV2412

DS92LV2411

,

DS92LV2412

SNLS302E –MAY 2010–REVISED FEBRUARY 2015

www.ti.com

Pin Functions, DS92LV2411 Serializer

(1)

(continued)

PIN

TYPE DESCRIPTION

NAME NO.

CLKIN 10 I, LVCMOS Clock Input

w/ pull-down Latch/data strobe edge set by RFB Pin.

DI[7:0] 34, 33, 32, 29, I, LVCMOS Parallel Interface Data Input Pins

28, 27, 26, 25 w/ pull-down For 8–bit RED Display: DI7 = R7 – MSB, DI0 = R0 – LSB.

DI[15:8] 42, 41, 40, 39, I, LVCMOS Parallel Interface Data Input Pins

38, 37, 36, 35 w/ pull-down For 8–bit GREEN Display: DI15 = G7 – MSB, DI8 = G0 – LSB.

DI[23:16] 2, 1, 48, 47, I, LVCMOS Parallel Interface Data Input Pins

46, 45, 44, 43 w/ pull-down For 8–bit BLUE Display: DI23 = B7 – MSB, DI16 = B0 – LSB.

CONTROL AND CONFIGURATION

BISTEN 31 I, LVCMOS BIST Mode — Optional

w/ pull-down BISTEN = 0, BIST is disabled (normal operation)

BISTEN = 1, BIST is enabled

CONFIG[1: 13, 12 I, LVCMOS 00: Control Signal Filter DISABLED. Interfaces with DS92LV2412 or DS92LV0412

0] w/ pull-down 01: Control Signal Filter ENABLED. Interfaces with DS92LV2412 or DS92LV0412

10: Reverse compatibility mode to interface with the DS90UR124 or DS99R124Q

11: Reverse compatibility mode to interface with the DS90C124

De-Emph 23 I, Analog De-Emphasis Control

w/ pull-up De-Emph = open (float) - disabled

To enable De-emphasis, tie a resistor from this Pin to GND or control via register.

See Table 2.

This can also be controlled by I2C register access.

ID[x] 6 I, Analog I2C Serial Control Bus Device ID Address Select — Optional

Resistor to Ground and 10 kΩ pull-up to 1.8V rail. See Table 11.

PDB 21 I, LVCMOS Power-down Mode Input

w/ pull-down PDB = 1, Ser is enabled (normal operation).

Refer to ”Power Up Requirements and PDB Pin” in the Applications Information Section.

PDB = 0, Ser is powered down

When the Ser is in the power-down state, the driver outputs (DOUT+/-) are both logic high,

the PLL is shutdown, IDD is minimized. Control Registers are RESET.

RES[2:0] 18, 16, 15 I, LVCMOS Reserved - tie LOW

w/ pull-down

RFB 11 I, LVCMOS Clock Input Latch/Data Strobe Edge Select

w/ pull-down RFB = 1, parallel interface data and control signals are latched on the rising clock edge.

RFB = 0, parallel interface data and control signals are latched on the falling clock edge.

This can also be controlled by I2C register access.

SCL 8 I, LVCMOS I2C Serial Control Bus Clock Input - Optional

Open Drain SCL requires an external pull-up resistor to 3.3V.

SDA 9 I/O, LVCMOS I2C Serial Control Bus Data Input / Output - Optional

Open Drain SDA requires an external pull-up resistor 3.3V.

VODSEL 24 I, LVCMOS Differential Driver Output Voltage Select

w/ pull-down VODSEL = 1, CML VOD is ±420 mV, 840 mVp-p (typ) — long cable / De-Emph applications

VODSEL = 0, CML VOD is ±280 mV, 560 mVp-p (typ) — short cable (no De-emph), low

power mode.

This is can also be control by I2C register.

4 Submit Documentation Feedback Copyright © 2010–2015, Texas Instruments Incorporated

Product Folder Links: DS92LV2411 DS92LV2412

DS92LV2411

,

DS92LV2412

www.ti.com

SNLS302E –MAY 2010–REVISED FEBRUARY 2015

Pin Functions, DS92LV2411 Serializer

(1)

(continued)

PIN

TYPE DESCRIPTION

NAME NO.

CHANNEL-LINK II — CML SERIAL INTERFACE

DOUT- 19 O, CML Inverting Output.

The output must be AC Coupled with a 0.1 µF capacitor.

DOUT+ 20 O, CML Non–Inverting Output.

The output must be AC Coupled with a 0.1 µF capacitor.

POWER AND GROUND

GND DAP Ground DAP is the large metal contact at the bottom side, located at the center of the WQFN

package. Connect to the ground plane (GND) with at least 9 vias.

VDDHS 17 Power TX High Speed Logic Power, 1.8 V ±5%

VDDIO 30 Power LVCMOS I/O Power, 1.8 V ±5% OR 3.3 V ±10%

VDDL 7 Power Logic Power, 1.8 V ±5%

VDDP 14 Power PLL Power, 1.8 V ±5%

VDDTX 22 Power Output Driver Power, 1.8 V ±5%

Copyright © 2010–2015, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Links: DS92LV2411 DS92LV2412

剩余57页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3175

- 资源: 5443

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功