TI-DS92LV0412.pdf

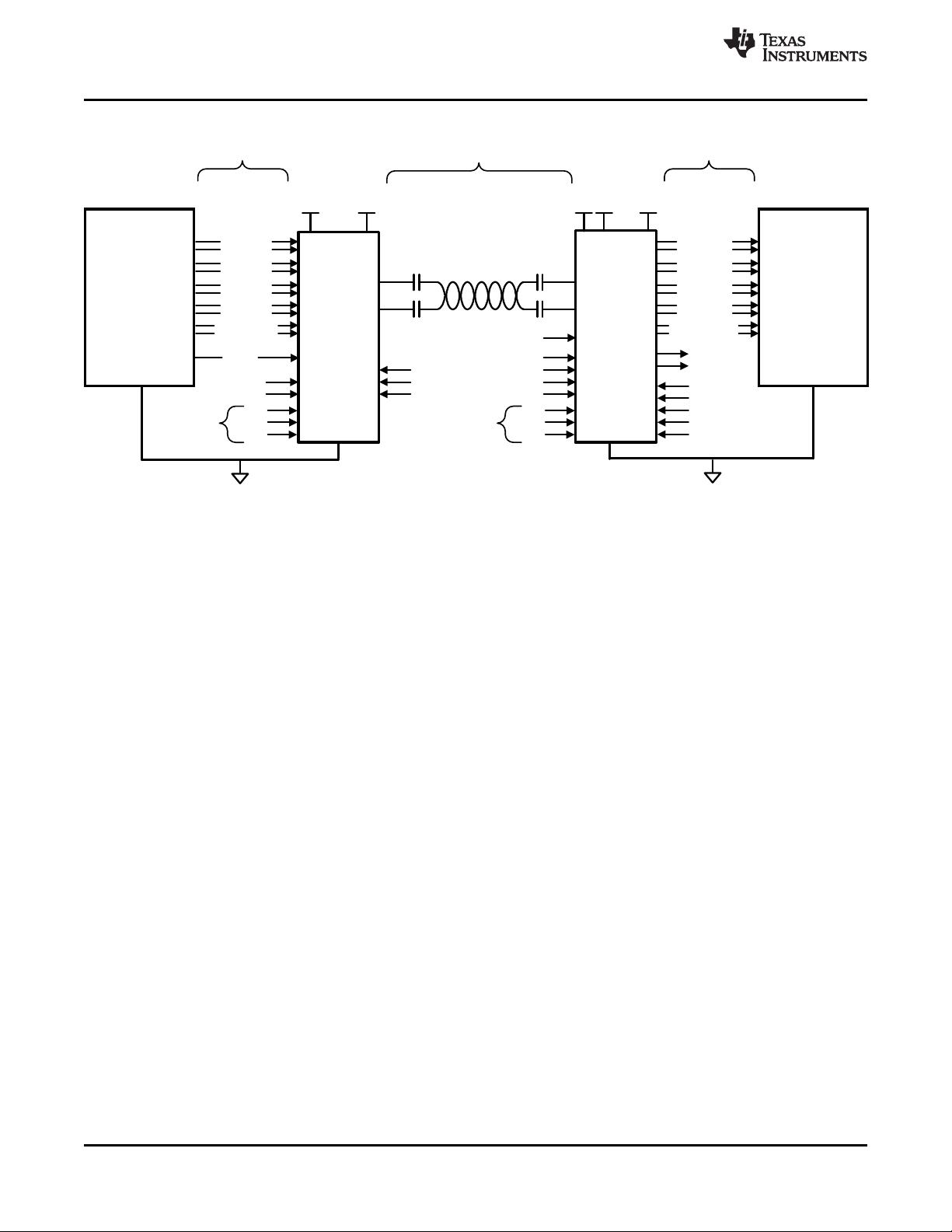

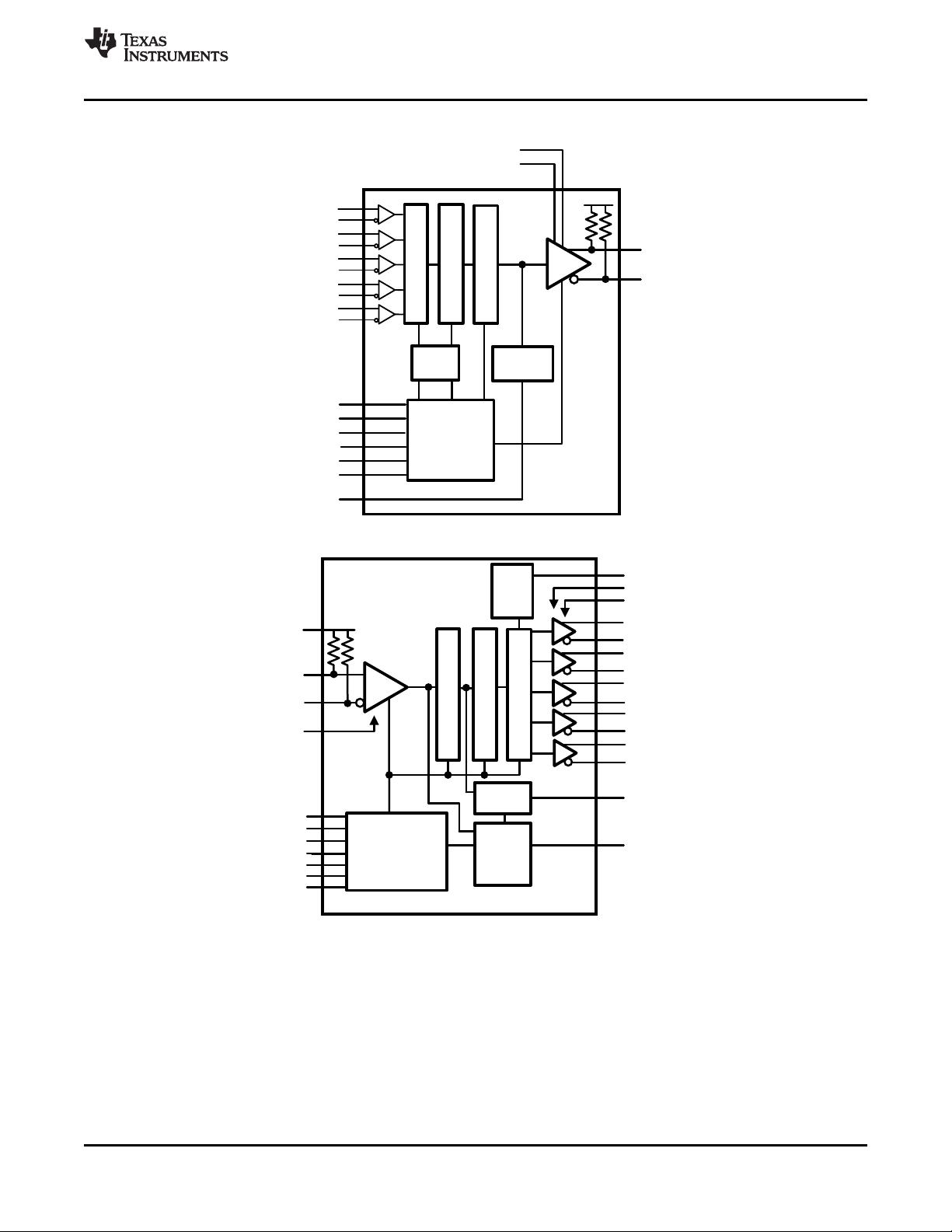

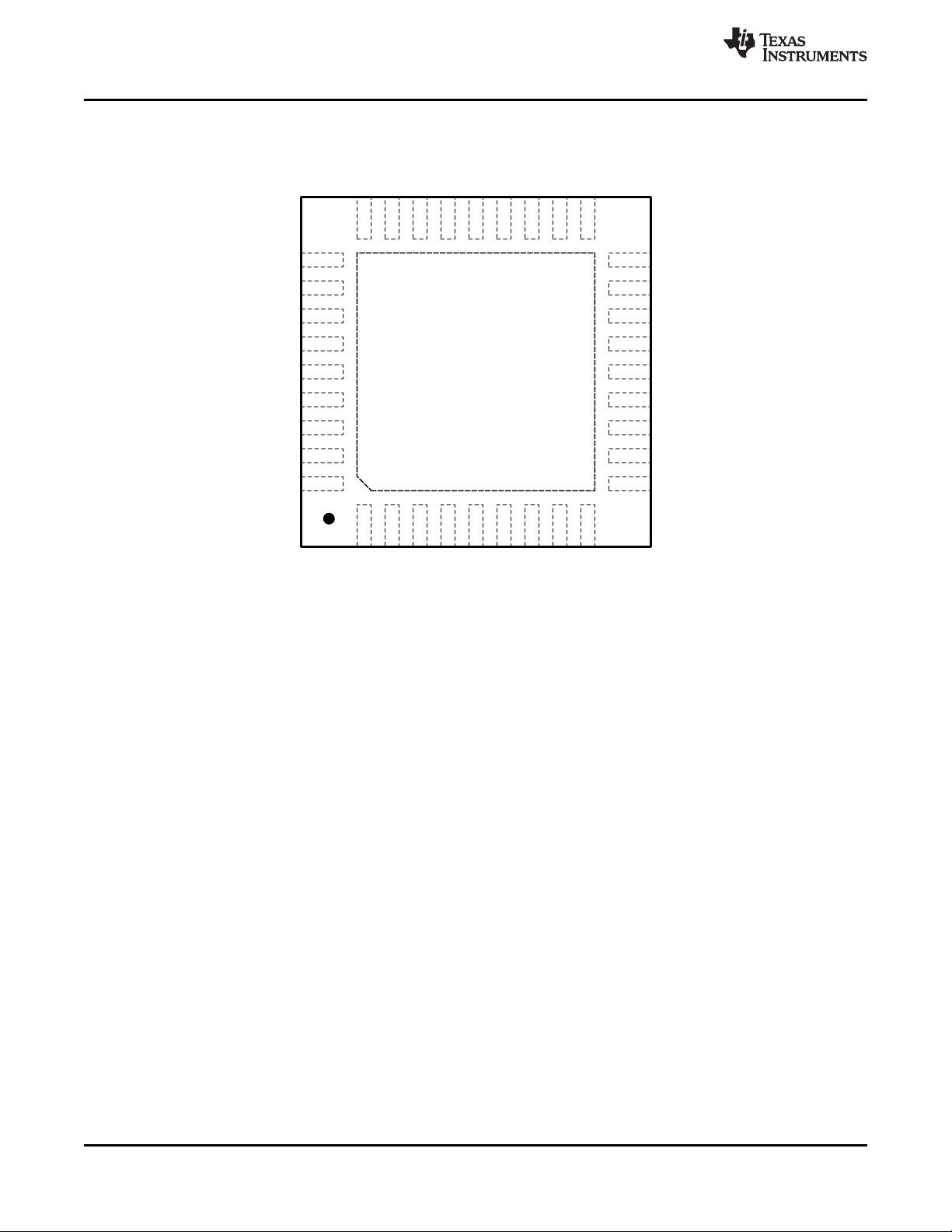

TI的DS92LV0411和DS92LV0412是LVDS(Low Voltage Differential Signaling)解串器与串行器芯片,主要用于实现高速数据传输。这两款器件是Channel Link II系列的一部分,能够将LVDS并行接口转换为高速串行接口,以减少互连成本和设计挑战。 **DS92LV0411**是串行器,它将一个24位的数据视频接口(4路LVDS数据加1路LVDS时钟)转换成一个5-50MHz的高速串行接口,通过单对CML(Current Mode Logic)线路进行传输。该器件支持3位控制信号,并且内置了串行CML终端电阻,有助于提高信号完整性和减少反射。 **DS92LV0412**是解串器,能够接收来自DS92LV0411的串行信号并恢复为5-50MHz的并行LVDS数据,同时自动锁定到输入数据,无需外部参考时钟或特殊同步模式,实现了即插即用的便捷操作。解串器还具有可选的I2C兼容串行控制总线,便于编程和配置。 **关键特性:** 1. **LVDS并行接口**:支持24位数据视频接口,降低了FPGA输入/输出引脚的需求,减少了板级走线数量,减轻了电磁干扰(EMI)问题。 2. **AC耦合STP互连**:支持长达10米的AC耦合屏蔽双绞线连接,确保长距离传输的可靠性。 3. **集成串行CML终端电阻**:优化信号传输,减少信号失真。 4. **AT-SPEED BIST模式**:内部包含自动测试(Built-In Self Test)功能,可以验证链路的完整性,用于系统诊断。 5. **可编程发射去加重和接收均衡**:适应不同的电缆和背板条件,延长在损耗性电缆上的传输距离。 6. **数据扰乱器**:通过数据扰乱减少EMI,改善信号质量。 7. **DC平衡编码器**:确保AC耦合的有效性,保证信号在传输过程中的稳定。 8. **可选择的输出电压摆幅和可调去加重**:根据系统需求调整输出信号的电压摆幅和去加重程度,以优化性能。 9. **可调输入接收均衡**:适应不同通道条件,优化接收端信号质量。 10. **ESD保护**:提供超过8kV的人体模型静电放电保护,增强系统抗静电干扰能力。 11. **工作温度范围**:可在-40°C到+85°C的宽温范围内稳定工作。 12. **电源管理模式**:电源下降模式可以降低功耗,适合低功耗应用。 DS92LV0411和DS92LV0412是LVDS传输解决方案的关键组件,它们提供高效、灵活和可靠的串行/解串功能,广泛应用于视频传输、数据通信和工业自动化等领域,帮助设计师简化设计,降低成本,同时提升系统性能和稳定性。

剩余54页未读,继续阅读

m0_745259962023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

m0_745259962023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 CSDN_1872023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

CSDN_1872023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 2301_763960562023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

2301_763960562023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

- 粉丝: 3450

- 资源: 5759

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功