没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS92LV1224.pdf

试读

23页

TI的DS92LV1224是一款专为高速单向串行数据传输设计的LVDS(低压差分信号)解串器。该器件适用于30到66MHz的频率范围,可实现300到660 Mb/s的数据吞吐率,特别适合在FR-4印刷电路板背板和平衡铜缆上简化PCB设计并降低成本。

**主要特性**

1. **30-66 MHz单1:10解串器**:DS92LV1224将接收到的与嵌入式时钟同步的10位宽Bus LVDS串行数据流转换回10位并行数据总线,并恢复并行时钟。这简化了数据路径,减少了PCB的尺寸和层数,降低了成本。

2. **时钟恢复功能**:从PLL锁定到随机数据模式,都能确保时钟的稳定恢复,提供出色的噪声免疫力和低EMI(电磁干扰)性能。

3. **每个数据转移周期确保转换**:确保每次数据传输时都有明确的转换,提高系统稳定性。

4. **低功耗**:在66 MHz工作时,典型功耗小于300 mW,降低了系统运行的能耗。

5. **单个差分对消除多通道 skew**:通过使用单个差分对,避免了多个通道之间的时钟与数据、数据与数据之间的偏移问题。

6. **流动式引脚布局**:设计有流动式引脚布局,便于PCB布局,节省空间。

7. **同步模式和锁定指示器**:提供同步模式和锁定状态指示,方便系统监控和调试。

8. **可编程边沿触发时钟**:用户可以根据需求设置时钟触发边缘,增强了系统的灵活性。

9. **电源关闭时高阻抗接收输入**:当电源关闭时,接收输入端进入高阻抗状态,防止未定义的信号输入。

10. **小型28引脚SSOP封装**:采用28引脚的小型表面贴装封装,节省板级空间。

**工作原理**

DS92LV1224的工作流程主要包括两个部分:串行至并行转换和时钟恢复。串行输入通过PLL(锁相环)进行同步和解码,然后通过10位并行输出latch将数据转换为并行格式。同时,时钟恢复单元从串行数据流中提取并恢复出原始的并行时钟。该器件的锁定指示器会显示PLL是否成功锁定到数据流,确保数据的准确传输。

在设计PCB时,利用DS92LV1224的流动式引脚布局可以简化布线,减少信号间的相互干扰。此外,由于DS92LV1224支持低功耗运行,因此对于电池供电或能源敏感的应用来说,是一个理想的解决方案。

TI的DS92LV1224 LVDS解串器通过简化高速数据传输的硬件设计,提供了高效、低功耗且可靠的并行数据恢复方案,是高性能通信、数据中心和工业应用的理想选择。在使用此设备时,应遵循TI提供的标准保修和使用指南,特别是在关键应用中,确保设备的正确选型和使用。

PARALLEL-TO-SERIAL

INPUT LATCH

TIMING and

CONTROL

PLL

10-BIT SERIALIZER

SYNC1

SYNC2

TCLK

(30 MHz to 66 MHz)

TCLK_R/F

D

IN

10

D

O+

D

O-

DEN

SERIAL-TO-PARALLEL

OUTPUT LATCH

R

I+

R

I-

LVDS

DS92LV1224

TIMING and

CONTROL

PLL

CLOCK

RECOVERY

10

R

OUT

REFCLK

REN

LOCK

RCLK

(30 MHz to 66 MHz)

RCLK_R/F

DS92LV1224

www.ti.com

SNLS189A –APRIL 2005–REVISED APRIL 2013

DS92LV1224 30-66 MHz 10 Bit Bus LVDS Deserializer

Check for Samples: DS92LV1224

1

FEATURES

DESCRIPTION

The DS92LV1224 is a 300 to 660 Mb/s deserializer

2

• 30–66 MHz Single 1:10 Deserializer with

for high-speed unidirectional serial data transmission

300–660 Mb/s Throughput

over FR-4 printed circuit board backplanes and

• Robust Bus LVDS Serial Data Transmission

balanced copper cables. It receives the Bus LVDS

with Embedded Clock for Exceptional Noise

serial data stream from a compatible 10–bit serializer,

Immunity and Low EMI

transforms it back into a 10-bit wide parallel data bus

and recovers parallel clock. This single serial data

• Clock Recovery from PLL Lock to Random

stream simplifies PCB design and reduces PCB cost

Data Patterns

by narrowing data paths that in turn reduce PCB size

• Ensured Transition Every Data Transfer Cycle

and number of layers. The single serial data stream

• Low Power Consumption < 300 mW (typ)

also reduces cable size, the number of connectors,

at 66 MHz

and eliminates clock-to-data and data-to-data skew.

• Single Differential Pair Eliminates Multi-

The DS92LV1224 works well with Bus LVDS 10–bit

Channel Skew

serializers within its specified frequency operating

range. It features low power consumption, and high

• Flow-Through Pinout for Easy PCB Layout

impedance outputs in power down mode.

• Synchronization Mode and LOCK Indicator

The DS92LV1224 was designed with the flow-through

• Programmable Edge Trigger on Clock

pinout and is available in a space saving 28–lead

• High Impedance on Receiver Inputs when

SSOP package.

Power is Off

• Small 28-Lead SSOP Package

Block Diagrams

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2005–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

DS92LV1224

SNLS189A –APRIL 2005–REVISED APRIL 2013

www.ti.com

Functional Description

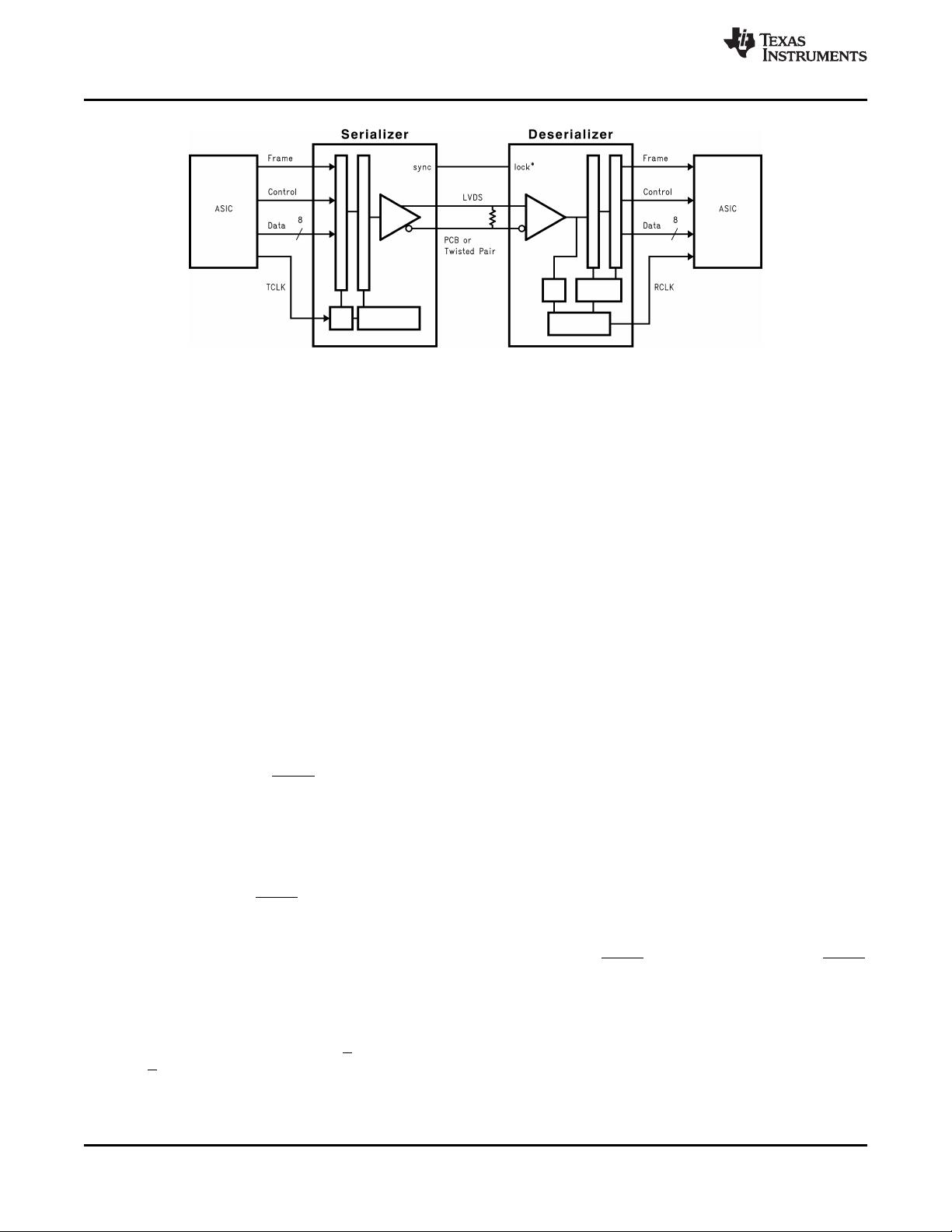

The DS92LV1224 is a 10-bit Deserializer device which together with a compatible serializer (i.e. DS92LV1023E)

forms a chipset designed to transmit data over FR-4 printed circuit board backplanes and balanced copper

cables at clock speeds from 30 MHz to 66 MHz.

The chipset has three active states of operation: Initialization, Data Transfer, and Resynchronization; and two

passive states: Powerdown and TRI-STATE.

The following sections describe each operation and passive state.

Initialization

Initialization of both devices must occur before data transmission begins. Initialization refers to synchronization of

the Serializer and Deserializer PLL's to local clocks, which may be the same or separate. Afterwards,

synchronization of the Deserializer to Serializer occurs.

Step 1: When you apply V

CC

to both Serializer and/or Deserializer, the respective outputs enter TRI-STATE, and

on-chip power-on circuitry disables internal circuitry. When V

CC

reaches V

CC

OK (2.5V) the PLL in each device

begins locking to a local clock. For the Serializer, the local clock is the transmit clock (TCLK) provided by the

source ASIC or other device. For the Deserializer, you must apply a local clock to the REFCLK pin.

The Serializer outputs remain in TRI-STATE while the PLL locks to the TCLK. After locking to TCLK, the

Serializer is now ready to send data or SYNC patterns, depending on the levels of the SYNC1 and SYNC2 inputs

or a data stream. The SYNC pattern sent by the Serializer consists of six ones and six zeros switching at the

input clock rate.

Note that the Deserializer LOCK output will remain high while its PLL locks to the incoming data or to SYNC

patterns on the input.

Step 2: The Deserializer PLL must synchronize to the Serializer to complete initialization. The Deserializer will

lock to non-repetitive data patterns. However, the transmission of SYNC patterns enables the Deserializer to lock

to the Serializer signal within a specified time.

The user's application determines control of the SYNC1 and SYNC 2 pins. One recommendation is a direct

feedback loop from the LOCK pin. Under all circumstances, the Serializer stops sending SYNC patterns after

both SYNC inputs return low.

When the Deserializer detects edge transitions at the Bus LVDS input, it will attempt to lock to the embedded

clock information. When the Deserializer locks to the Bus LVDS clock, the LOCK output will go low. When LOCK

is low, the Deserializer outputs represent incoming Bus LVDS data.

Data Transfer

After initialization, the Serializer will accept data from inputs DIN0–DIN9. The Serializer uses the TCLK input to

latch incoming Data. The TCLK_R/F pin selects which edge the Serializer uses to strobe incoming data.

TCLK_R/F high selects the rising edge for clocking data and low selects the falling edge. If either of the SYNC

inputs is high for 5*TCLK cycles, the data at DIN0-DIN9 is ignored regardless of clock edge.

2 Submit Documentation Feedback Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: DS92LV1224

DS92LV1224

www.ti.com

SNLS189A –APRIL 2005–REVISED APRIL 2013

After determining which clock edge to use, a start and stop bit, appended internally, frame the data bits in the

register. The start bit is always high and the stop bit is always low. The start and stop bits function as the

embedded clock bits in the serial stream.

The Serializer transmits serialized data and clock bits (10+2 bits) from the serial data output (DO±) at 12 times

the TCLK frequency. For example, if TCLK is 66 MHz, the serial rate is 66 × 12 = 792 Mega-bits-per-second.

Since only 10 bits are from input data, the serial “payload” rate is 10 times the TCLK frequency. For instance, if

TCLK = 66 MHz, the payload data rate is 66 × 10 = 660 Mbps. The data source provides TCLK and must be in

the range of 30 MHz to 66 MHz nominal.

The Serializer outputs (DO±) can drive a point-to-point connection or in limited multi-point or multi-drop

backplanes. The outputs transmit data when the enable pin (DEN) is high, PWRDN = high, and SYNC1 and

SYNC2 are low. When DEN is driven low, the Serializer output pins will enter TRI-STATE.

When the Deserializer synchronizes to the Serializer, the LOCK pin is low. The Deserializer locks to the

embedded clock and uses it to recover the serialized data. ROUT data is valid when LOCK is low. Otherwise

ROUT0–ROUT9 is invalid.

The ROUT0-ROUT9 pins use the RCLK pin as the reference to data. The polarity of the RCLK edge is controlled

by the RCLK_R/F input. See Figure 6.

ROUT(0-9), LOCK and RCLK outputs will drive a maximum of three CMOS input gates (15 pF load) with a 66

MHz clock.

Resynchronization

When the Deserializer PLL locks to the embedded clock edge, the Deserializer LOCK pin asserts a low. If the

Deserializer loses lock, the LOCK pin output will go high and the outputs (including RCLK) will enter TRI-STATE.

The user's system monitors the LOCK pin to detect a loss of synchronization. Upon detection, the system can

arrange to pulse the Serializer SYNC1 or SYNC2 pin to resynchronize. Multiple resynchronization approaches

are possible. One recommendation is to provide a feedback loop using the LOCK pin itself to control the sync

request of the Serializer (SYNC1 or SYNC2). Dual SYNC pins are provided for multiple control in a multi-drop

application. Sending sync patterns for resynchronization is desirable when lock times within a specific time are

critical. However, the Deserializer can lock to random data, which is discussed in the next section.

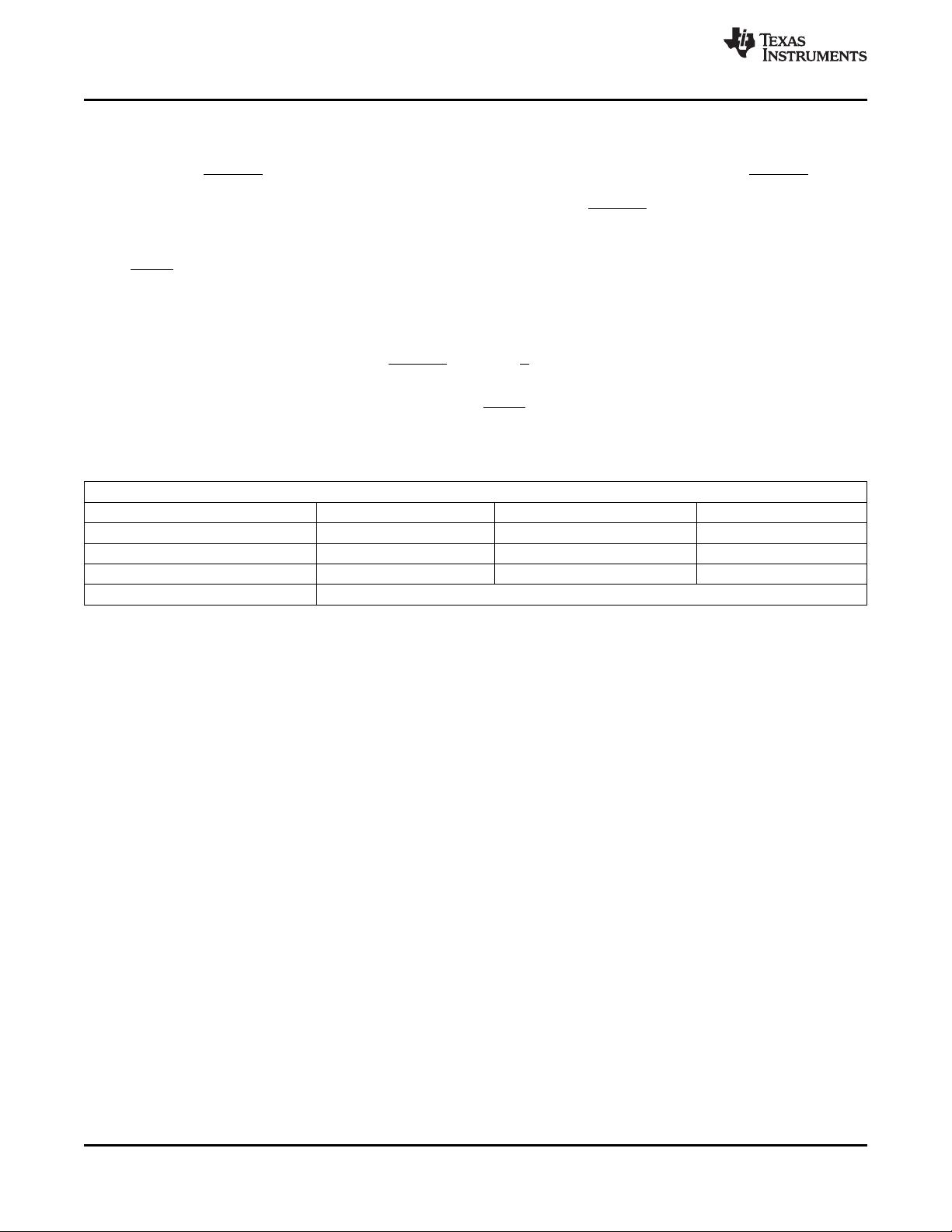

Random Lock Initialization and Resynchronization

The initialization and resynchronization methods described in their respective sections are the fastest ways to

establish the link between the Serializer and Deserializer. However, the DS92LV1224 can attain lock to a data

stream without requiring the Serializer to send special SYNC patterns. This allows the DS92LV1224 to operate in

“open-loop” applications. Equally important is the Deserializer's ability to support hot insertion into a running

backplane. In the open loop or hot insertion case, we assume the data stream is essentially random. Therefore,

because lock time varies due to data stream characteristics, we cannot possibly predict exact lock time.

However, please see Table 1 for some general random lock times under specific conditions. The primary

constraint on the “random” lock time is the initial phase relation between the incoming data and the REFCLK

when the Deserializer powers up. As described in the next paragraph, the data contained in the data stream can

also affect lock time.

If a specific pattern is repetitive, the Deserializer could enter “false lock” - falsely recognizing the data pattern as

the clocking bits. We refer to such a pattern as a repetitive multi-transition, RMT. This occurs when more than

one Low-High transition takes place in a clock cycle over multiple cycles. This occurs when any bit, except DIN

9, is held at a low state and the adjacent bit is held high, creating a 0-1 transition. In the worst case, the

Deserializer could become locked to the data pattern rather than the clock. Circuitry within the DS92LV1224 can

detect that the possibility of “false lock” exists. The circuitry accomplishes this by detecting more than one

potential position for clocking bits. Upon detection, the circuitry will prevent the LOCK output from becoming

active until the potential “false lock” pattern changes. The false lock detect circuitry expects the data will

eventually change, causing the Deserializer to lose lock to the data pattern and then continue searching for clock

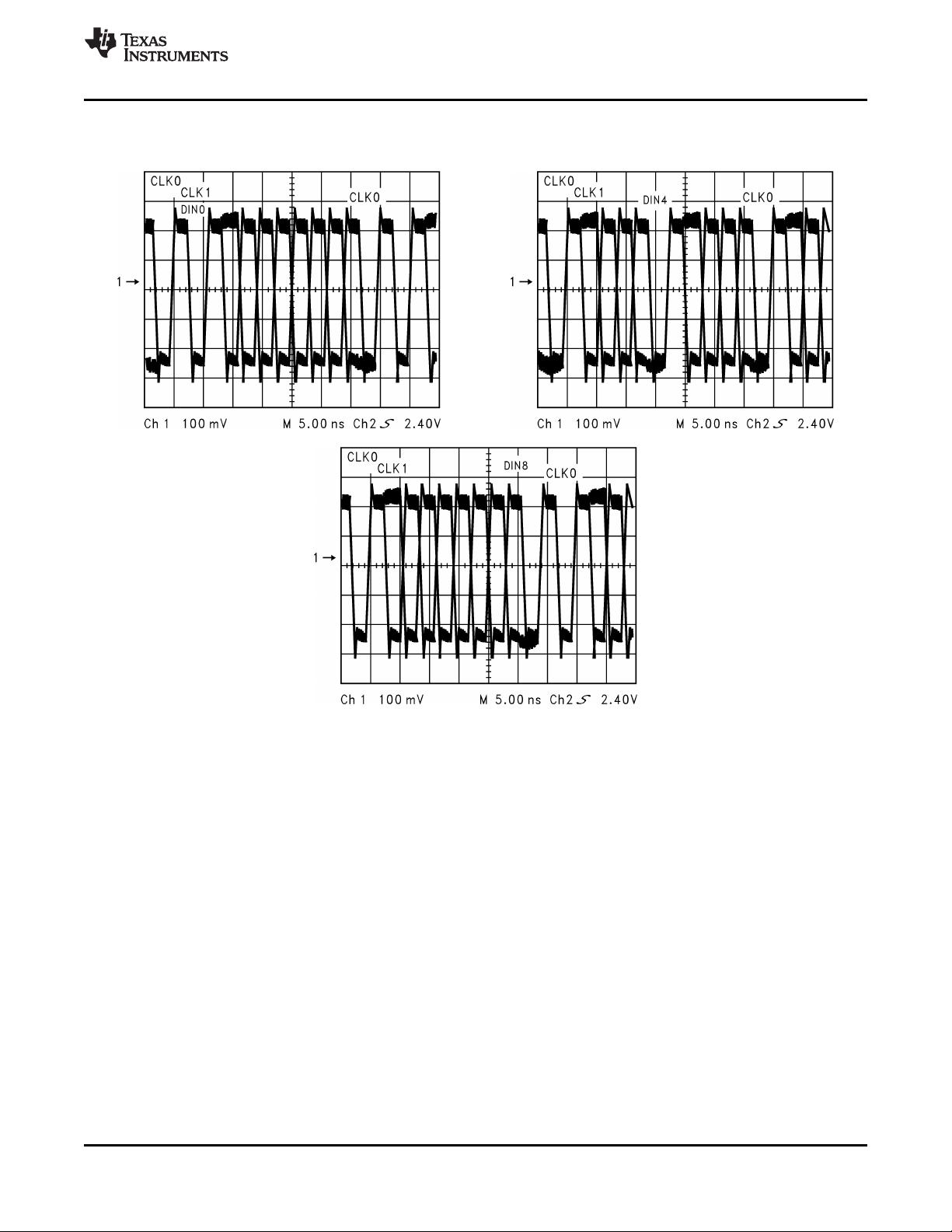

bits in the serial data stream. Graphical representations of RMT are shown in Figure 1. Please note that RMT

only applies to bits DIN0-DIN8.

Copyright © 2005–2013, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: DS92LV1224

DS92LV1224

SNLS189A –APRIL 2005–REVISED APRIL 2013

www.ti.com

Powerdown

When no data transfer occurs, you can use the Powerdown state. The Serializer and Deserializer use the

Powerdown state, a low power sleep mode, to reduce power consumption. The Deserializer enters Powerdown

when you drive PWRDN and REN low. The Serializer enters Powerdown when you drive PWRDN low. In

Powerdown, the PLL stops and the outputs enter TRI-STATE, which disables load current and reduces supply

current to the milliampere range. To exit Powerdown, you must drive the PWRDN pin high.

Before valid data exchanges between the Serializer and Deserializer, you must reinitialize and resynchronize the

devices to each other. Initialization of the Serializer takes 510 TCLK cycles. The Deserializer will initialize and

assert LOCK high until lock to the Bus LVDS clock occurs.

TRI-STATE

The Serializer enters TRI-STATE when the DEN pin is driven low. This puts both driver output pins (DO+ and

DO−) into TRI-STATE. When you drive DEN high, the Serializer returns to the previous state, as long as all other

control pins remain static (SYNC1, SYNC2, PWRDN, TCLK_R/F).

When you drive the REN pin low, the Deserializer enters TRI-STATE. Consequently, the receiver output pins

(ROUT0–ROUT9) and RCLK will enter TRI-STATE. The LOCK output remains active, reflecting the state of the

PLL.

Table 1.

(1)

Random Lock Times for the DS92LV1224

40 MHz 66 MHz Units

Maximum 26 18 μs

Mean 4.5 3.0 μs

Minimum 0.77 0.43 μs

Conditions: PRBS 2

15

, V

CC

= 3.3V

(1) Difference in lock times are due to different starting points in the data pattern with multiple parts.

4 Submit Documentation Feedback Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: DS92LV1224

DS92LV1224

www.ti.com

SNLS189A –APRIL 2005–REVISED APRIL 2013

Figure 1. RMT Patterns Seen on the Bus LVDS Serial Output

DIN0 Held Low-DIN1 Held High Creates an RMT Pattern DIN4 Held Low-DIN5 Held High Creates an RMT Pattern

DIN8 Held Low-DIN9 Held High Creates an RMT Pattern

Copyright © 2005–2013, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Links: DS92LV1224

剩余22页未读,继续阅读

资源推荐

资源评论

148 浏览量

2023-02-08 上传

2023-02-08 上传

171 浏览量

174 浏览量

139 浏览量

152 浏览量

2023-02-08 上传

192 浏览量

133 浏览量

2023-02-08 上传

资源评论

2301_763960562023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

2301_763960562023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

不觉明了

- 粉丝: 7479

- 资源: 5764

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【锂电池剩余寿命预测】TCN时间卷积神经网络锂电池剩余寿命预测,马里兰大学锂电池数据集(Pytorch完整源码和数据)

- stm32 USB 复合设备使用msc cdc

- 武汉、西安等城市预处理后的路网数据,包括道路双线转单线、中心打断等等

- 【锂电池剩余寿命预测】Transformer锂电池剩余寿命预测,马里兰大学锂电池数据集(Pytorch完整源码和数据)

- 汽车电机壳体压装产线sw18可编辑全套技术资料100%好用.zip

- boot-win7.c2c84adb.mp4

- redis笔记自学笔记自学笔记

- 前端分析-2023071100789

- 工创赛k210视觉识别

- 前端分析-2023071100789

- Java 21 新特性详解:虚拟线程、字符串模板与模式匹配等亮点

- Photoshop-CS6-13.0.1-简化版

- 通过网盘分享的文件:中国国家级地面气象站基本气象要素日值数据集(V3.0)SURF-CLI-CHN-MUL-DAY-V3.0.zip

- AI游戏Flappy-Bird

- Java各版本新特性一览表,汇总Java 8~21的新特性,按功能分类速查

- 大模型与智能制造融合创新报告,涵盖智能制造背景、大模型技术赋能、工艺优化、智能研发、生产调度、供应链优化、数据安全等内容,助力制造业降本增效、智能化升级与高效决策,适用于行业报告撰写与企业战略规划

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功