没有合适的资源?快使用搜索试试~ 我知道了~

TI-LMH1981.pdf

需积分: 11 0 下载量 15 浏览量

2022-11-30

13:02:12

上传

评论 4

收藏 1.3MB PDF 举报

温馨提示

试读

26页

TI-LMH1981.pdf

资源推荐

资源详情

资源评论

R

EXT

GND

V

CC1

V

IN

GND

V

CC2

HSOUT

OEOUT

BPOUT

CSOUT

V

CC3

GND

VFOUT

VSOUT

LMH1981

1

2

3

4

5

6

7

14

13

12

11

10

9

8

LMH1981

www.ti.com

SNLS214H –APRIL 2006–REVISED MARCH 2013

LMH1981 Multi-Format Video Sync Separator

Check for Samples: LMH1981

1

FEATURES

DESCRIPTION

The LMH1981 is a high performance multi-format

2

• Standard Analog Video Sync Separation for

sync separator ideal for use in a wide range of video

NTSC, PAL, 480I/P, 576I/P, 720P, and

applications, such as broadcast and professional

1080I/P/PsF from Composite Video (CVBS),

video equipment and HDTV/DTV systems.

S-Video (Y/C), and Component Video

The input accepts standard analog SD/ED/HD video

(YP

B

P

R

/GBR) Interfaces

signals with either bi-level or tri-level sync, and the

• Bi-Level & Tri-Level Sync Compatible

outputs provide all of the critical timing signals in

• Composite, Horizontal, and Vertical Sync

CMOS logic, which swing from rail-to-rail (V

CC

and

Outputs

GND) including Composite, Horizontal, and Vertical

Syncs, Burst/Back Porch Timing, Odd/Even Field,

• Burst/Back Porch Timing, Odd/Even Field, and

and Video Format Outputs. HSync features very low

Video Format Outputs

jitter on its leading (falling) edge, minimizing external

• Superior Jitter Performance on Leading Edge

circuitry needed to clean and reduce jitter in

of HSync

subsequent clock generation stages.

• Automatic Video Format Detection

The LMH1981 automatically detects the input video

• 50% Sync Slicing for Video Inputs from 0.5 V

PP

format, eliminating the need for programming using a

to 2 V

PP

microcontroller, and applies precise 50% sync slicing

to ensure accurate sync extraction at O

H

, even for

• 3.3V to 5V Supply Operation

inputs with irregular amplitude from improper

termination or transmission loss. Its unique Video

APPLICATIONS

Format Output conveys the total horizontal line count

• Broadcast and Professional Video Equipment

per field as an 11-bit binary serial data stream, which

can be decoded by the video system to determine the

• HDTV/DTV Systems

input video format and enable dynamic adjustment of

• Genlock Circuits

system parameters, i.e.: color space or scaler

• Video Capture Devices

conversions. The LMH1981 is available in a 14-pin

• Set-Top Boxes (STB) & Digital Video

TSSOP package and operates over a temperature

range of −40°C to +85°C.

Recorders (DVR)

• Video Displays

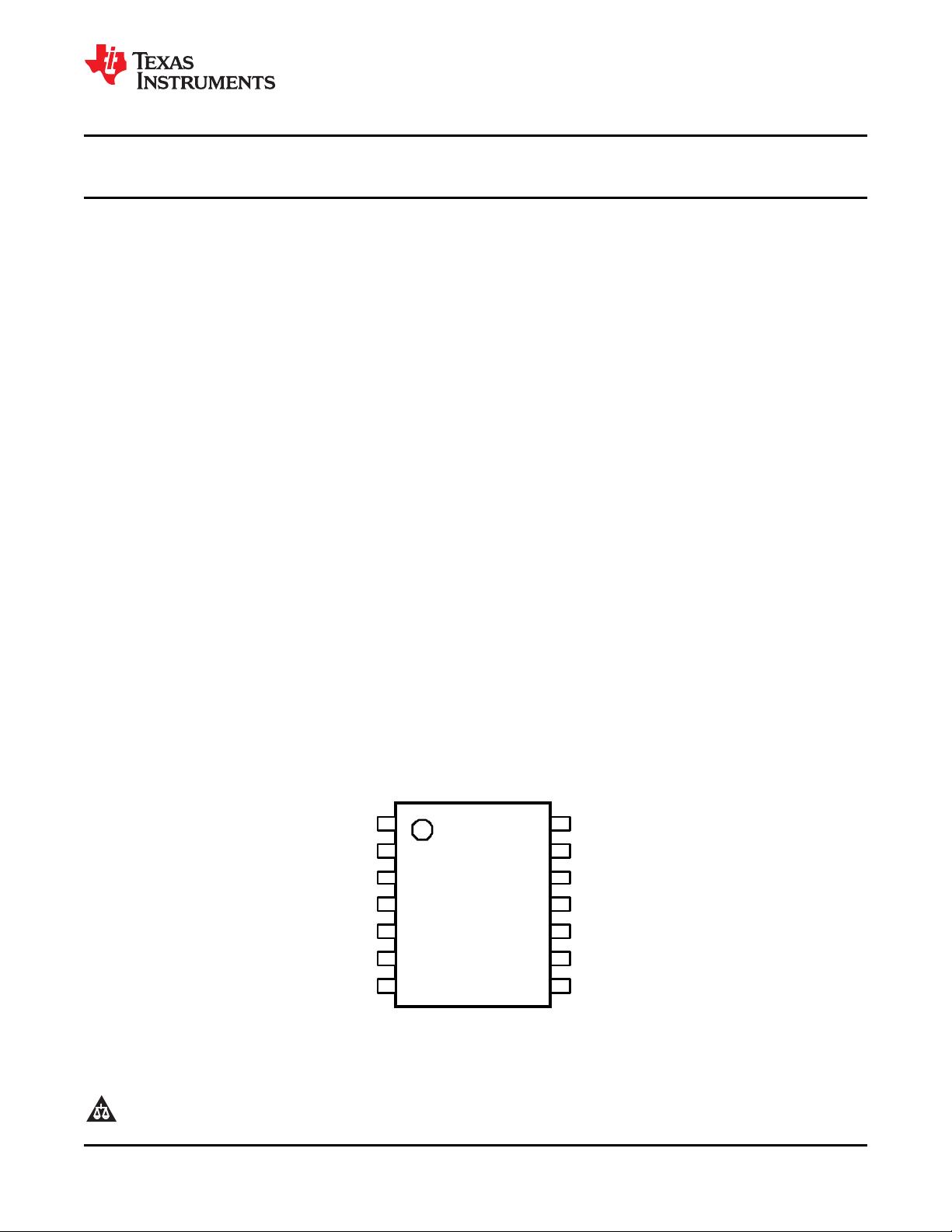

Connection Diagram

Figure 1. 14-Pin TSSOP - Top View

See PW Package

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2006–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

LMH1981

SNLS214H –APRIL 2006–REVISED MARCH 2013

www.ti.com

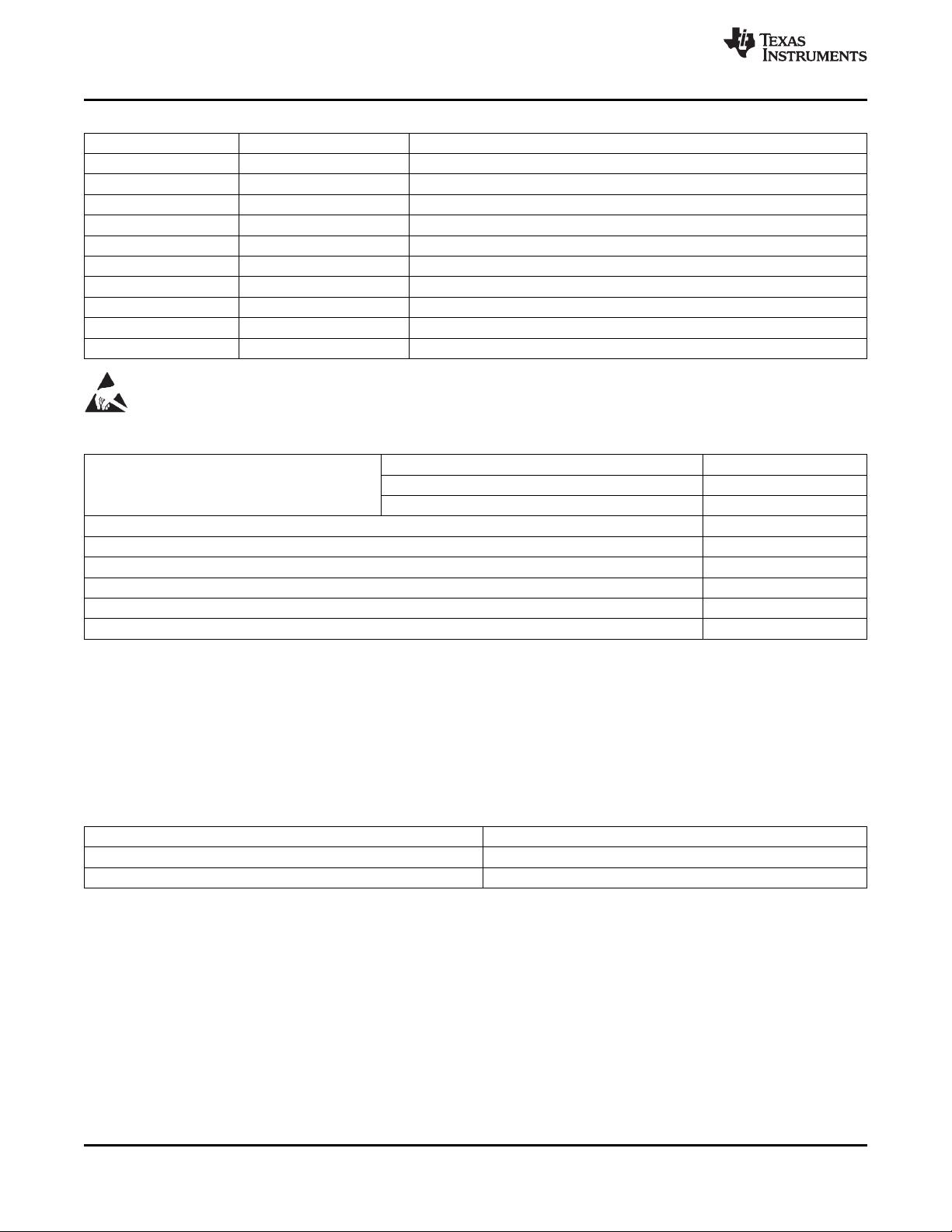

PIN DESCRIPTIONS

Pin No. Pin Name Pin Description

1 R

EXT

Bias Current External Resistor

2, 5, 10 GND Ground

3, 6, 11 V

CC

Supply Voltage

4 V

IN

Video Input

7 HSOUT Horizontal Sync Output

8 VSOUT Vertical Sync Output

9 VFOUT Video Format Output

12 CSOUT Composite Sync Output

13 BPOUT Burst/Back Porch Timing Output

14 OEOUT Odd/Even Field Output

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings

(1)(2)(3)

ESD Tolerance

(4)

Human Body Model 3.5 kV

Machine Model 350V

Charge-Device Model 1.0 kV

Supply Voltage, V

CC

0V to 5.5V

Video Input, V

IN

−0.3V to V

CC

+ 0.3V

Storage Temperature Range −65°C to +150°C

Lead Temperature (soldering 10 sec.) 300°C

Junction Temperature (T

JMAX

)

(5)

+150°C

Thermal Resistance (θ

JA

) 52°C/W

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for

which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test

conditions, see the Electrical Characteristics Tables.

(2) All voltages are measured with respect to GND, unless otherwise specified.

(3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and

specifications.

(4) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of

JEDEC)Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

(5) The maximum power dissipation is a function of T

J(MAX)

, θ

JA

. The maximum allowable power dissipation at any ambient temperature is

P

D

= (T

J(MAX)

- T

A

)/θ

JA

. All numbers apply for packages soldered directly onto a PC board.

Operating Ratings

(1)

Temperature Range

(2)

−40°C to +85°C

V

CC

3.3V −5% to 5V +5%

Input Amplitude, V

IN-AMPL

140 mV to V

CC

–V

IN-CLAMP

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for

which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test

conditions, see the Electrical Characteristics Tables.

(2) The maximum power dissipation is a function of T

J(MAX)

, θ

JA

. The maximum allowable power dissipation at any ambient temperature is

P

D

= (T

J(MAX)

- T

A

)/θ

JA

. All numbers apply for packages soldered directly onto a PC board.

2 Submit Documentation Feedback Copyright © 2006–2013, Texas Instruments Incorporated

Product Folder Links: LMH1981

LMH1981

www.ti.com

SNLS214H –APRIL 2006–REVISED MARCH 2013

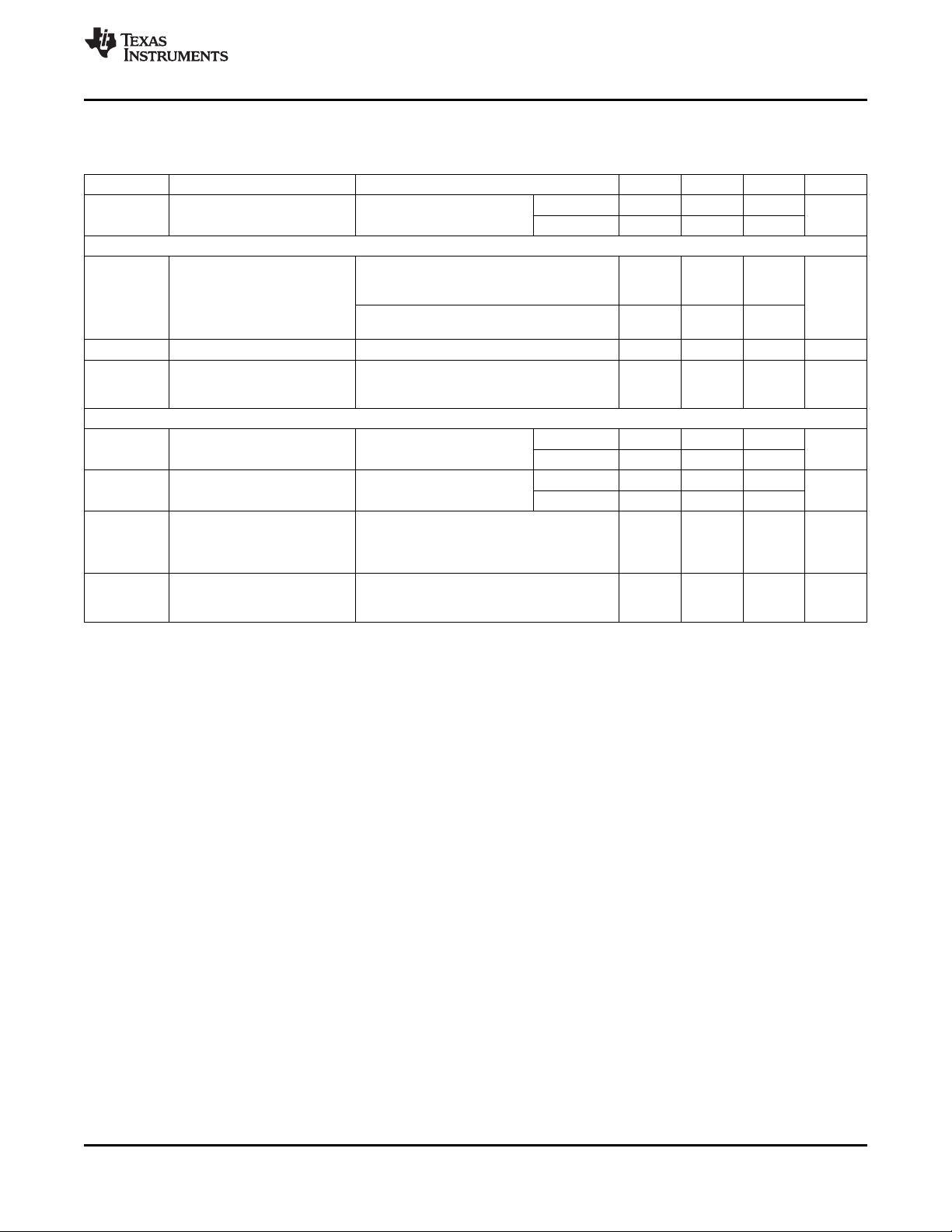

Electrical Characteristics

(1)

Unless otherwise specified, all limits are ensured for T

A

= 25°C, V

CC

= V

CC1

= V

CC2

= V

CC3

= 3.3V, R

EXT

= 10 kΩ 1%,

R

L

= 10 kΩ, C

L

< 10 pF.Boldface limits apply at the temperature extremes. See Figure 2.

Symbol Parameter Conditions Min

(2)

Typ

(3)

Max

(2)

Units

I

CC

Supply Current No input signal V

CC

= 3.3V 9.5 11.5

mA

V

CC

= 5V 11 13.5

Video Input Specifications

V

IN-SYNC

Input Sync Amplitude Amplitude from negative sync tip to video 0.14 0.30 0.60

blanking level for SD/EDTV bi-level sync

(4)(5)(6)

V

PP

Amplitude from negative to positive sync tips 0.30 0.60 1.20

for HDTV tri-level sync

(4)(7)(6)

V

IN-CLAMP

Input Sync Tip Clamp Level 0.7 V

V

IN-SLICE

Input Sync Slice Level Level between video blanking & sync tip for 50 %

SD/EDTV and between negative & positive

sync tips for HDTV

Logic Output Specifications

(8)

V

OL

Output Logic 0 See output load conditions V

CC

= 3.3V 0.3

V

above

V

CC

= 5V 0.5

V

OH

Output Logic 1 See output load conditions V

CC

= 3.3V 3.0

V

above

V

CC

= 5V 4.5

T

SYNC-LOCK

Sync Lock Time Time for the output signals to be correct after 2 V

the video signal settles at V

IN

following a periods

significant input change. See START-UP

TIME for more information

T

VSOUT

Vertical Sync Output Pulse See Figure 3, Figure 4, Figure 5, Figure 6, 3 H

Width Figure 7, and Figure 8 for SDTV, EDTV & periods

HDTV Vertical Interval Timing

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very

limited self-heating of the device such that T

J

= T

A

. No ensured specification of parametric performance is indicated in the electrical

tables under conditions of internal self-heating where T

J

> T

A

.

(2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using the

Statistical Quality Control (SQC) method.

(3) Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and

will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production

material.

(4) V

IN-AMPL

plus V

IN-CLAMP

should not exceed V

CC

.

(5) Tested with 480I signal.

(6) Maximum voltage offset between 2 consecutive input horizontal sync tips must be less than 25 mV

PP

.

(7) Tested with 720P signal.

(8) Outputs are negative-polarity logic signal, except for odd/even field and video format outputs.

Copyright © 2006–2013, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: LMH1981

+

ODD/EVEN

FIELD OUTPUT

C

3

0.1 PF

R

S

14

13

R

S

BURST/BACK PORCH

TIMING OUTPUT

12

R

S

COMPOSITE

SYNC OUTPUT

11

V

CC

10

9

8

R

S

R

S

VIDEO FORMAT

OUTPUT

VERTICAL SYNC

OUTPUT

VSOUT

VFOUT

GND

V

CC3

BPOUT

OEOUT

CSOUT

R

EXT

GND

V

CC1

V

IN

GND

V

CC2

HSOUT

R

S

HORIZONTAL

SYNC OUTPUT

V

CC

C

2

0.1 PF

7

6

5

4

3

2

1

R

EXT

10 k:, 1%

C

4

4.7 PF

C

1

0.1 PF

C

IN

1 PF

CVBS/Y/G

VIDEO INPUT

R

T

75:

V

CC

LMH1981

LMH1981

SNLS214H –APRIL 2006–REVISED MARCH 2013

www.ti.com

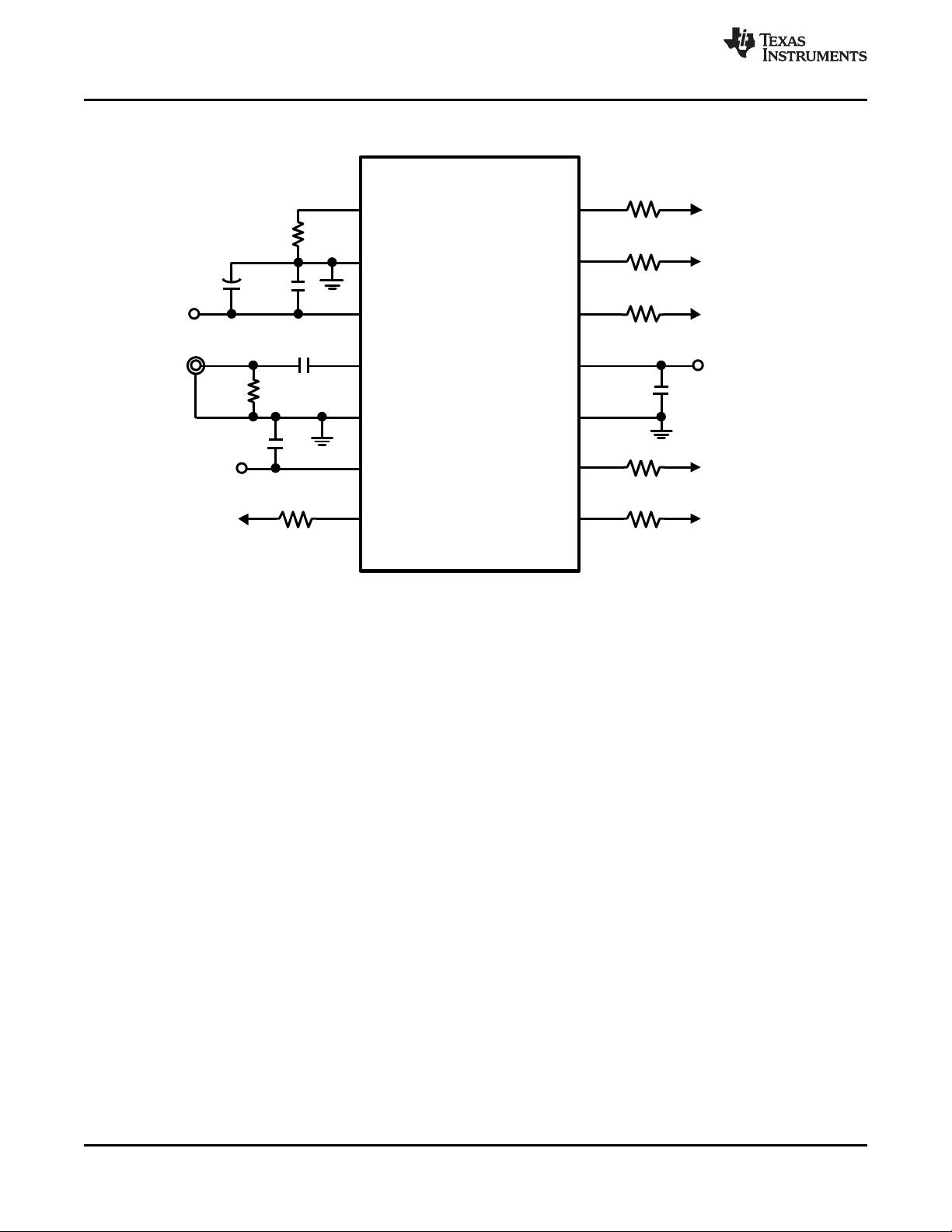

LMH1981 Test Circuit

Figure 2. Test Circuit

The LMH1981 test circuit is shown in Figure 2. The video generator should provide a low-noise, broadcast-

quality signal over 75Ω coaxial cable which should be impedance-matched with a 75Ω load termination resistor

to prevent unwanted signal distortion. The output waveforms should be monitored using a low-capacitance probe

on an oscilloscope with at least 500 MHz bandwidth. See PCB LAYOUT CONSIDERATIONS for more

information about signal and supply trace routing and component placement.

4 Submit Documentation Feedback Copyright © 2006–2013, Texas Instruments Incorporated

Product Folder Links: LMH1981

V

IN

CSOUT

HSOUT

BPOUT

VSOUT

OEOUT

264 265 266 267 268 269 270 271 272 273

EVEN FIELD

½ H

LINE # 263

START OF FIELD 2

3H

3H

3H

T

VSOUT

= 3H

V

IN

CSOUT

HSOUT

BPOUT

VSOUT

OEOUT

COLOR

BURST

START OF FIELD 1

ODD FIELD

LINE # 1 3 4 5 6 7 9 10 11525 2 8

3H

H

3H 3H

T

VSOUT

= 3H

H

½ H

VERTICAL SYNC

SERRATION

LMH1981

www.ti.com

SNLS214H –APRIL 2006–REVISED MARCH 2013

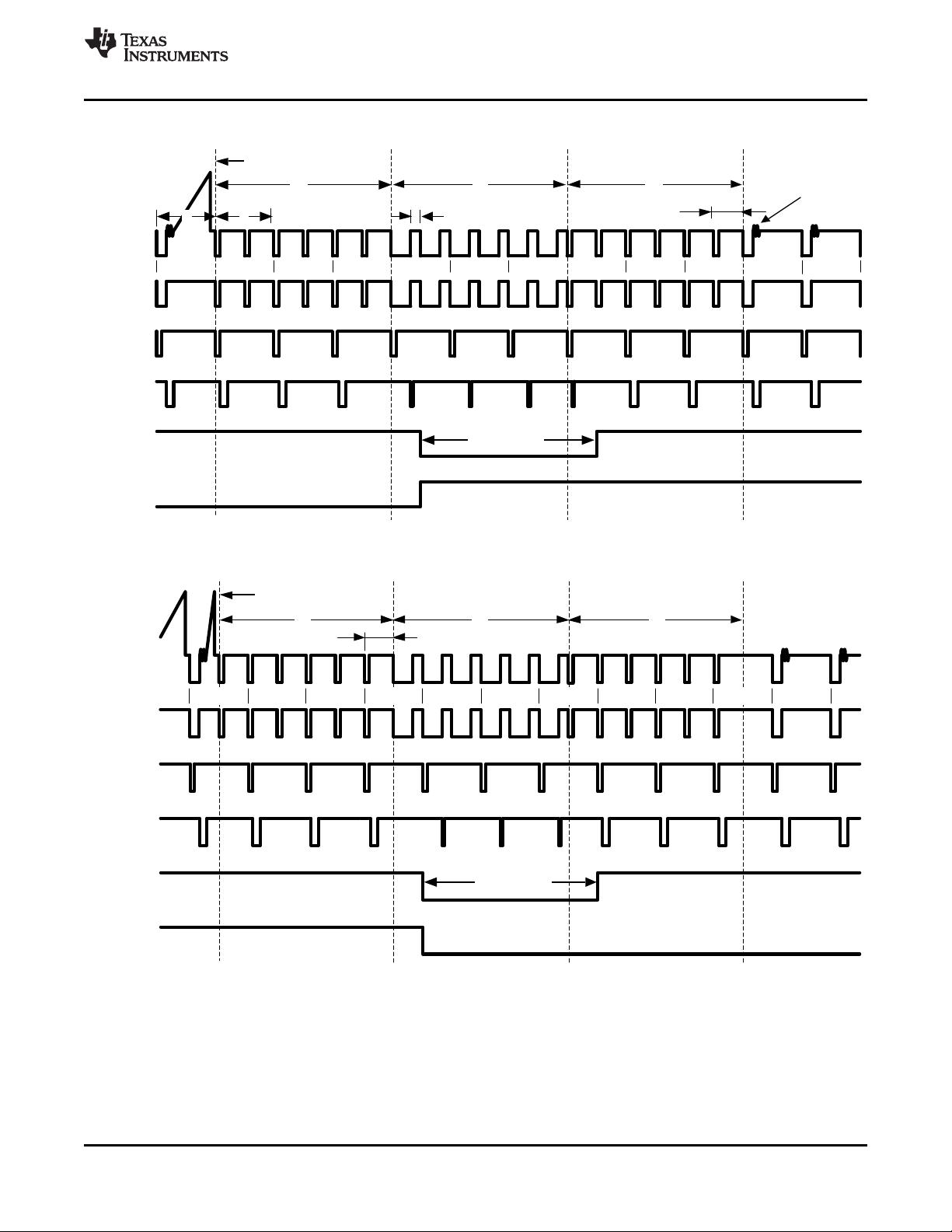

SDTV Vertical Interval Timing (NTSC, PAL, 480I, 576I)

Figure 3. NTSC Odd Field Vertical Interval

Figure 4. NTSC Even Field Vertical Interval

Copyright © 2006–2013, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Links: LMH1981

剩余25页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3119

- 资源: 5370

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 5152单片机proteus仿真和源码用定时器T0的中断控制1位LED闪烁

- 这是用于在 Akka 集群中复制数据的库的早期预览 它是一个复制的内存数据存储,支持低延迟和高可用性 要求

- 基于ketama算法和eredis项目的redis erlang驱动,主要以一致性hash的方式存储数据,做到key的分布式存储

- 2024五一杯B题要点和难点建模解析

- 贪吃蛇小项目的源代码包含snake.c,snake.h,snaketest.c

- 一款极简的截图工具(支持 Win,Mac,Linux)

- 基于SpringBoot + SSM实现的HIS医院信息管理系统

- 基于Springboot+mybatisplus+Layui+mysql制作的图书管理系统

- sql-lap注入靶场

- 803916326552715醒图v9.7.0解锁会员版.apk

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功