没有合适的资源?快使用搜索试试~ 我知道了~

TI-LMH1219.pdf

需积分: 10 0 下载量 185 浏览量

2022-11-30

23:02:41

上传

评论 4

收藏 2.44MB PDF 举报

温馨提示

试读

56页

TI-LMH1219.pdf

资源推荐

资源详情

资源评论

Control Logic

Power

Management

OUT0±

OUT1±

Single 2.5 V

or

Dual 2.5 V and 1.8 V

Control

Pins

Serial

Interface

SPI

or

SMBus

Lock

Indicator

OUT_MUX

100-Ÿ

Driver

100-Ÿ

Driver

LDO

2

2

Reclocker

with

Integrated

LoopFilter,

EyeMon

Data

Clock

IN_MUX

SE 75 Ÿ

Term

Cable

EQ

IN0±

2

Diff 100 Ÿ

Term

PCB

EQ

IN1±

2

VDD_LDO

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

Reference

Design

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: SNLS530

LMH1219

ZHCSIC9D –APRIL 2016–REVISED JUNE 2018

LMH1219 具具有有集集成成时时钟钟恢恢复复器器的的低低功功耗耗 12G UHD 自自适适应应电电缆缆均均衡衡器器

1

1 特特性性

1

• 支持 ST-2082-1(12G)、ST-2081-1(6G)、ST-424

(3G)、ST-292(HD) 和 ST-259(SD)

• 支持适用于 SMPTE 2022-5/6 的 SFF8431 (SFP+)

• 兼容 DVB-ASI 和 AES10 (MADI)

• 集成的无基准时钟恢复器锁定至 SMPTE 和 10GbE

速率:11.88Gbps、5.94Gbps、2.97Gbps、

1.485Gbps 或经 1.001 分频的子速率、270Mbps

和 10.3125Gbps

• 在输入 0 (IN0) 端具有自适应电缆均衡器

• 电缆长度 (Belden 1694A):

– 11.88Gbps (4Kp60 UHD) 时 75m

– 5.94Gbps (UHD) 时 120m

– 2.97Gbps (FHD) 时 200m

– 1.485Gbps (HD) 时 280m

– 270 Mbps (SD) 时 600m

• 输入 1 (IN1) 上具有自适应电路板走线均衡器

• 低功耗:250mW(典型值)

• 省电模式:16mW

• 集成输入回波损耗网络

• 2:1 输入多路复用,1:2 扇出输出,具有去加重功能

• 支持信号分离器模式(–6dB 启动幅值)

• 片上回路滤波器电容和眼图监视器

• 由 2.5V 单电源或片上 1.8V 稳压器供电

• 可通过控制引脚、SPI 或者 SMBus 接口进行配置

• 4mm×4mm 24 引脚 QFN 封装

• 工作温度范围:-40°C 至 +85°C

2 应应用用

• 兼容 SMPTE 的串行数字接口

• UHDTV/4K/8K/HDTV/SDTV 视频

• 广播视频路由器、交换机、分布式放大器和监视器

• 数字视频处理和编辑

• 10GbE - SDI 媒体网关

3 说说明明

LMH1219 是一款具有集成时钟恢复器的低功耗双输入

双输出自适应均衡器。该器件支持高达 11.88Gbps 的

SMPTE 视频速率以及基于 IP 传输的 10GbE 视频,

能够应用于 4K/8K 超高清 (UHD) 应用至 RTN。IN0 端

的远距离自适应电缆均衡器设计用于均衡通过 75Ω 同

轴电缆传输的数据,可在较宽的传输速率下运行,支持

的速率范围为 125Mbps 到 11.88Gbps。IN1 上的自适

应电路板走线均衡器与 SFF-8431 兼容,并且支持

SMPTE 和 10GbE 数据速率。

集成时钟恢复器可削弱高频抖动并且提供出色的信号完

整性。该器件的高输入抖动容差改善了时序裕度。时钟

恢复器内置有回路滤波器,运行时无需精准的输入基准

时钟。非破坏性眼图监视器支持实时测量串行数据,从

而简化系统调试并加速电路板调通。

凭借集成的 2:1 复用和 1:2 扇出电路,该器件能够灵活

输出多种视频信号。输出驱动器提供可编程的去加重功

能,用于补偿其输出端的电路板走线损失。集成式回波

损耗网络在所有数据传输速率下均可满足严格的

SMPTE 规范要求。LMH1219 典型的功耗值为

250mW。无输入信号时,功耗会进一步降至 16mW。

LMH1219 与 LMH1226(12G UHD 时钟恢复器)以及

LMH0324(3G 自适应电缆均衡器)引脚兼容。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

LMH1219 QFN (24) 4.00mm × 4.00mm

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品

附录。

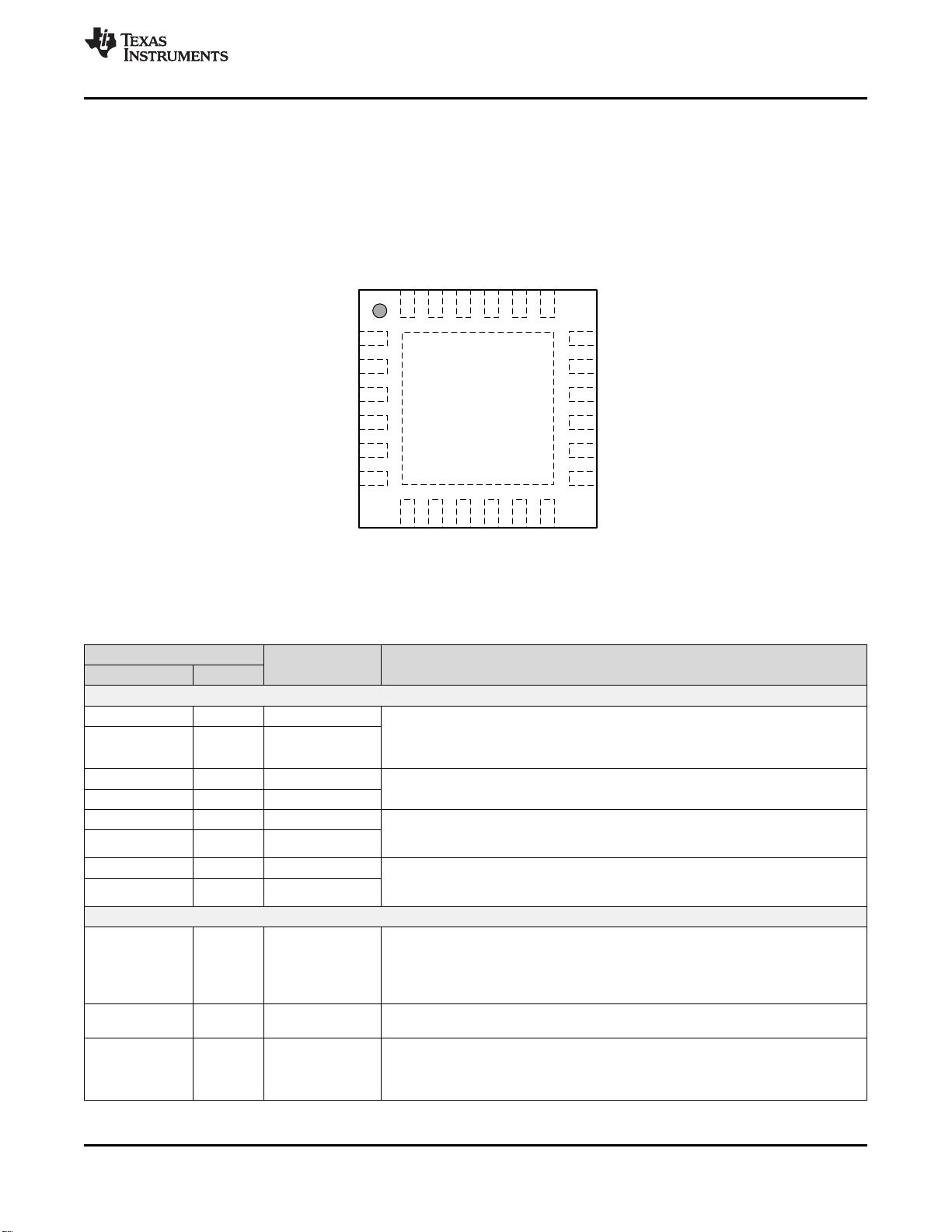

简简化化框框图图

2

LMH1219

ZHCSIC9D –APRIL 2016–REVISED JUNE 2018

www.ti.com.cn

Copyright © 2016–2018, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 5

6.1 Absolute Maximum Ratings ...................................... 5

6.2 ESD Ratings ............................................................ 5

6.3 Recommended Operating Conditions....................... 5

6.4 Thermal Information.................................................. 6

6.5 Electrical Characteristics........................................... 6

6.6 Recommended SMBus Interface AC Timing

Specifications........................................................... 12

6.7 Serial Parallel Interface (SPI) AC Timing

Specifications........................................................... 13

6.8 Typical Characteristics............................................ 14

7 Detailed Description............................................ 16

7.1 Overview ................................................................. 16

7.2 Functional Block Diagram ....................................... 16

7.3 Feature Description................................................. 17

7.4 Device Functional Modes........................................ 22

7.5 LMH1219 Register Map.......................................... 27

8 Application and Implementation ........................ 40

8.1 Application Information............................................ 40

8.2 Typical Application .................................................. 40

9 Power Supply Recommendations...................... 47

10 Layout................................................................... 47

10.1 PCB Layout Guidelines......................................... 47

10.2 Layout Example .................................................... 49

11 器器件件和和文文档档支支持持 ..................................................... 50

11.1 接收文档更新通知 ................................................. 50

11.2 社区资源................................................................ 50

11.3 商标 ....................................................................... 50

11.4 静电放电警告......................................................... 50

11.5 术语表 ................................................................... 50

12 机机械械、、封封装装和和可可订订购购信信息息....................................... 50

4 修修订订历历史史记记录录

Changes from Revision C (October 2017) to Revision D Page

• 首次公开发布的完整生产版产品说明书;添加 TI 参考设计顶部导航图标链接 ....................................................................... 1

• Moved LMH1219 and LMH0324 Compatibility to Application Information ........................................................................... 40

Changes from Revision B (February 2017) to Revision C Page

• 添加封装图............................................................................................................................................................................ 50

Changes from Revision A (May 2016) to Revision B Page

• Changed eq_en_bypass bit description from "Gain Stages 3 and 4" to "Gain Stages 2 and 3" ........................................ 29

• Changed bit location of IN1 Carrier Detect Power Down Control from Reg 0x13[5] to Reg 0x15[6] .................................. 29

Changes from Original (April 2016) to Revision A Page

• Deleted min and max VOD_DE amplitude specification when VOD_DE = Level F ............................................................. 9

• Changed typical VOD_DE amplitude specifications for Levels F, R, and L .......................................................................... 9

• Changed DEM value and DEM register settings in Table 5 to match correct VOD_DE pin logic levels ............................. 20

• 已添加 new row for VOD = 5, DEM = 5 setting in 表 10 ..................................................................................................... 43

1

2

3

4

5

6

18

17

16

15

14

13

19

20

21

22

23

24

12

11

10

9

8

7

VDD_CDR

IN0+ OUT0+

OUT0-

VSS

OUT1+

OUT1-

IN0-

VSS

IN1+

IN1-

MODE_SEL

VIN

VDD_LDO

VDDIO

SCK_SCL

MISO_ADDR1

OUT_CTRL

SS_N_ADDR0

IN_OUT_SEL

VSS

MOSI_SDA

VOD_DE

LOCK_N

LMH1219

EP = VSS

3

LMH1219

www.ti.com.cn

ZHCSIC9D –APRIL 2016–REVISED JUNE 2018

Copyright © 2016–2018, Texas Instruments Incorporated

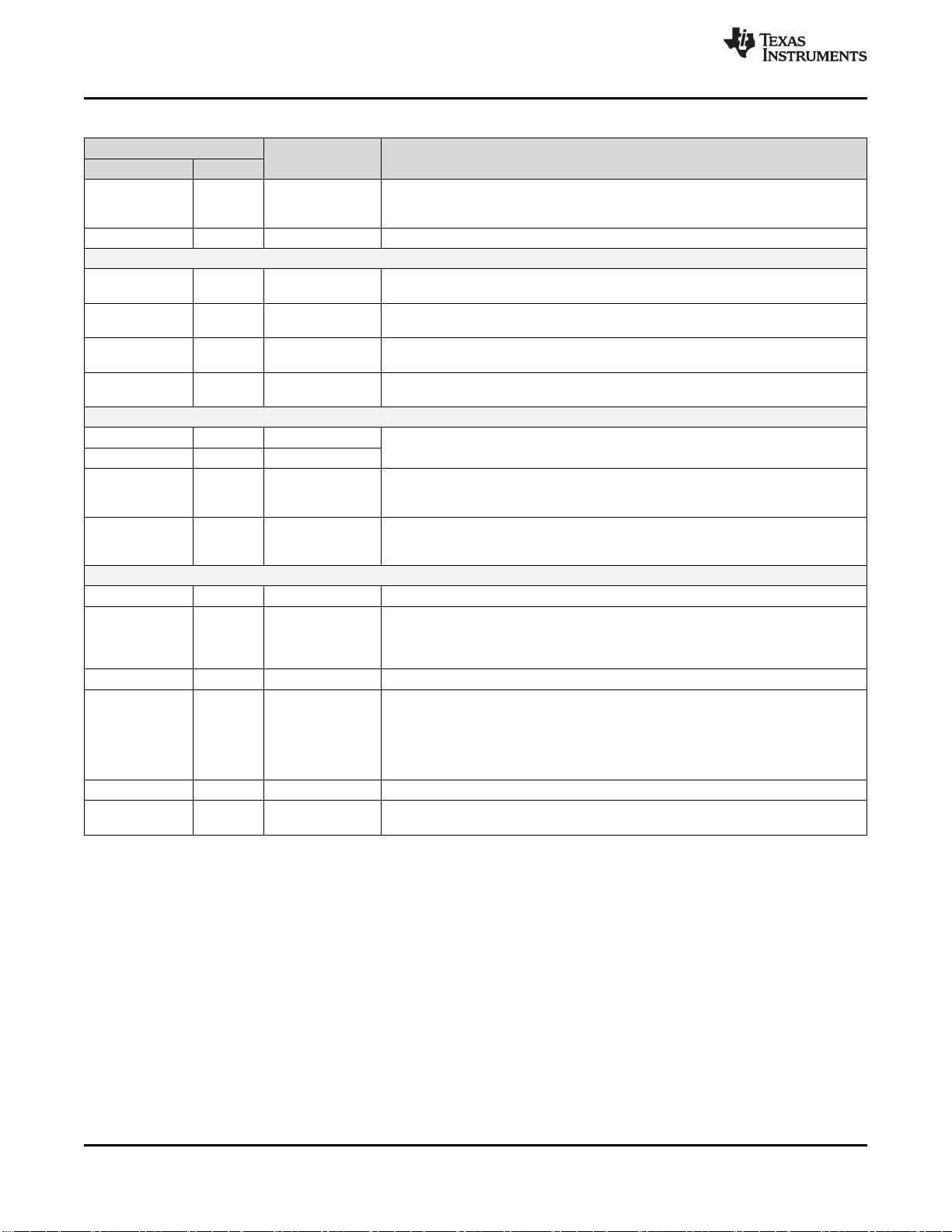

(1) I = Input, O = Output, IO = Input or Output, OD = Open Drain, LVCMOS = 2-State Logic, 4-LEVEL = 4-State Logic

5 Pin Configuration and Functions

RTW Package

24-Pin QFN

Top View

Pin Functions

PIN

I/O

(1)

DESCRIPTION

NAME NO.

High Speed Differential I/O'S

IN0+ 1 I, Analog Single-ended complementary inputs, 75-Ω internal termination from IN0+ or IN0- to

internal common mode voltage and return loss compensation network. Requires

external 4.7-µF AC coupling capacitors. IN0+ is the 75-Ω input port for the adaptive

cable equalizer in SMPTE video applications.

IN0- 2 I, Analog

IN1+ 4 I, Analog

Differential complementary inputs with internal 100-Ω termination. Requires external

4.7-µF AC coupling capacitors for SMPTE and 10 GbE.

IN1- 5 I, Analog

OUT0+ 18 O, Analog Differential complementary outputs with 100-Ω internal termination. Requires external

4.7-µF AC coupling capacitors. Output driver OUT0± can be disabled under user

control.

OUT0- 17 O, Analog

OUT1+ 15 O, Analog Differential complementary outputs with 100-Ω internal termination. Requires external

4.7-µF AC coupling capacitors. Output driver OUT1± can be disabled under user

control.

OUT1- 14 O, Analog

Control Pins

LOCK_N 12 O, LVCMOS, OD

LOCK_N is the reclocker lock indicator for the selected input. LOCK_N is pulled LOW

when the reclocker has acquired locking condition. LOCK_N is an open drain output,

3.3 V tolerant, and requires an external 2-kΩ to 5-kΩ pull-up resistor to logic supply.

LOCK_N pin can be re-configured to indicate CD_N (Carrier Detect) or INT_N

(Interrupt) for IN0 or IN1 through register programming.

IN_OUT_SEL 8 I, 4-LEVEL

IN_OUT_SEL selects the signal flow at input ports to output ports. See Table 2 for

details. This pin setting can be overridden by register control.

OUT_CTRL 19 I, 4-LEVEL

OUT_CTRL selects the signal flow from the selected IN port to OUT0± and OUT1±. It

selects reclocked data, reclocked data and clock, bypassed reclocker data (equalized

data to output driver), or bypassed equalizer and reclocker data. See Table 4 for

details. This pin setting can be overridden by register control.

4

LMH1219

ZHCSIC9D –APRIL 2016–REVISED JUNE 2018

www.ti.com.cn

Copyright © 2016–2018, Texas Instruments Incorporated

Pin Functions (continued)

PIN

I/O

(1)

DESCRIPTION

NAME NO.

VOD_DE 11 I, 4-LEVEL

VOD_DE selects the driver output amplitude and de-emphasis level for both OUT0±

and OUT1±. See Table 5 for details. This pin setting can be overridden by register

control.

MODE_SEL 6 I, 4-LEVEL MODE_SEL enables SPI or SMBus serial control interface. See Table 6 for details.

Serial Control Interface (SPI Mode), MODE_SEL = F (Float)

SS_N 7 I, LVCMOS

SS_N is the Slave Select. When SS_N is at logic Low, it enables SPI access to the

LMH1219 slave device. SS_N is a LVCMOS input referenced to VDDIO.

MISO 20 O, LVCMOS

MISO is the SPI control serial data output from the LMH1219 slave device. MISO is a

LVCMOS output referenced to VDDIO.

MOSI 10 I, LVCMOS

MOSI is used as the SPI control serial data input to the LMH1219 slave device. MOSI

is LVCMOS input referenced to VDDIO.

SCK 21 I, LVCMOS

SCK is the SPI serial input clock to the LMH1219 slave device. SCK is LVCMOS

referenced to VDDIO.

Serial Control Interface (SMBus MODE) , MODE_SEL = L (1 kΩ to VSS)

ADDR0 7 Strap, 4-LEVEL

ADDR[1:0] are SMBus address straps to select one of the 16 supported SMBus

addresses. ADDR[1:0] are 4-level straps and are read into the device at power up.

ADDR1 20 Strap, 4-LEVEL

SDA 10 IO, LVCMOS, OD

SDA is the SMBus bi-directional open drain SDA data line to or from the LMH1219

slave device. SDA is an open drain IO and tolerant to 3.3 V. SDA requires an external

2-kΩ to 5-kΩ pull-up resistor to the SMBus termination voltage.

SCL 21 I, LVCMOS, OD

SCL is the SMBus input clock to the LMH1219 slave device. It is driven by a

LVCMOS open drain driver from the SMBus master. SCL is tolerant to 3.3 V and

requires an external 2-kΩ to 5-kΩ pull up resistor to the SMBus termination voltage.

Power

VSS 3, 9, 16 I, Ground Ground reference.

VIN 24 I, Power

VIN is connected to an external power supply. It accepts either 2.5 V ± 5% or 1.8 V ±

5%. When VIN is powered from 2.5 V, VDD_LDO is the output of an on-chip LDO

regulator. For lower power operation, both VIN and VDD_LDO should be connected

to a 1.8 V supply.

VDDIO 22 I, Power VDDIO powers the LVCMOS IO and 4-level input logic and connects to 2.5 V ± 5%.

VDD_LDO 23 IO, Power

VDD_LDO is the output of the internal 1.8 V LDO regulator when VIN is connected to

a 2.5 V supply. VDD_LDO output requires external 1-µF and 0.1-µF bypass

capacitors to VSS. The internal LDO is designed to power internal circuitry only.

VDD_LDO is an input when VIN is powered from 1.8 V for lower power operation.

When VIN is connected to a 1.8 V supply, both VIN and VDD_LDO should be

connected to a 1.8 V supply.

VDD_CDR 13 I, Power VDD_CDR powers the reclocker circuitry and connects to 2.5 V ± 5% supply.

EP I, Ground

EP is the exposed pad at the bottom of the QFN package. The exposed pad must be

connected to the ground plane through a via array. See 图 41 for details.

5

LMH1219

www.ti.com.cn

ZHCSIC9D –APRIL 2016–REVISED JUNE 2018

Copyright © 2016–2018, Texas Instruments Incorporated

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) For soldering specifications, see application note SNOA549.

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)(2)

MIN MAX UNIT

Supply Voltage for 2.5 V Mode (VDD_CDR, VIN, VDDIO) –0.5 2.75 V

Supply Voltage for 1.8 V Mode (VIN, VDD_LDO) –0.5 2.0 V

4-Level Input/Output Voltage (IN_OUT_SEL, OUT_CTRL, VOD_DE, MODE_SEL, ADDR0,

ADDR1)

–0.5 2.75 V

SMBus Input/Output Voltage (SDA, SCL) –0.5 4.0 V

SPI Input/Output Voltage (SS_N, MISO, MOSI, and SCK) –0.5 2.75 V

Input Voltage (IN0±, IN1±) –0.5 2.75 V

Input Current (IN0±, IN1±) –30 30 mA

Junction Temperature 125 °C

Storage temperature -65 150 °C

(1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with

less than 500 V HBM is possible with the necessary precautions. Pins listed as ±4500 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with

less than 250 V CDM is possible with the necessary precautions. Pins listed as ±1500 V may actually have higher performance.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

±4500

V

Charged-device model (CDM), per JEDEC specification JESD22-C101

(2)

±1500

(1) In Single Supply Mode, the VIN, VDDIO and VDD_CDR supplies are 2.5 V. The VDD_LDO is the 1.8 V LDO output of an internal LDO

regulator, the VDD_LDO pin should not be connected to any external supply voltage.

(2) In Dual Supply Mode, the VIN and VDD_LDO are connected to a 1.8 V supply, while the VDD_CDR and VDDIO supplies are 2.5 V.

(3) In Dual Supply Mode, the VDDIO and VDD_CDR supply should be powered before or at the same time as VIN and VDD_LDO = 1.8 V.

(4) The sum of the DC supply voltage and AC supply noise should not exceed the recommended supply voltage range.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

Single Supply

Mode

(1)

VIN, VDDIO, VDD_CDR to VSS 2.375 2.5 2.625 V

Dual Supply

Mode

(2)(3)

VIN, VDD_LDO to VSS 1.71 1.8 1.89

V

VDD_CDR, VDDIO to VSS 2.375 2.5 2.625

VDD

SMBUS

SMBus: SDA, SCL Open Drain Termination Voltage 2.375 3.6 V

V

IN0_LAUNCH

Source Launch Amplitude before coaxial

cable

Normal mode 0.72 0.8 0.88

Vp-p

Splitter mode 0.36 0.4 0.44

V

IN1_LAUNCH

Source Differential Launch Amplitude

before 5-inch board trace 300 850

mVp-p

before 20-inch board trace 650 1000

T

JUNCTION

Operating Junction Temperature 100 °C

T

AMBIENT

Ambient Temperature –40 25 85 °C

NTps

max

(4)

Maximum Supply Noise Tolerance

50 Hz to 1 MHz, sinusoidal <20

mVp-p

1.1 MHz to 6 GHz,

sinusoidal

<10

剩余55页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3119

- 资源: 5348

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 三菱PLC(Mitsubishi)通讯协议的C#实现,支持FX、Q系列的ASCII-3E、BIN-3E、FX串口格式

- 五一建模20242024

- rainy-day.jpg

- IMG_20240501_171218.jpg

- Swift-内购封装swift版本

- 经典CNN网络之ResNet 图像分类网络实战项目:7种小麦叶片病害分类(迁移学习)

- Java毕设之ssm010基于ssm的新能源汽车在线租赁管理系统+vue.rar

- Java毕设之ssm009毕业生就业信息统计系统+vue.rar

- Java毕设之ssm008医院门诊挂号系统+jsp.rar

- Java毕设之ssm007亚盛汽车配件销售业绩管理统+jsp.rar

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功