没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS99R421-Q1.pdf

试读

26页

需积分: 0 0 下载量 7 浏览量

更新于2023-02-07

4

收藏 918KB PDF 举报

FPD-Link转换器DS99R421-Q1

FPD-Link转换器DS99R421-Q1是一款由德州仪器(TI)公司推出的高速串行转换器,旨在将FPD-Link信号转换为FPD-Link II信号。该器件具有多种特性,能够满足不同应用场景的需求。

功能描述:

DS99R421-Q1的主要功能是将FPD-Link信号转换为FPD-Link II信号,实现高速数据传输。该器件可以将3个LVDS数据信号和1个LVDS时钟信号转换为单个LVDS串行流,嵌入时钟信息。该串行流可以通过单个差分对PCB迹线和电缆传输,解决了LVDS数据输入和LVDS时钟路径之间的时延问题。

特性:

FPD-Link转换器DS99R421-Q1具有以下特性:

* 用户可调整的预加重驱动能力,通过外部电阻在LVDS输出端实现

* 能够驱动长达10米的屏蔽双绞线电缆

* 支持AC耦合数据传输

* 集成了100Ω的LVDS终端电阻

* 电源关闭控制

* 可以与DS90UR124进行BIST测试以验证链路完整性

* 所有LVCMOS输入和控制引脚具有内部下拉电阻

* Schmitt触发器输入OS[2:0]以最小化不稳定条件

* 输出tri-state通过DEN输出使能

* PLL滤波器集成在芯片内

* 电源电压范围为3.3V ± 10%

* 工作温度范围为-40°C到+105°C

* 高达8kV的ESD耐受性

* 符合ISO 10605 ESD和AEC-Q100标准

应用场景:

FPD-Link转换器DS99R421-Q1广泛应用于各类高速数据传输系统,例如高分辨率显示器、机器视觉系统、医疗成像设备等。在这些应用场景中,FPD-Link转换器DS99R421-Q1能够提供高速、可靠的数据传输解决方案。

FPD-Link转换器DS99R421-Q1是一款功能强大、性能出色的高速串行转换器,能够满足不同应用场景的需求,广泛应用于高速数据传输系统。

DS99R421

www.ti.com

SNLS264D –JUNE 2007–REVISED APRIL 2013

5-43 MHz FPD-Link LVDS (3 Data + 1 Clock) to FPD-Link II LVDS (Embedded Clock DC-

Balanced) Converter

Check for Samples: DS99R421

1

FEATURES

DESCRIPTION

The DS99R421 converts a FPD-Link input with 4

2

• 5 MHz–43 MHz Embedded Clock & DC-

non-DC Balanced LVDS (3 LVDS Data + LVDS

Balanced Data Transmission (21 Total LVDS

Clock) plus 3 over-sampled low speed control bits

Data Bits Plus 3 Low Speed LVCMOS Data

into a single LVDS DC-balanced serial stream with

Bits)

embedded clock information. This single serial stream

• User Adjustable Pre-Emphasis Driving Ability

simplifies transferring the 24-bit bus over a single

Through External Resistor on LVDS Outputs

differential pair of PCB traces and cable by

eliminating the skew problems between the 3 parallel

and Capable to Drive up to 10 Meters Shielded

LVDS data inputs and LVDS clock paths. It saves

Twisted-Pair Cable

system cost by narrowing 4 LVDS pairs to 1 LVDS

• Supports AC-Coupling Data Transmission

pair that in turn reduce PCB layers, cable width,

• 100Ω Integrated Termination Resistor at LVDS

connector size, and pins.

Input

The DS99R421 incorporates a single serialized LVDS

• Power-Down Control

signal on the high-speed I/O. Embedded clock LVDS

• Available @SPEED BIST to DS90UR124 to

provides a low power and low noise environment for

Validate Link Integrity

reliably transferring data over a serial transmission

path. By optimizing the converter output edge rate for

• All LVCMOS Inputs & Control Pins Have

the operating frequency range EMI is further reduced.

Internal Pulldown

In addition the device features pre-emphasis to boost

• Schmitt Trigger Inputs on OS[2:0] to Minimize

signals over longer distances using lossy cables.

Metastable Conditions

Internal DC balanced encoding is used to support

• Outputs Tri-Stated Through DEN

AC-Coupled interconnects.

• On-Chip Filters for PLLs

• Power Supply Range 3.3V ± 10%

• Automotive Temperature Range −40°C to

+105°C

• Greater Than 8kV ESD Tolerance

• Meets ISO 10605 ESD and AEC-Q100

Compliance

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2007–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

100:

Differential

PCB Traces

DOUT-

R

T

=

100

:

R

T

=

100

:

RIN-

Rx - DESERIALIZER

DOUT+ RIN+

DS

90

UR

124

DS

99

R421

100

:

100

:

100

:

100:

LVDS

DATA0

LVDS

DATA1

LVDS

DATA2

LVDS

CLK

(5 MHz to 43 MHz)

GUI

3

LVDS NON

-

DC Balanced

OS

[

2

:

0

]

STP

(Up to 10 meters)

DEN

Standard 4 LVDS - to - 1 LVDS Tx ± Converter

PLL

DOUT-

DOUT+

DeSerializer

Parallel to Serial

DC Balance Encoder

PRE

21 Bits

Parallel

Data

DS

99

R421

100

:

100

:

100:

100:

RxIN0-

(5 MHz to 43 MHz)

3

LVDS NON-DC Balanced

OS

[

2

:

0

]

VODSEL

RxIN0+

RxIN1-

RxIN1+

RxIN2-

RxIN2+

RxCLKIN-

RxCLKIN+

PWDNB

DS99R421

SNLS264D –JUNE 2007–REVISED APRIL 2013

www.ti.com

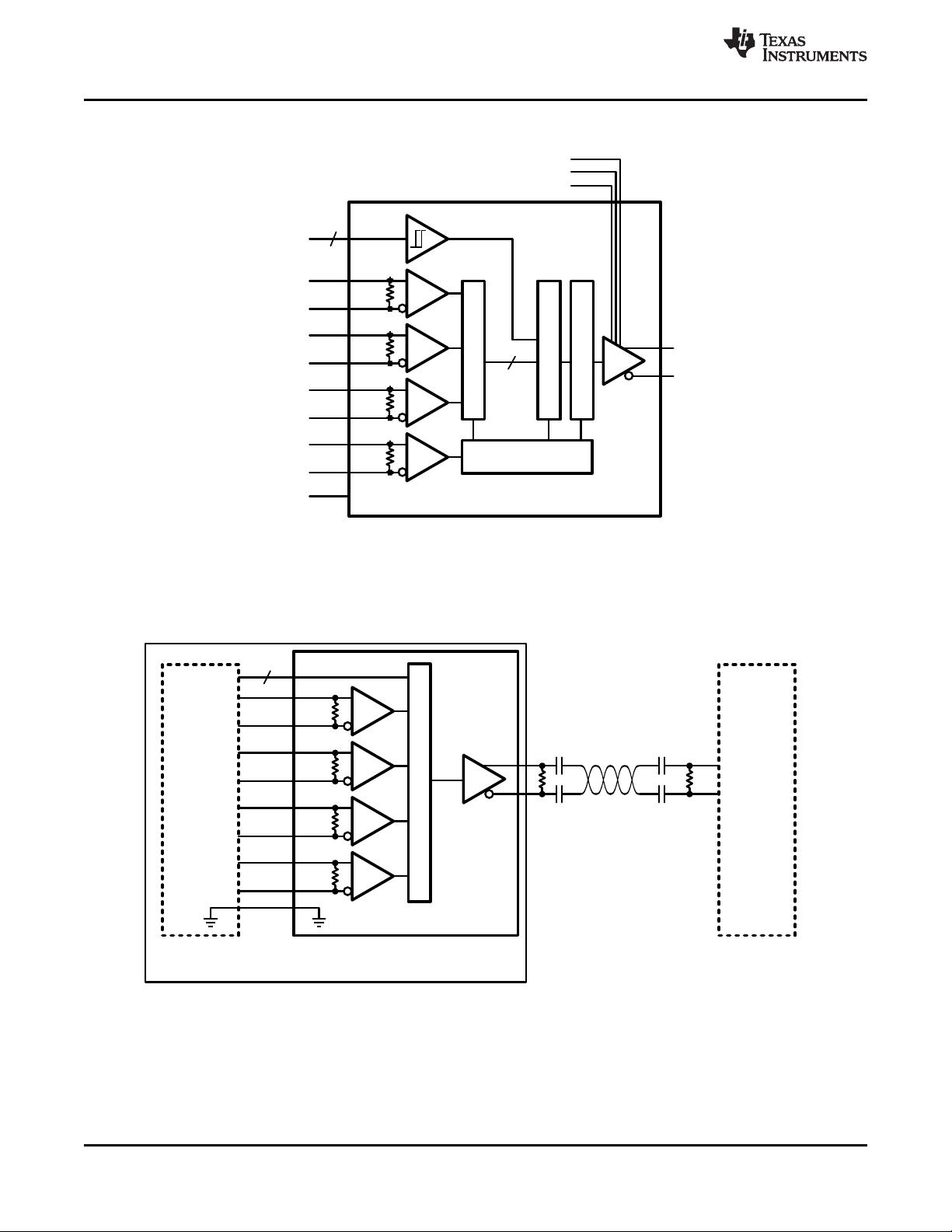

Block Diagram

Figure 1. Block Diagram

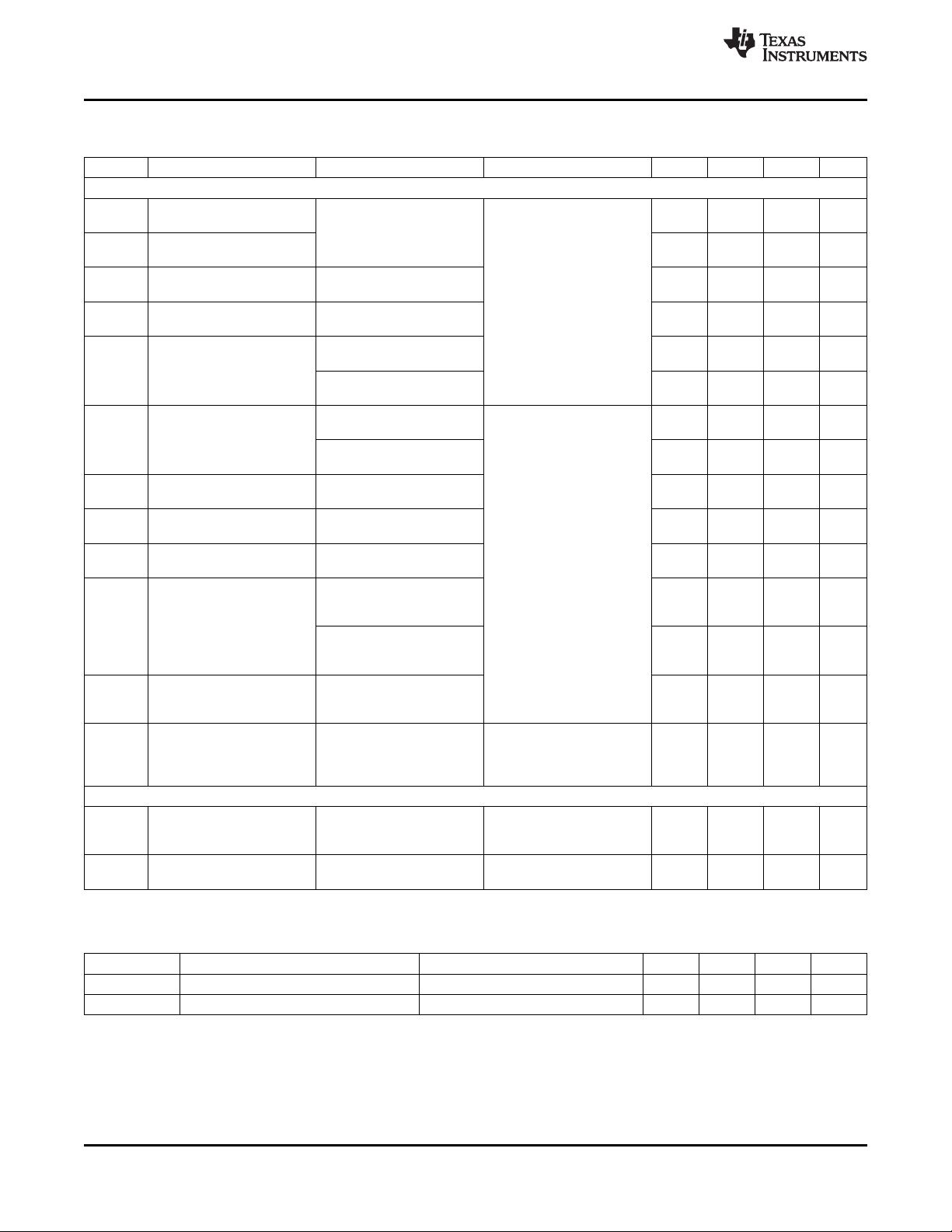

Application Overview

Figure 2. Typical Application Diagram

2 Submit Documentation Feedback Copyright © 2007–2013, Texas Instruments Incorporated

Product Folder Links: DS99R421

DS99R421

www.ti.com

SNLS264D –JUNE 2007–REVISED APRIL 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings

(1)(2)

Supply Voltage (V

DD

) −0.3V to +4V

LVCMOS Input Voltage −0.3V to (V

DD

+0.3V)

LVCMOS Output Voltage −0.3V to (V

DD

+0.3V)

LVDS Receiver Input Voltage −0.3V to +3.9V

LVDS Driver Output Voltage −0.3V to +3.9V

LVDS Output Short Circuit Duration 10 ms

Junction Temperature +150°C

Storage Temperature −65°C to +150°C

Lead Temperature (Soldering, 4 seconds) +260°C

Package De-rating: DS99R421 − 36L WQFN 1/θ

JA

°C/W above +25°C

Maximum Package Power Dissipation

θ

JA

37.6 (4L

(3)

); 83.7 (2L

(3)

)°C/W

Capacity

θ

JC

3.1 (2/4L

(3)

) °C/W

HBM ≥±8 kV

ESD Rating

ISO10605 DS99R421 meets ISO10605

Contact Discharge, DOUT± ±10 kV

R

D

= 2 kΩ, C

S

= 150/330 pF

Air Discharge, DOUT± ±25 kV

(1) “Absolute Maximum Ratings” indicate limits beyond which damage to the device may occur, including inoperability and degradation of

device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or

other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating

Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

(3) JEDEC

Recommended Operating Conditions

Min Nom Max Units

Supply Voltage (V

DD

) 3.0 3.3 3.6 V

Operating Free Air Temperature (T

A

) −40 +25 +105 °C

Input Clock Rate, RxCLKIN± 5 43 MHz

Supply Noise (V

DDp-p

) ±100 mV

P-P

Receiver Input Range 0 V

DD

V

Electrical Characteristics

(1)(2)(3)

Over recommended operating supply and temperature ranges unless otherwise specified.

Symbol Parameter Conditions Pin/Freq. Min Typ Max Units

LVCMOS & SCHMITT-TRIGGER INPUT DC SPECIFICATIONS

V

IH

High Level Input Voltage PWDNB, DEN, VODSEL, 2.0 V

DD

V

BISTEN

V

IL

Low Level Input Voltage GND 0.8 V

V

CL

Input Clamp Voltage I

CL

= −18 mA −0.9 −1.5 V

I

IN

Input Current V

IN

= 0V or 3.6V −10 +10 µA

V

TH

+ High Level Input Voltage OS[2:0] 2.0 V

(Schmitt-triggered Inputs)

V

TH

− High Level Input Voltage 0.8 V

V

H

Hysteresis Voltage V

TH

+ – V

TH

− 200 400 600 mV

(1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as

otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and

are not ensured.

(2) Typical values represent most likely parametric norms at 3.3V, Ta = +25 degC, and at the Recommended Operation Conditions at the

time of product characterization and are not ensured.

(3) Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground

except V

OD

, ΔV

OD

, V

TH

and V

TL

which are differential voltages.

Copyright © 2007–2013, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: DS99R421

DS99R421

SNLS264D –JUNE 2007–REVISED APRIL 2013

www.ti.com

Electrical Characteristics

(1)(2)(3)

(continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

Symbol Parameter Conditions Pin/Freq. Min Typ Max Units

LVDS DC SPECIFICATIONS

V

TH

Differential Threshold High V

CM

= 1.2V LVDS differential Inputs:

+100 mV

Voltage RxIN0±, RxIN1±, RxIN2±,

RxCLKIN±

V

TL

Differential Threshold Low

−100 mV

Voltage

|V

ID

| Differential Input Voltage

100 600 mV

Swing

V

CM

Common Mode Voltage V

DD

−

0.525 1.2 mV

(V

ID

/2)

I

IN

Input Current V

IN

= +2.4V,

−10 +10 µA

V

DD

= 3.6V

V

IN

= 0V,

-10 +10 µA

V

DD

= 3.6V

V

OD

Output Differential Voltage R

T

= 100Ω LVDS differential Outputs:

380 500 630 mV

(Figure 10) VODSEL = L DOUT±

R

T

= 100Ω

650 900 1150 mV

VODSEL = H

ΔV

OD

Output Differential Voltage R

T

= 100Ω

10 50 mV

Unbalance

V

OS

Output Voltage Offset R

T

= 100Ω

1.0 1.2 1.5 V

PRE = H (off)

ΔV

OS

Output Voltage Offset R

T

= 100Ω

5 50 mV

Difference PRE = H (off)

I

OS

Output Short Circuit Current DOUT± = 0V

VODSEL = L −2 −8 mA

PRE = H (off)

DOUT± = 0V

VODSEL = H −7 −13 mA

PRE = H (off)

I

OZ

TRI-STATE Output Current PWDNB = 0V,

DOUT± = 0V OR V

DD

−10 ±1 +10 µA

(inputs not toggling)

R

T

Internal Input Termination RxIN:

Resistance across RxIN(2:0)+ &

90 105 130 Ω

RxIN(2:0)−, and across

RxCLKIN+ & RxCLKIN−

CONVERTER SUPPLY CURRENT

I

DD

Total Supply Current R

T

= 100Ω f = 43 MHz

(includes load current) CHECKERBOARD pattern 95 130 mA

PRE = 6 KΩ (Figure 3)

I

DDTZ

Supply Current Power-down PWDNB = 0V

2 50 µA

(inputs not toggling)

Receiver Input Timing Requirements

Over recommended operating supply and temperature ranges unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Units

t

RCIH

Receiver Clock Input High Time Referenced to rising edge of RxCLKIN 0.35T 0.57T ns

t

RCIL

Receiver Clock Input Low Time Referenced to rising edge of RxCLKIN 0.43T 0.65T ns

4 Submit Documentation Feedback Copyright © 2007–2013, Texas Instruments Incorporated

Product Folder Links: DS99R421

剩余25页未读,继续阅读

资源推荐

资源评论

166 浏览量

107 浏览量

134 浏览量

2023-02-07 上传

2023-02-01 上传

118 浏览量

2023-02-01 上传

2023-02-01 上传

2023-02-01 上传

147 浏览量

177 浏览量

2023-02-01 上传

资源评论

不觉明了

- 粉丝: 6600

- 资源: 5764

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 4b126基于Springboot+vue的新闻发布管理系统_springboot+vue.zip

- 4b128高校院系学生信息管理系统设计与实现_springboot+vue.zip

- 4b125智慧旅游系统_springboot+vue.zip

- 4b132基于软件研发过程中的缺陷管理系统的设计与实现_springboot+vue.zip

- 4b131小区车辆管理系统-springboot+vue.zip

- 4b129基于springboot+vue的宠物寄养系统.zip

- 4b134校园车辆管理系统_springboot+vue.zip

- Windows 7 离线补丁包 - UpdatePack7R2(24.12.12)珍藏品

- CRT8.7中文版,解压直接使用,不用安装

- 智能合约技术:基于Solidity的数据存储与访问权限管理

- COMSOL电线缆,电磁涡流感应热仿真,集肤效应,涡流效应仿真

- 4b041考试报名系统_springboot+vue0.zip

- 2-SvgToXaml-WPF开发者实用工具

- 4b055在线考试系统_springboot+vue0.zip

- 4b050明星周边商城系统_springboot+vue0.zip

- 4b070水果蔬菜商城_springboot+vue0.zip

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功