没有合适的资源?快使用搜索试试~ 我知道了~

TI-TPS92515-Q1.pdf

需积分: 12 1 下载量 79 浏览量

2022-11-16

23:36:27

上传

评论 5

收藏 2.24MB PDF 举报

温馨提示

试读

41页

TI-TPS92515-Q1.pdf

资源推荐

资源详情

资源评论

VCC

CSN

TPS92515

SW

1

2

3

4

IADJ

PWM

COFF

GND

10

9

8

7

56 DRN

VIN

BOOT

V

OUT

V

IN

PAD

Copyright © 2016, Texas Instruments Incorporated

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: SLUSBZ6

TPS92515

,

TPS92515-Q1

,

TPS92515HV

,

TPS92515HV-Q1

ZHCSFD3A –APRIL 2016–REVISED AUGUST 2016

TPS92515x 集集成成有有 N 沟沟道道 FET、、

高高侧侧电电流流感感测测和和分分流流 FET PWM 调调光光功功能能的的 2A 降降压压 LED 驱驱动动器器

1

1 特特性性

1

• 符合 AEC-Q100 1 级标准

• 集成 290mΩ(典型值)内部 N 沟道场效应晶体管

(FET)

• 输入电压范围:

– TPS92515x:5.5V 至 42V

– TPS92515HVx:5.5V 至 65V

– 启动后工作电压低至 5.15V

• 低偏移高侧峰值电流比较器

• 高达 2A 的恒定平均电流

• 固有逐周期电流限制

• 多种调光方法

– 10,000:1 分流脉宽调制 (PWM) 调光范围

– 1000:1 PWM 调光范围

– 200:1 模拟调光范围

• 简单的恒定关断时间控制

– 无环路补偿

– 快速瞬态响应

• 散热增强型 HVSSOP 封装

• 集成热保护

2 应应用用

• 汽车照明:LED 开关矩阵 AFS 头灯,DRL,远光

灯/近光灯,雾灯,尾灯,转向信号灯,轮廓灯,售

后市场

• 工业照明:工厂自动化、飞行时间 (TOF)、电器、

零售照明、机器视觉检测、紧急出口和/或安全照

明、医用照明、舞台和场地照明

• 农业、航海和重工业照明

• 高对比度分流 FET 调光

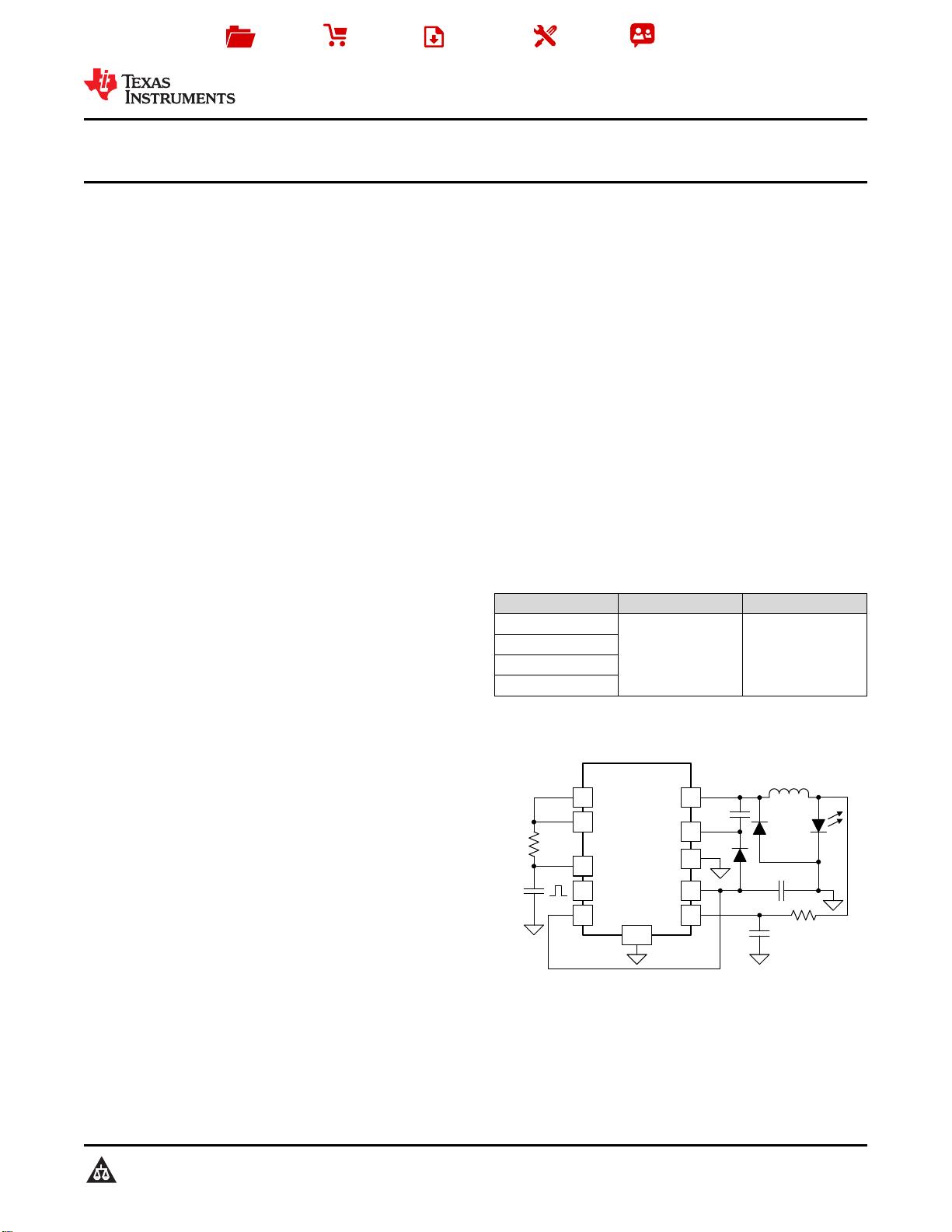

3 说说明明

TPS92515 系列器件是集成了低电阻 N 沟道金属氧化

物半导体场效应晶体管 (MOSFET) 的紧凑型单片开关

稳压器。该系列器件适用于 注重 高效率、高带宽、

PWM 和/或模拟调光以及小尺寸的高亮度 LED 照明应

用。

该稳压器利用恒定关断时间和峰值电流控制功能来运

行。工作原理十分简单:在基于输出电压的一段关断时

间后,即开始导通时间。达到电感峰值电流阈值后,导

通时间立即结束。TPS92515 器件可配置为在分流

FET 调光周期的导通和关断时间内保持恒定的纹波峰

峰值。这非常适合在整个分流 FET 调光范围内保持线

性响应。

稳态精度是在低偏移高侧比较器的支持下得到保证。可

单独使用模拟或 PWM 调光技术来调制 LED 电流,也

可同时使用这两种技术来调制 LED 电流。其他 特性

包括欠压闭锁 (UVLO)、宽输入电压操作、固有 LED

开路操作和热关断功能,其工作温度范围较宽。

TPS92515 和 TPS92515-Q1 器件的工作输入电压范

围高达 42V。TPS92515HV 和 TPS92515HV-Q1 提供

输入范围高达 65V 的高电压选项。所有器件均采用散

热增强型 10 引脚 HVSSOP 封装。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

TPS92515

HVSSOP (10) 3mm x 3mm

TPS92515-Q1

TPS92515HV

TPS92515HV-Q1

(1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。

简简化化的的降降压压 LED 驱驱动动器器应应用用

2

TPS92515

,

TPS92515-Q1

,

TPS92515HV

,

TPS92515HV-Q1

ZHCSFD3A –APRIL 2016–REVISED AUGUST 2016

www.ti.com.cn

Copyright © 2016, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Device Comparison Table..................................... 3

6 Pin Configuration and Functions......................... 3

7 Specifications......................................................... 4

7.1 Absolute Maximum Ratings ...................................... 4

7.2 ESD Ratings ............................................................ 4

7.3 Recommended Operating Conditions....................... 4

7.4 Thermal Information................................................. 4

7.5 Electrical Characteristics........................................... 5

7.6 Typical Characteristics.............................................. 7

8 Detailed Description.............................................. 9

8.1 Overview ................................................................... 9

8.2 Functional Block Diagram ......................................... 9

8.3 Feature Description................................................. 10

8.4 Device Functional Modes........................................ 21

9 Application and Implementation ........................ 22

9.1 Application Information............................................ 22

9.2 Typical Application ................................................. 22

9.3 Dos and Don'ts ....................................................... 30

10 Power Supply Recommendations ..................... 31

10.1 Input Source Direct from Battery........................... 31

10.2 Input Source from a Boost Stage ......................... 31

11 Layout................................................................... 31

11.1 Layout Guidelines ................................................. 31

11.2 Layout Example .................................................... 32

12 器器件件和和文文档档支支持持 ..................................................... 33

12.1 文档支持 ............................................................... 33

12.2 接收文档更新通知 ................................................. 33

12.3 社区资源................................................................ 33

12.4 商标 ....................................................................... 33

12.5 静电放电警告......................................................... 33

12.6 Glossary................................................................ 33

13 机机械械、、封封装装和和可可订订购购信信息息....................................... 34

4 修修订订历历史史记记录录

Changes from Original (April 2016) to Revision A Page

• 已将数据表状态由

产品预览

更改为

量产数据

........................................................................................................................... 1

VCC

CSN

SW

1

2

3

4

IADJ

PWM

COFF

GND

10

9

8

7

5 6 DRN

VIN

BOOT

Thermal Pad

3

TPS92515

,

TPS92515-Q1

,

TPS92515HV

,

TPS92515HV-Q1

www.ti.com.cn

ZHCSFD3A –APRIL 2016–REVISED AUGUST 2016

Copyright © 2016, Texas Instruments Incorporated

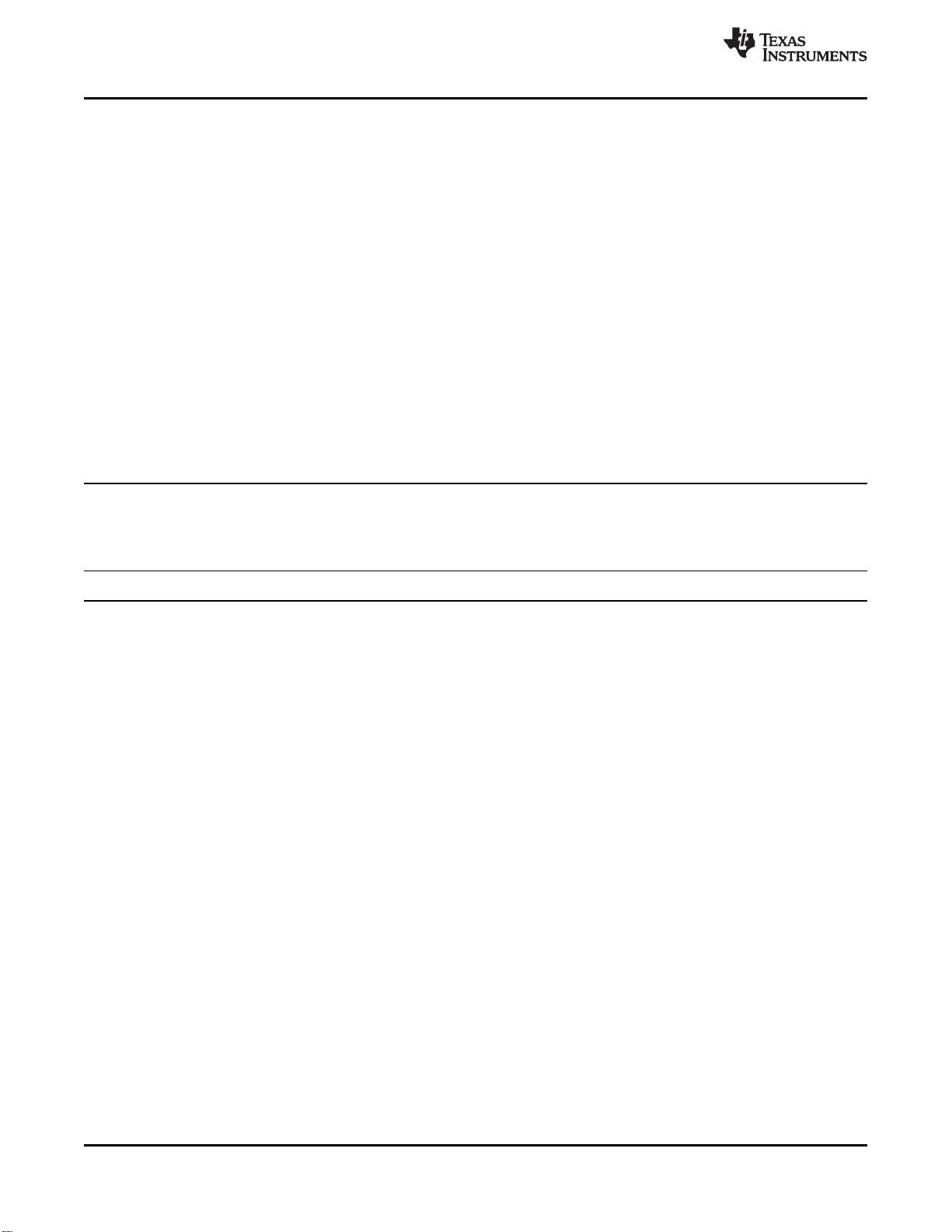

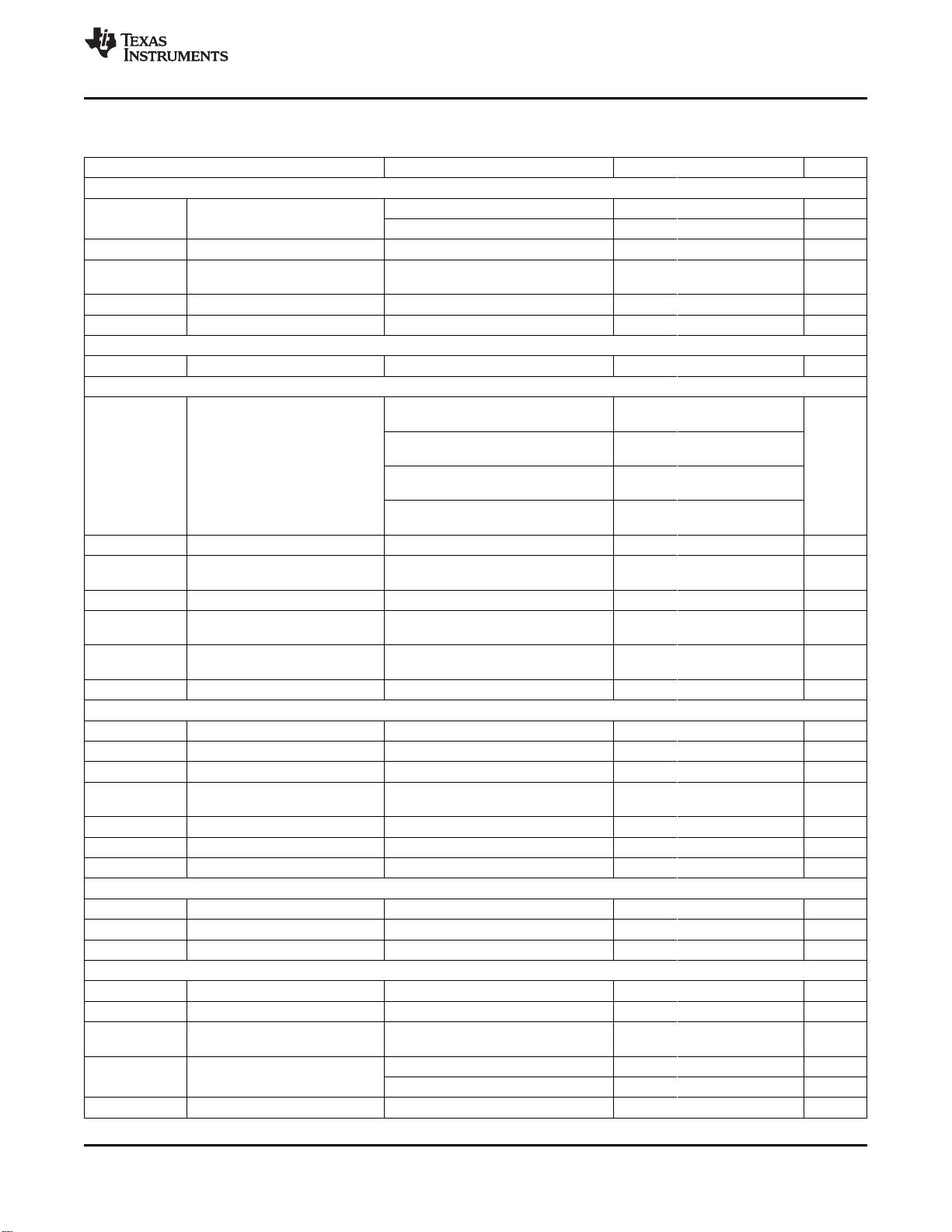

5 Device Comparison Table

DEVICE

MAXIMUM

VOLTAGE (V)

CONTROL METHOD

AUTOMOTIVE

QUALIFIED

TPS92515HV-Q1 65

Internal N-channel FET, constant OFF-time

Y

TPS92515-Q1 42 Y

TPS92515HV 65 N

TPS92515 42 N

LM3409HV-Q1 75

External P-channel FET, constant OFF-time

Y

LM3409-Q1 42 Y

LM3409HV 75

External P-channel FET, constant OFF-time

N

LM3409 42 N

LM3406HV-Q1 75

Internal N-channel FET, controlled ON-time

Y

LM3406-Q1 42 Y

LM3406HV 75 N

LM3406 42 N

6 Pin Configuration and Functions

DGQ Package

HVSSOP 10-Pin with PowerPAD

Top View

Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

BOOT 4 I

Connect a ceramic capacitor between BOOT and SW and a diode from VCC to BOOT to

power the high-side FET drive circuitry.

COFF 1 I Connect a resistor from V

OUT

, and a capacitor to GND to set the OFF-time.

CSN 7 I

Current sense negative input. Connect current sense resistor from VIN to CSN for high-side

current sense control.

DRN 6 I Internal FET drain. Connect to CSN node

GND 3 G Ground

IADJ 10 I Output current adjust. Connect to an external divider, reference or tie to VCC.

PWM 9 I

PWM dimming input. Connect to PWM control signal. Output current is pulse-width

modulated (PWM) dimmed from the maximum analog controlled level. Connect to VCC if not

used.

SW 5 O Internal FET Source. Connect to output inductor

VCC 2 O

5-V Regulator Output. Use a decoupling capacitor from VCC to ground. See section on VCC

capacitor selection.

VIN 8 I Connect to input voltage. VIN is also the current sense positive input.

Thermal pad — Connect to ground

4

TPS92515

,

TPS92515-Q1

,

TPS92515HV

,

TPS92515HV-Q1

ZHCSFD3A –APRIL 2016–REVISED AUGUST 2016

www.ti.com.cn

Copyright © 2016, Texas Instruments Incorporated

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) DRN to SW. Absolute maximum not to be exceeded.

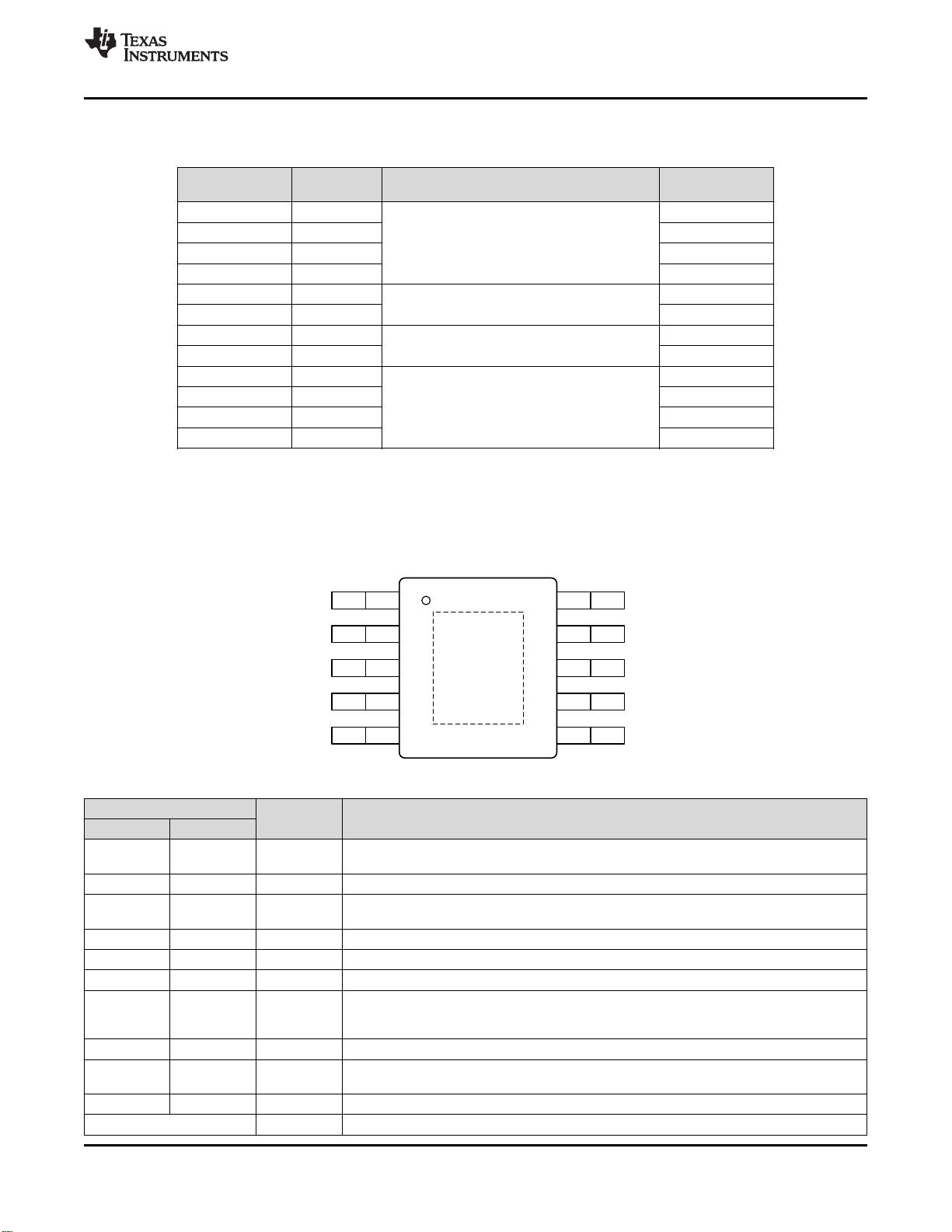

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)

MIN MAX UNIT

VIN, DRN, SW, CSN to GND

TPS92515, TPS92515-Q1 –0.3 45.0

V

TPS92515HV, TPS92515HV-Q1 –0.3 65.0

DRN to SW

TPS92515, TPS92515-Q1 –0.3 45.0

TPS92515HV, TPS92515HV-Q1 –0.3 65.0

BOOT to GND

TPS92515, TPS92515-Q1 –0.3 50.5

TPS92515HV, TPS92515HV-Q1 –0.3 70.5

COFF, IADJ, PWM to GND –0.3 5.5

BOOT to SW –0.3 5.5

VCC to GND -0.3 5.5

VIN to CSN –0.3 0.3

SW to GND, 10-ns transient

(2)

–2.0

Storage temperature, T

stg

-40 150 °C

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

7.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic

discharge

Human-body model (HBM), per AEC Q100-002

(1)

±2000

V

Charged-device model (CDM), per AEC Q100-011 ±750

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

V

IN

Input voltage

TPS92515, TPS92515-Q1 5.5 42

V

TPS92515HV, TPS92515HV-Q1 5.5 65

T

A

Operating ambient temperature 125 °C

T

J

Operating junction temperature 150 °C

(1) For more information about traditional and new thermal metrics, see the Semiconductor and device Package Thermal Metrics

application report, SPRA953.

7.4 Thermal Information

THERMAL METRIC

(1)

TPS92515

UNITHVSSOP

10 PINS

R

θJA

Junction-to-ambient thermal resistance 56.2 °C/W

R

θJC(top)

Junction-to-case (top) thermal resistance 44.7 °C/W

R

θJB

Junction-to-board thermal resistance 32.1 °C/W

ψ

JT

Junction-to-top characterization parameter 1.5 °C/W

ψ

JB

Junction-to-board characterization parameter 31.8 °C/W

R

θJC(bot)

Junction-to-case (bottom) thermal resistance 5.3 °C/W

5

TPS92515

,

TPS92515-Q1

,

TPS92515HV

,

TPS92515HV-Q1

www.ti.com.cn

ZHCSFD3A –APRIL 2016–REVISED AUGUST 2016

Copyright © 2016, Texas Instruments Incorporated

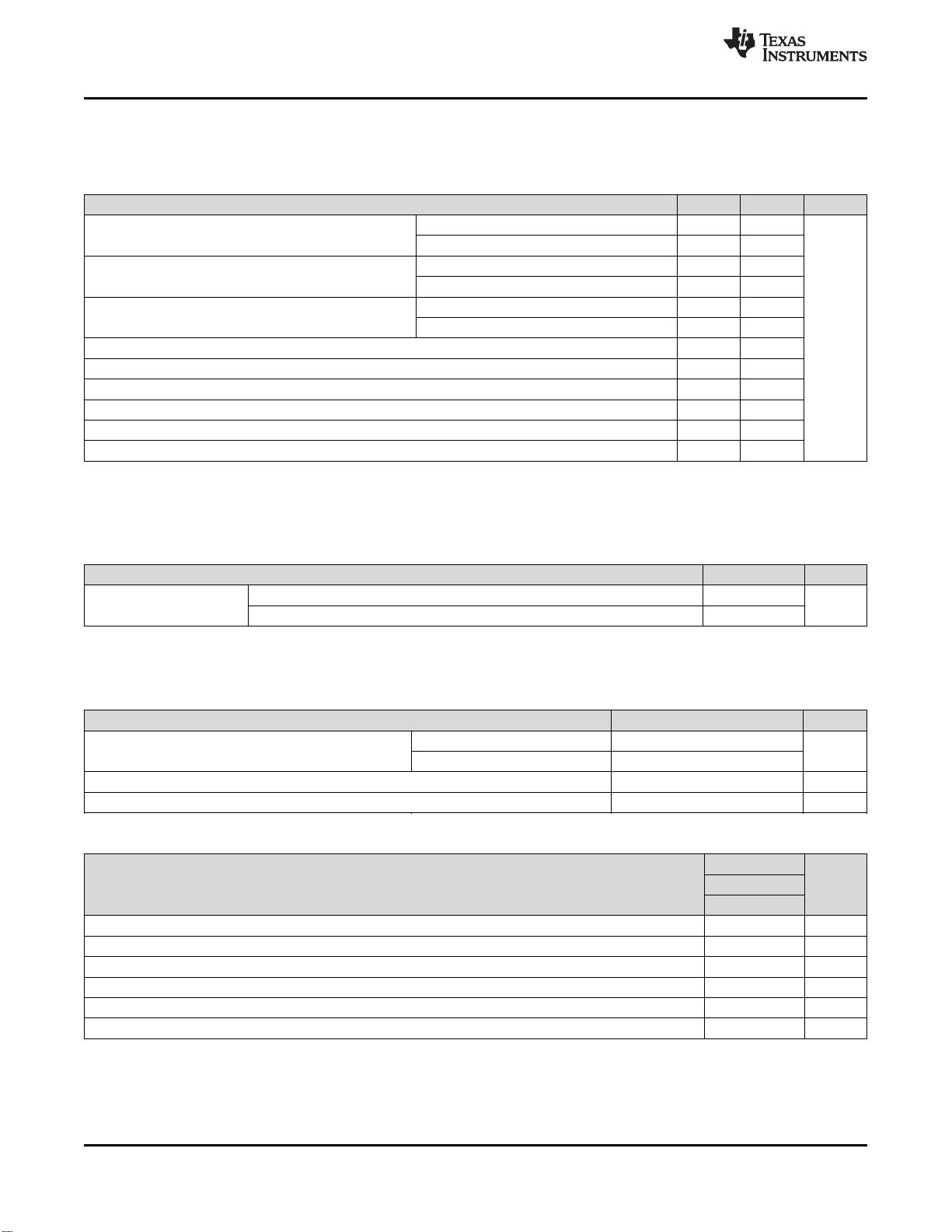

7.5 Electrical Characteristics

V

IN

= 40 V, –40°C ≤ T

J

≤ 150°C, V

BOOT

is referenced to SW pin, unless otherwise specified.

PARAMETER TEST CONDITION MIN TYP MAX UNIT

PEAK CURRENT COMPARATOR

V

CST

V

IN

– V

CSN

peak current threshold

V

IADJ

= VCC 224 240 251 mV

V

IADJ

= 2.2 V 211.5 220 223.5 mV

A

ADJ

V

IADJ

to V

IN

– V

CSN

threshold gain 0.1 ≤ V

IADJ

≤ 2.2 V 0.1 V/V

I

CSN

Current sense pin, input bias

current

–5 0 µA

t

DEL

CSN pin falling delay CSN fall to SW fall 75 130 ns

t

LEB

Minimum ON-time Minimum pulse width 75 195 275 ns

SYSTEM CURRENTS

I

cq

Operating current Not switching, V

IADJ

= V

VCC

0.85 1.5 mA

INTEGRATED N-Channel MOSFET AND DRIVER

R

DS(on)

FET ON-resistance

I

DRN-SW

= 200mA, V

BOOT

= 5 V,

T

J

= 25°C

290 500

mΩ

I

DRN-SW

= 200mA, V

BOOT

= 5 V,

T

J

= 150°C

290 600

I

DRN-SW

= 200mA, V

BOOT

= 3.5 V,

T

J

= 25°C

310 500

I

DRN-SW

= 200mA, V

BOOT

= 3.5 V,

T

J

= 150°C

310 650

I

DRN-SW(off)

FET leakage current V

DRN-SW

= 6 V, V

SW

= 0 V 10 µA

V

BOOT-UVLO

Voltage where gate drive is

disabled

V

BOOT

falling 2.0 2.8 3.5 V

V

BOOT-UVLO(hys)

BOOT pin UVLO Hysteresis 125 mV

I

PD(PWM/UVLO)

Pull down from SW when PWM

low.

PWM low, V

BOOT

= 5 V , V

SW

= 8 V 100 130 µA

I

PD(BOOT)

Pull down from SW when V

BOOT

reaches V

BOOT-UVLO

PWM high, V

BOOT

< BOOT-UVLO, V

SW

= 8 V

5 7 mA

I

BOOT_Q

BOOT pin quiescent current V

BOOT

= 5.5 V, 0 V ≤ V

SW

≤ 65 V 60 90 µA

VCC/REFERENCE REGULATOR

VCC Regulated pin voltage I

VCC(ext)

≤ 500 µA 4.8 5.0 5.2 V

VCC

DO

Drop out voltage I

VCC(ext)

≤ 500 µA 0.1 0.2 V

VCC

UVLO

VCC undervoltage lockout Falling threshold, V

IN

= 10 V 4.0 4.2 4.4 V

VCC

UVLO_hys

VCC undervoltage lockout

hysteresis

0.22 V

I

VCC(ILIM)

VCC regulator current limit VCC shorted to GND 14 19 23 mA

VIN

UVLO

VIN UVLO Falling Threshold 4.65 4.90 5.15 V

VIN

UVLO_hys

VIN UVLO Hysteresis 150 190 225 mV

OFF-TIMER

V

OFT

OFF-time threshold 0.95 1.00 1.05 V

t

D(off)

C

OFF

threshold C

OFF

to SW rising delay 68 120 ns

t

OFF(max)

Maximum OFF-time 230 µs

PWM/UVLO (Enable)

I

PWM(uvlo)

PWM/UVLO pin current V

PWM(uvlo)

= 5.5 V 10 nA

V

PWM(uvlo)

PWM/UVLO pin threshold PWM pin rising 0.95 1.0 1.05 V

V

PWM(uvlo-hys)

PWM/UVLO pin hysteresis

Difference between rising and falling

threshold

50 100 150 mV

t

PWM(uvlo)

PWM/UVLO pin delay

PWM pin rising to SW pin rising 75 130 ns

PWM pin falling to SW pin falling 100 170 ns

I

PWM(uvlo-hys)

PWM/UVLO hysteresis current V

PWM(uvlo)

= 2 V –25 –20 –15 μA

剩余40页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3102

- 资源: 5337

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功