没有合适的资源?快使用搜索试试~ 我知道了~

TI-TPS51200A-Q1.pdf

需积分: 10 0 下载量 16 浏览量

2022-11-20

17:26:20

上传

评论 5

收藏 2.07MB PDF 举报

温馨提示

试读

39页

TI-TPS51200A-Q1.pdf

资源推荐

资源详情

资源评论

2

3

4

5

1

9

8

7

6

10

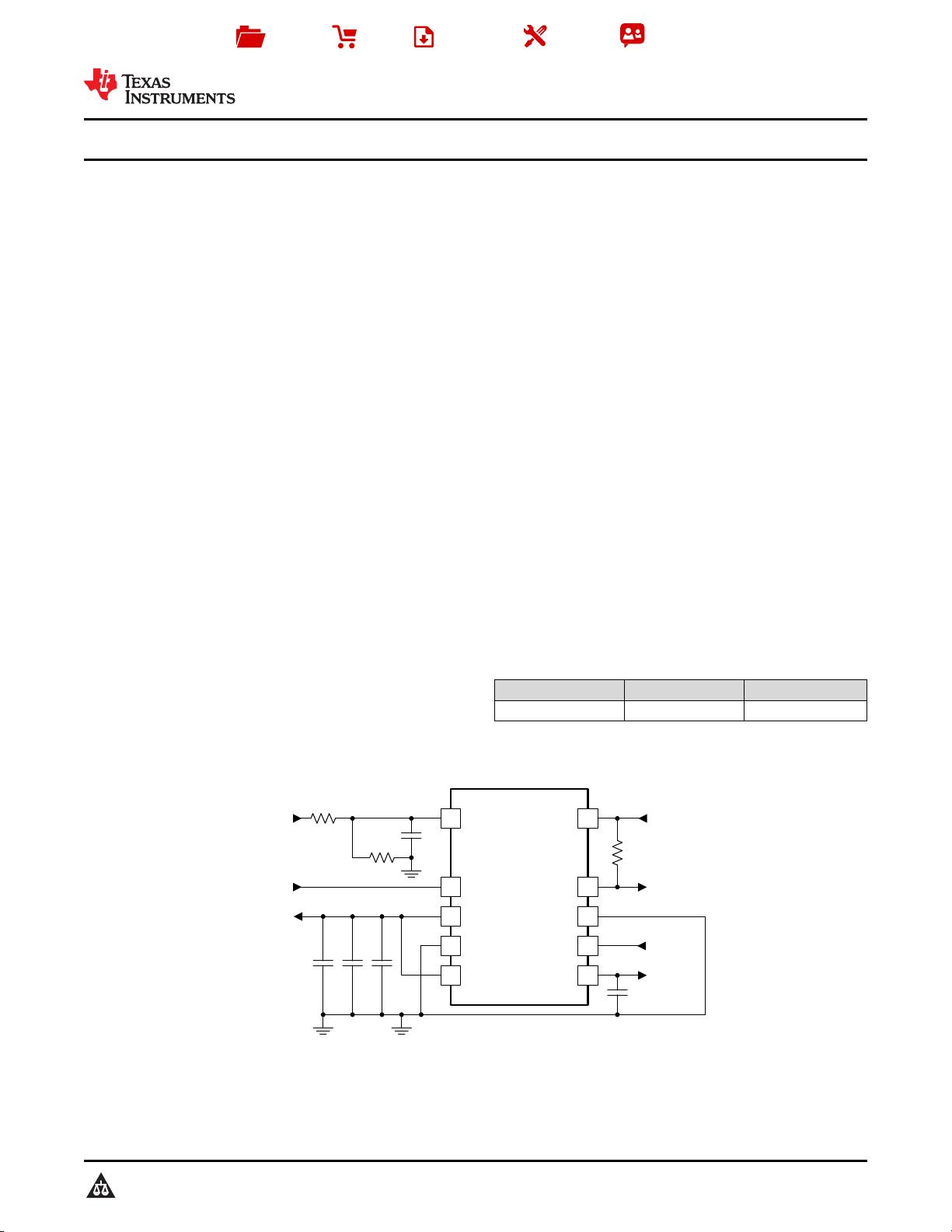

TPS51200A-Q1

REFIN

VLDOIN

VO

PGND

VOSNS

VIN

PGOOD

GND

EN

REFOUT

3.3 V

IN

PGOOD

SLP_S3

VTTREF

VLDOIN

V

TT

V

DDQ

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

本文档旨在为方便起见,提供有关 TI 产品中文版本的信息,以确认产品的概要。 有关适用的官方英文版本的最新信息,请访问 www.ti.com,其内容始终优先。 TI 不保证翻译的准确

性和有效性。 在实际设计之前,请务必参考最新版本的英文版本。

English Data Sheet: SLUSD58

TPS51200A-Q1

ZHCSIL4A –JUNE 2018–REVISED DECEMBER 2018

TPS51200A-Q1 灌灌电电流流和和拉拉电电流流 DDR 终终端端稳稳压压器器

1

1 特特性性

1

• 符合面向汽车应用的 AEC-Q100 AEC-Q100 标

准:

– 器件温度等级 1:

–40°C ≤ T

A

≤ 125°C

– 器件 HBM ESD 分类等级 2

– 器件 CDM ESD 分类等级 C4B

• 扩展的可靠性测试

• 输入电压:支持 2.5V 和 3.3V 电源轨

• VLDOIN 电压范围:1.1V 至 3.5V

• 具有压降补偿功能的灌电流和拉电流终端稳压器

• 所需最小输出电容为 20μF(通常为 3 × 10μF

MLCC),用于存储器终端 应用 (DDR)

• 用于监视输出稳压的 PGOOD

• EN 输入

• REFIN 输入允许直接或通过电阻分压器灵活进行输

入跟踪

• 远程检测 (VOSNS)

• ±10mA 缓冲基准 (REFOUT)

• 内置软启动、UVLO 和 OCL

• 热关断

• 符合 DDR、DDR2 JEDEC 规范;支持 DDR3、低

功耗 DDR3 和 DDR4 VTT 应用

• 带外露散热焊盘的 VSON-10 封装

2 应应用用

• 用于 DDR、DDR2、DDR3、低功耗 DDR3 和

DDR4 的存储器终端稳压器

• 笔记本电脑、台式机、服务器

• 电信和数据通信、GSM 基站、液晶 (LCD) 电视和

等离子 (PDP) 电视、复印机和打印机、机顶盒

3 说说明明

TPS51200A-Q1 器件是一款灌电流和拉电流双倍数据

速率 (DDR) 终端稳压器,专门针对低输入电压、低成

本、低噪声的空间受限型系统而设计。

此器件可保持快速的瞬态响应,最低仅需 20μF 输出电

容。此器件支持遥感功能,并且可满足 DDR、

DDR2、DDR3、低功耗 DDR3 和 DDR4 VTT 总线终

端的所有电源要求。

此外,该器件还提供一个开漏 PGOOD 信号来监测输

出稳压,并提供一个 EN 信号在 S3(挂起至 RAM)

期间针对 DDR 应用进行 VTT 放电。

此器件采用高效散热型 VSON-10 封装,具有绿色环保

和无铅的特性。该器件的额定温度范围为 –40°C 至

125°C。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

TPS51200A-Q1 VSON (10) 3.00mm × 3.00mm

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

简简化化的的 DDR 应应用用

2

TPS51200A-Q1

ZHCSIL4A –JUNE 2018–REVISED DECEMBER 2018

www.ti.com.cn

Copyright © 2018, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 4

6.1 Absolute Maximum Ratings ..................................... 4

6.2 ESD Ratings.............................................................. 4

6.3 Recommended Operating Conditions....................... 4

6.4 Thermal Information.................................................. 4

6.5 Electrical Characteristics........................................... 5

6.6 Switching Characteristics.......................................... 6

6.7 Typical Characteristics.............................................. 6

7 Detailed Description............................................ 10

7.1 Overview ................................................................ 10

7.2 Functional Block Diagram ....................................... 10

7.3 Feature Description................................................. 10

7.4 Device Functional Modes........................................ 12

8 Application and Implementation ........................ 14

8.1 Application Information............................................ 14

8.2 Typical Application ................................................. 14

9 Power Supply Recommendations...................... 25

10 Layout................................................................... 25

10.1 Layout Guidelines ................................................. 25

10.2 Layout Example .................................................... 26

10.3 Thermal Considerations........................................ 27

11 器器件件和和文文档档支支持持 ..................................................... 29

11.1 器件支持................................................................ 29

11.2 文档支持................................................................ 29

11.3 接收文档更新通知 ................................................. 29

11.4 社区资源................................................................ 29

11.5 商标 ....................................................................... 29

11.6 静电放电警告......................................................... 29

11.7 术语表 ................................................................... 29

12 机机械械、、封封装装和和可可订订购购信信息息....................................... 29

4 修修订订历历史史记记录录

注:之前版本的页码可能与当前版本有所不同。

Changes from Original (June 2018) to Revision A Page

• 已添加 “

扩展的可靠性测试

”添加到

特性

列表中的项目 ............................................................................................................. 1

• 已更改 将文档状态从“

预告信息

”

更改

为“

生产数据

”.................................................................................................................. 1

• Updated device number error in schematic illustrations ...................................................................................................... 14

REFIN

VLDOIN

VO

PGND

VOSNS

VIN

PGOOD

GND

EN

REFOUT

Thermal

Pad

10

9

8

7

6

1

2

3

4

5

3

TPS51200A-Q1

www.ti.com.cn

ZHCSIL4A –JUNE 2018–REVISED DECEMBER 2018

Copyright © 2018, Texas Instruments Incorporated

(1) Thermal pad connection. See 图 35 in the Thermal Considerations section for additional information.

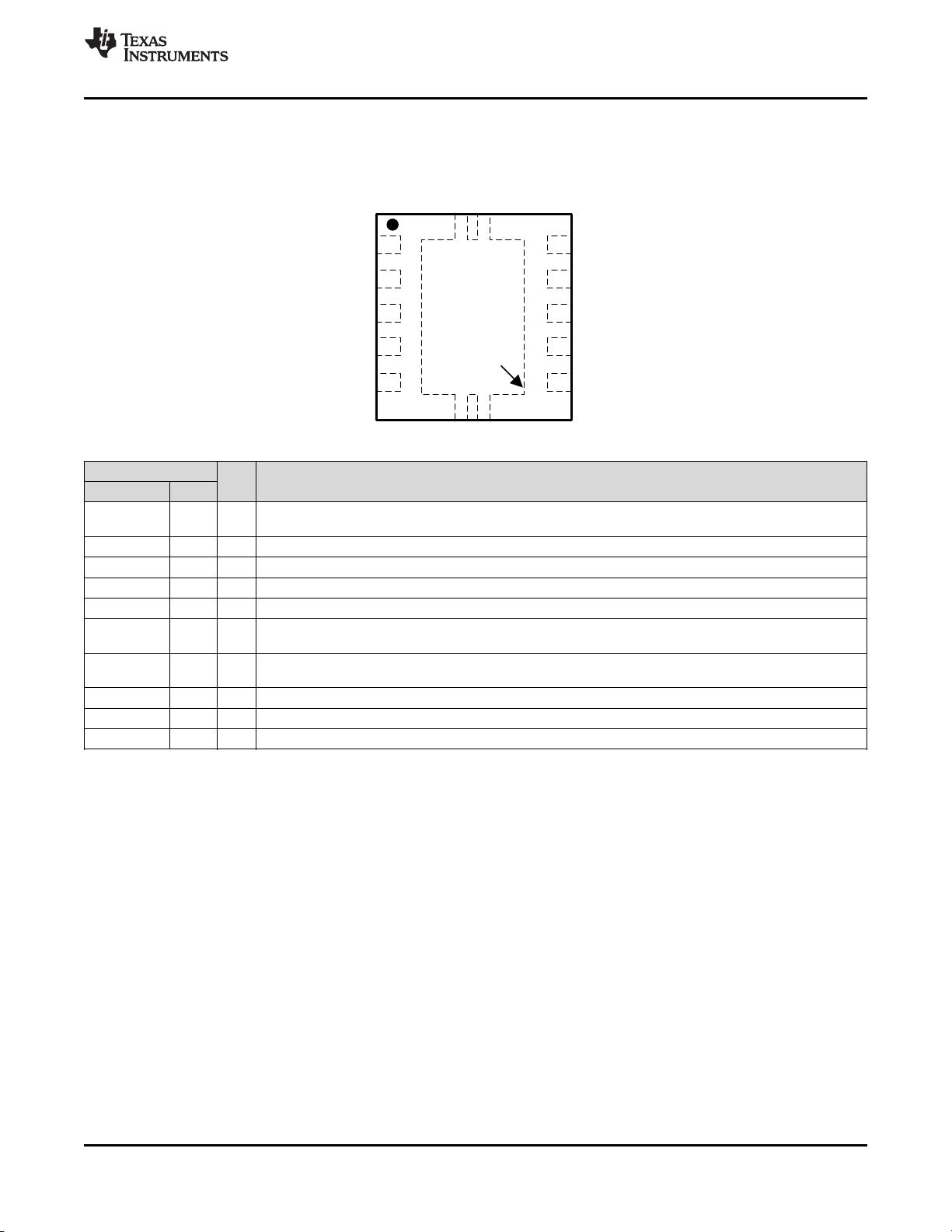

5 Pin Configuration and Functions

DRC Package

10-Pin VSON With Exposed Thermal Pad

Top View

Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

EN 7 I

For DDR VTT application, connect EN to SLP_S3. For any other applications, use EN as the ON/OFF

function. Keep EN voltage equal or lower than VIN voltage at all times.

GND 8 — Ground. Signal ground. Connect to negative pin of the output capacitor.

PGND

(1)

4 — Power ground output for the LDO

PGOOD 9 O PGOOD output. Indicates regulation.

REFIN 1 I Reference input

REFOUT 6 O

Reference output. Connect to GND through 0.1-μF ceramic capacitor. If there is REFOUT capacitor at DDR

side, keep the total capacitance on REFOUT pin below 1 μF. The REFOUT pin can not be open.

VIN 10 I

2.5-V or 3.3-V power supply A ceramic decoupling capacitor with a value between 1-μF and 4.7-μF is

required.

VLDOIN 2 I Supply voltage for the LDO.

VO 3 O Power output for the LDO. Minimum 20-μF capacitance is required. No maximum capacitance limit.

VOSNS 5 I Voltage sense output for the LDO. Connect to positive pin of the output capacitor or the load.

4

TPS51200A-Q1

ZHCSIL4A –JUNE 2018–REVISED DECEMBER 2018

www.ti.com.cn

Copyright © 2018, Texas Instruments Incorporated

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating

Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground pin unless otherwise noted.

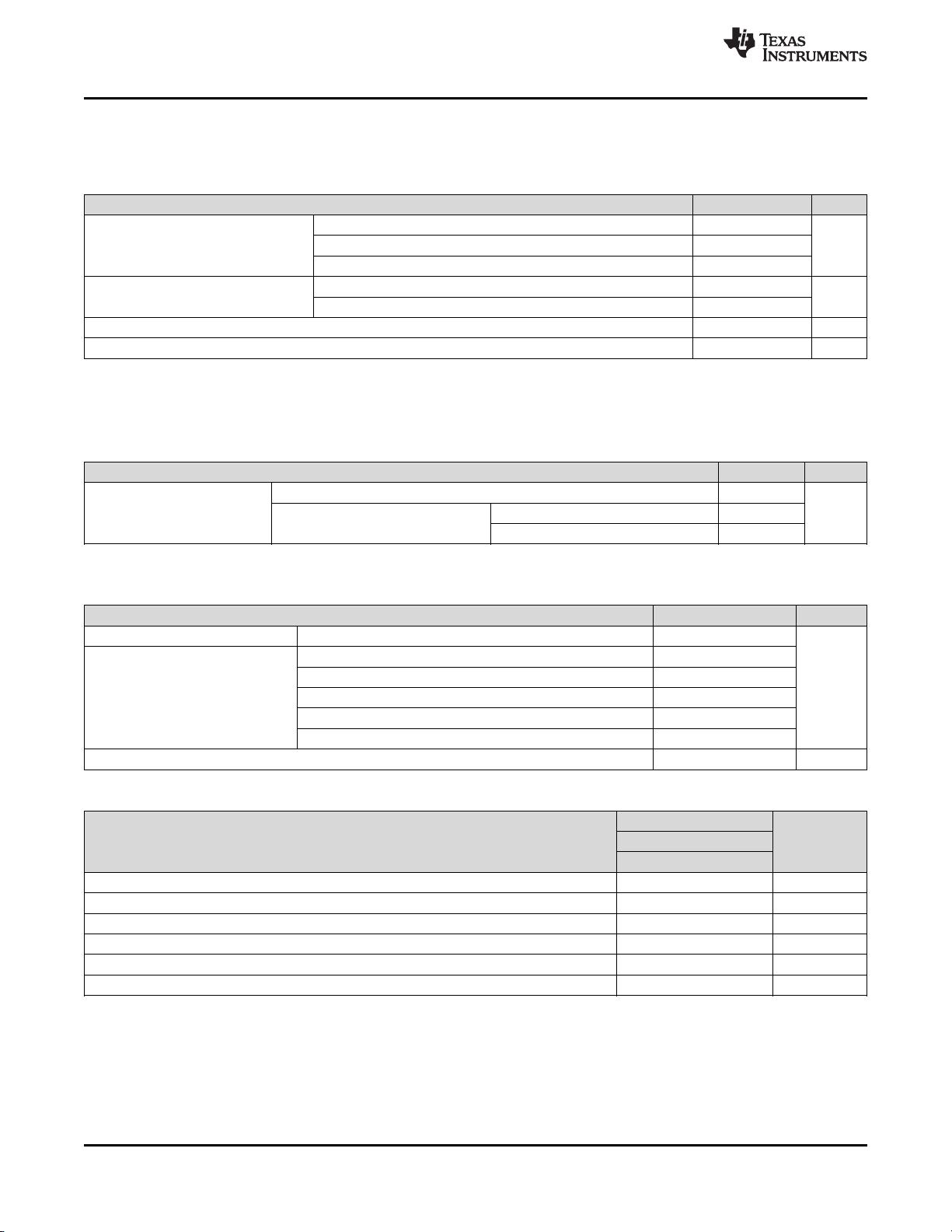

6 Specifications

6.1 Absolute Maximum Ratings

Over operating free-air temperature range, unless otherwise noted.

(1)

MIN MAX UNIT

Input voltage

(2)

VIN, VLDOIN, VOSNS, REFIN –0.3 3.6

VEN –0.3 6.5

PGND to GND –0.3 0.3

Output voltage

(2)

VO, REFOUT –0.3 3.6

V

PGOOD –0.3 6.5

Operating junction temperature, T

J

150 °C

Storage temperature, T

stg

–55 150 °C

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic

discharge

Human body model (HBM), per AEC Q100-002

(1)

±2000

V

Charged device model (CDM), per

AEC Q100-011

Corner pins (1, 5, 6, and 10) ±750

Other pins ±500

6.3 Recommended Operating Conditions

MIN MAX UNIT

Supply voltage VIN 2.375 3.500

V

Voltage range

EN, VLDOIN, VOSNS –0.1 3.5

REFIN 0.5 1.8

VO, PGOOD –0.1 3.5

REFOUT –0.1 1.8

PGND –0.1 0.1

Operating free-air temperature, T

A

–40 125 °C

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

6.4 Thermal Information

THERMAL METRIC

(1)

TPS51200A-Q1

UNITDRC (VSON)

10 PINS

R

θJA

Junction-to-ambient thermal resistance 55.7 °C/W

R

θJCtop

Junction-to-case (top) thermal resistance 62.2 °C/W

R

θJB

Junction-to-board thermal resistance 28.0 °C/W

ψ

JT

Junction-to-top characterization parameter 3.1 °C/W

ψ

JB

Junction-to-board characterization parameter 27.9 °C/W

R

θJCbot

Junction-to-case (bottom) thermal resistance 12.1 °C/W

5

TPS51200A-Q1

www.ti.com.cn

ZHCSIL4A –JUNE 2018–REVISED DECEMBER 2018

Copyright © 2018, Texas Instruments Incorporated

(1) Ensured by design. Not production tested.

6.5 Electrical Characteristics

Over recommended free-air temperature range, V

VIN

= 3.3 V, V

VLDOIN

= 1.8 V, V

REFIN

= 0.9 V, V

VOSNS

= 0.9 V, V

EN

= V

VIN

, C

OUT

= 3 × 10 μF and circuit shown in the

简化的

DDR

应用

section (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SUPPLY CURRENT

I

IN

Supply current T

A

= 25 °C, V

EN

= 3.3 V, No Load 0.7 1 mA

I

IN(SDN)

Shutdown current

T

A

= 25 °C, V

EN

= 0 V, V

REFIN

= 0, No Load 65 80

μA

T

A

= 25 °C, V

EN

= 0 V, V

REFIN

> 0.4 V, No Load 200 400

I

LDOIN

Supply current of VLDOIN T

A

= 25 °C, V

EN

= 3.3 V, No Load 1 50 μA

I

LDOIN(SDN)

Shutdown current of VLDOIN T

A

= 25 °C, V

EN

= 0 V, No Load 0.1 50 μA

INPUT CURRENT

I

REFIN

Input current, REFIN V

EN

= 3.3 V 1 μA

VO OUTPUT

V

VOSNS

Output DC voltage, VO

V

REFOUT

= 1.25 V (DDR1), I

O

= 0 A

1.25 V

–15 15 mV

V

REFOUT

= 0.9 V (DDR2), I

O

= 0 A

0.9 V

–15 15 mV

V

REFOUT

= 0.75 V (DDR3), I

O

= 0 A

0.75 V

–15 15 mV

V

REFOUT

= 0.675 V (DDR3L), I

O

= 0 A

0.675 V

-15 15 mV

V

REFOUT

= 0.6 V (DDR4), I

O

= 0 A

0.6 V

-15 15 mV

V

VOTOL

Output voltage tolerance to REFOUT –2A < I

VO

< 2A –25 25 mV

I

VOSRCL

VO source current Limit With reference to REFOUT, V

OSNS

= 90% × V

REFOUT

3 4.5 A

I

VOSNCL

VO sink current Limit With reference to REFOUT, V

OSNS

= 110% × V

REFOUT

3.5 5.5 A

I

DSCHRG

Discharge current, VO V

REFIN

= 0 V, V

VO

= 0.3 V, V

EN

= 0 V, T

A

= 25°C 18 25 Ω

POWERGOOD COMPARATOR

V

TH(PG)

VO PGOOD threshold

PGOOD window lower threshold with respect to REFOUT –23.5% –20% –17.5%

PGOOD window upper threshold with respect to REFOUT 17.5% 20% 23.5%

PGOOD hysteresis 5%

V

PGOODLOW

Output low voltage I

SINK

= 4 mA 0.4 V

I

PGOODLK

Leakage current

(1)

V

OSNS

= V

REFIN

(PGOOD high impedance), PGOOD = V

IN

+ 0.2 V

1 μA

REFIN AND REFOUT

V

REFIN

REFIN voltage range 0.5 1.8 V

V

REFINUVLO

REFIN undervoltage lockout REFIN rising 360 390 420 mV

V

REFINUVHYS

REFIN undervoltage lockout hysteresis 20 mV

V

REFOUT

REFOUT voltage REFIN V

V

REFOUTTOL

REFOUT voltage tolerance to V

REFIN

–10 mA ≤ I

REFOUT

≤ 10 mA, 0.6 V ≤ V

REFIN

≤ 1.25 V –15 15

mV

–1 mA ≤ I

REFOUT

≤ 1 mA, 0.6 V ≤ V

REFIN

≤ 1.25 V -12 12

I

REFOUTSRCL

REFOUT source current limit V

REFOUT

= 0.5 V 10 40 mA

I

REFOUTSNCL

REFOUT sink current limit V

REFOUT

= 1.5 V 10 40 mA

UVLO / EN LOGIC THRESHOLD

V

VINUVLO

UVLO threshold

Wake up, T

A

= 25°C 2.2 2.3 2.375 V

Hysteresis 50 mV

V

ENIH

High-level input voltage Enable 1.7 V

V

ENIL

Low-level input voltage Enable 0.3 V

V

ENYST

Hysteresis voltage Enable 0.5 V

I

ENLEAK

Logic input leakage current EN, T

A

= 25°C –1 1 μA

THERMAL SHUTDOWN

T

SDN

Thermal shutdown threshold

(1)

Shutdown temperature 150

°C

Hysteresis 25

剩余38页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3118

- 资源: 5348

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功