没有合适的资源?快使用搜索试试~ 我知道了~

TI-THS4541-Q1.pdf

需积分: 10 0 下载量 160 浏览量

2022-11-24

23:40:27

上传

评论 5

收藏 2.6MB PDF 举报

温馨提示

试读

65页

TI-THS4541-Q1.pdf

资源详情

资源评论

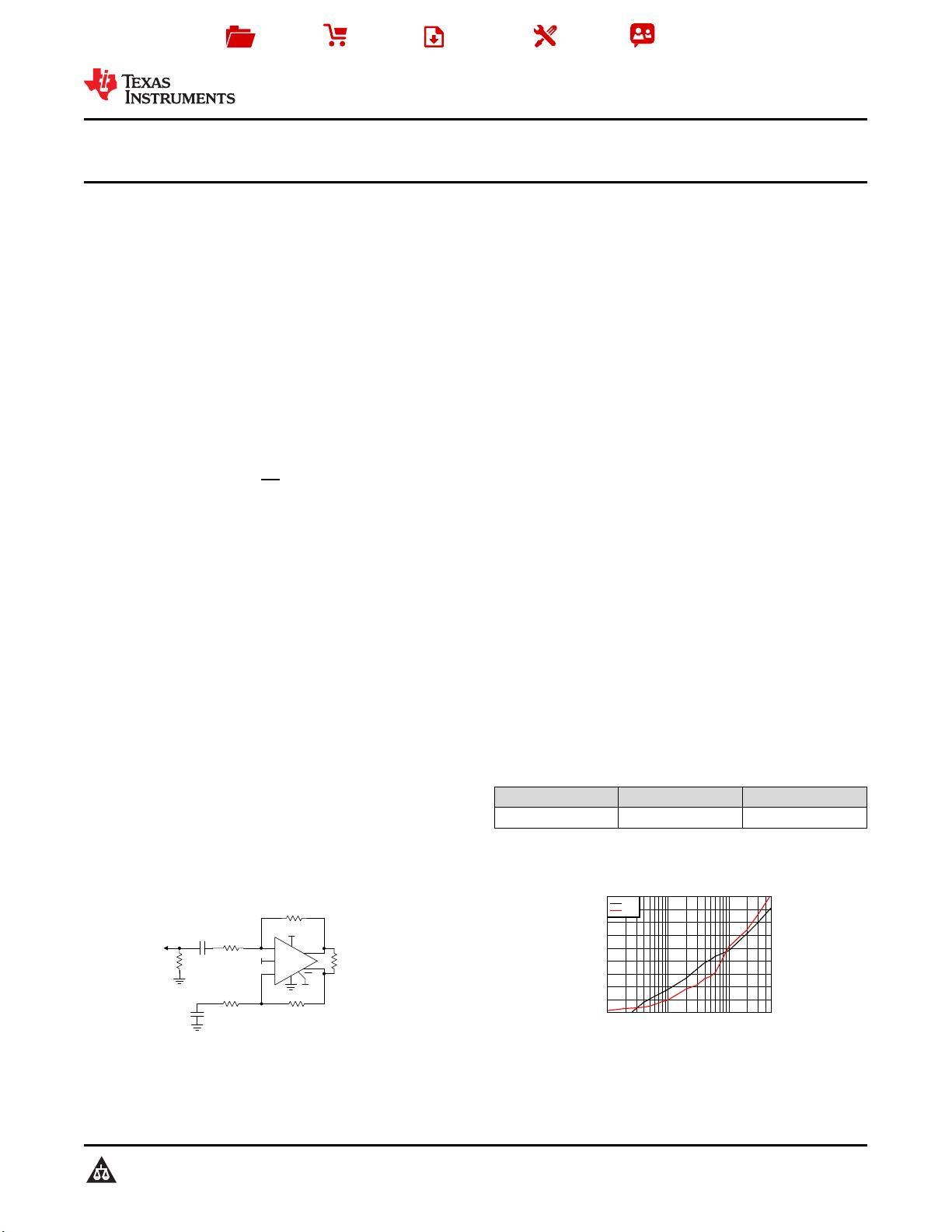

Frequency (MHz)

Distortion (dBc)

0.1 1 10 50

-140

-130

-120

-110

-100

-90

-80

-70

-60

-50

D013

HD2

HD3

C2

100 nF

Rf1

402

Rload

500

Rg1

191

C1

100 nF

Rg2

221

Rt

60.2

Output

Measurement

Point

THS4541 Wideband,

Fully-Differential Amplifier

50-Input Match,

Gain of 2 V/V from Rt,

Single-Ended Source to

Differential Output

Vocm

Rf2

402

50-

Source

+

±

Vcc

+

±

Vocm

Vcc

FDA

PD

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: SLOS930

THS4541-Q1

ZHCSEK0A –NOVEMBER 2015–REVISED NOVEMBER 2015

THS4541-Q1 负负轨轨输输入入、、轨轨到到轨轨输输出出、、高高精精度度、、850MHz

全全差差分分放放大大器器

1

1 特特性性

1

• 适用于汽车电子 应用

• 具有符合 AEC-Q100 标准的下列结果:

– 器件温度 1 级:-40℃ 至 +125℃ 的环境运行温

度范围

– 器件人体放电模式 (HBM) 分类等级 2

– 器件组件充电模式 (CDM) 分类等级 C6

• 完全差分放大器 (FDA) 架构

• 带宽:500MHz (G = 2V/V)

• 增益带宽产品:850MHz

• 转换率:1500V/μs

• HD

2

:10MHz 时为 –95dBc(2 V

PP

,R

L

= 500Ω)

• HD

3

:10MHz 时为 –90dBc(2 V

PP

,R

L

= 500Ω)

• 输入电压噪声:2.2nV/Hz(f > 100kHz)

• 低偏移漂移:±0.5µV/°C(典型值)

• 负轨输入 (NRI)

• 轨到轨输出 (RRO)

• Rload ≥ 50Ω 时仍可稳定运行

• 输出共模控制

• 电源:

– 单电源电压范围:2.7V 到 5.4V

– 分离电源电压范围:±1.35V 到 ±2.7V

– 静态电流:10.1mA(5V 电源)

• 断电能力:2µA(典型值)

2 应应用用

• 低功耗高性能模数转换器 (ADC) 驱动器

– SAR、ΔΣ 和流水线

• 低功耗、高性能(直流耦合或交流耦合)

– 单端到差分放大器

– 差分到差分放大器

• 差分有源滤波器

• 数模转换器 (DAC) 输出的差分互阻抗

• ADC3xxx 系列低功耗、高性能 ADC 的直流耦合或

交流耦合接口

• 与 ADA4932-1 (VQFN-16) 引脚兼容

3 说说明明

THS4541-Q1 器件是一款低功耗、电压反馈、全差分

放大器 (FDA),其具有低于负电源轨的输入共模范围以

及轨到轨输出。其设计用于低功耗数据采集系统,其中

高密度对于高性能 ADC 或 DAC 接口设计至关重要。

THS4541-Q1 器件 提供了 连接直流耦合中央接地源信

号所需的负轨输入。此负轨输入搭配轨到轨输出,只需

使用一个 2.7V 到 5.4V 的电源即可轻松将单端接地基

准双极信号源与各种逐次逼近寄存器 (SAR)、Δ-Σ 或流

水线 ADC 相连接。

THS4541-Q1 器件的额定运行温度介于 –40°C 与

+125°C 之间,并且采用 16 引脚超薄四方扁平无引线

(VQFN) 封装。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

THS4541-Q1 VQFN (16) 3.00mm x 3.00mm

(1) 要了解所有可用封装,请参见数据表末尾的封装选项附录。

简简化化电电路路原原理理图图

单单端端到到差差分分增增益益为为 2,,2 V

PP

输输出出

2

THS4541-Q1

ZHCSEK0A –NOVEMBER 2015–REVISED NOVEMBER 2015

www.ti.com.cn

Copyright © 2015, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Device Family Comparison................................... 3

6 Pin Configuration and Functions......................... 3

7 Specifications......................................................... 4

7.1 Absolute Maximum Ratings ...................................... 4

7.2 ESD Ratings.............................................................. 4

7.3 Recommended Operating Conditions....................... 4

7.4 Thermal Information.................................................. 4

7.5 Electrical Characteristics: (Vs+) – Vs– = 5 V........... 5

7.6 Electrical Characteristics: (Vs+) – Vs– = 3 V........... 8

7.7 Typical Characteristics............................................ 11

8 Parameter Measurement Information ................ 21

8.1 Example Characterization Circuits.......................... 21

8.2 Frequency-Response Shape Factors ..................... 23

8.3 I/O Headroom Considerations ................................ 26

8.4 Output DC Error and Drift Calculations and the Effect

of Resistor Imbalances ............................................ 28

8.5 Noise Analysis......................................................... 30

8.6 Factors Influencing Harmonic Distortion................. 31

8.7 Driving Capacitive Loads ........................................ 32

8.8 Thermal Analysis..................................................... 32

9 Detailed Description............................................ 33

9.1 Overview ................................................................. 33

9.2 Functional Block Diagram ....................................... 34

9.3 Feature Description................................................. 35

9.4 Device Functional Modes........................................ 36

10 Application and Implementation........................ 44

10.1 Application Information.......................................... 44

10.2 Typical Applications .............................................. 44

11 Power-Supply Recommendations..................... 49

12 Layout................................................................... 49

12.1 Layout Guidelines ................................................. 49

12.2 Layout Example .................................................... 50

13 器器件件和和文文档档支支持持 ..................................................... 51

13.1 器件支持................................................................ 51

13.2 文档支持................................................................ 51

13.3 社区资源................................................................ 51

13.4 商标 ....................................................................... 51

13.5 静电放电警告......................................................... 52

13.6 Glossary................................................................ 52

14 机机械械、、封封装装和和可可订订购购信信息息....................................... 52

4 修修订订历历史史记记录录

注:之前版本的页码可能与当前版本有所不同。

Changes from Original (November 2015) to Revision A Page

• 已更改 器件状态,从

产品预览

更改为

生产数据

....................................................................................................................... 1

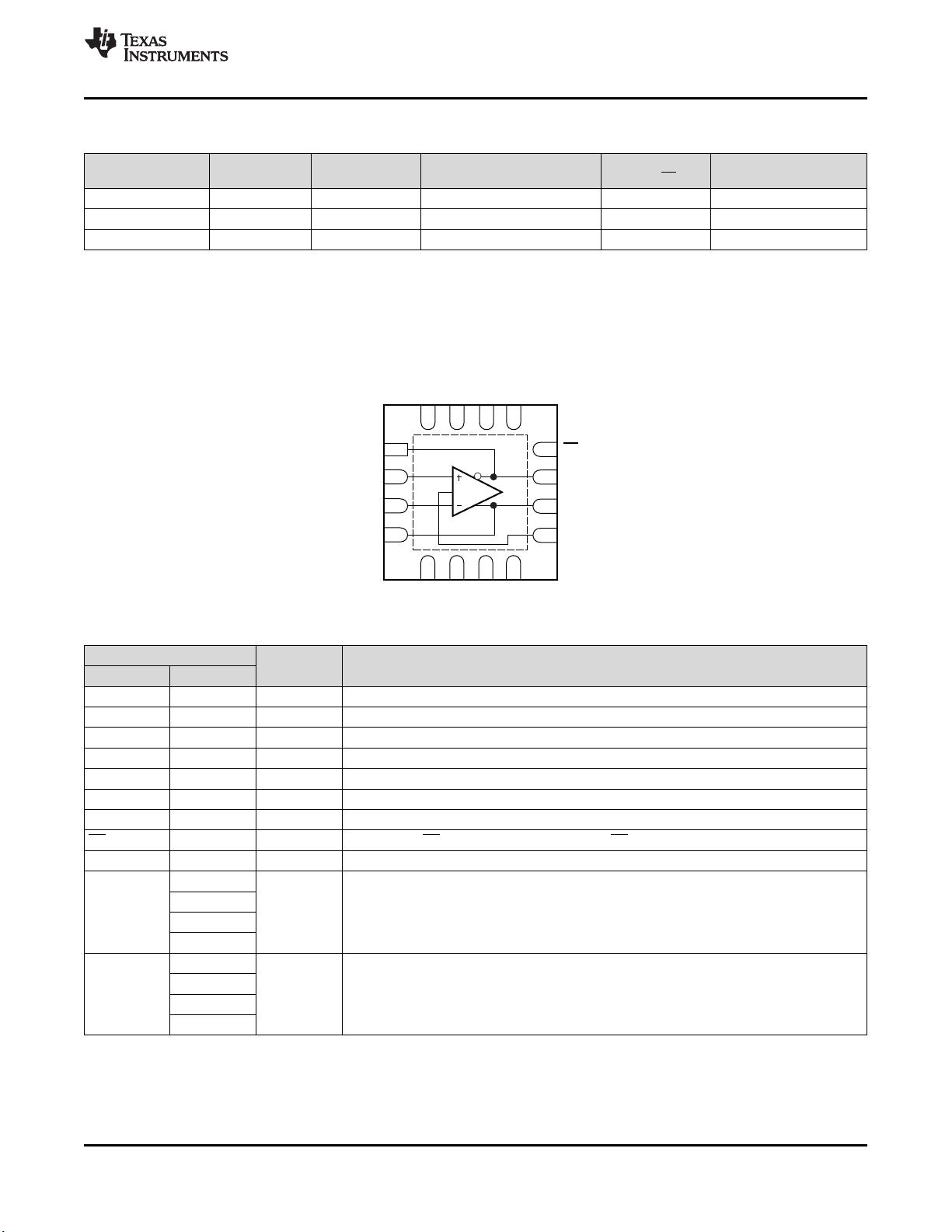

1315 1416

86 75

FB–

FB+

IN+

IN–

PD

OUT–

OUT+

Vocm

Vs–

Vs+

Vs–

Vs–

Vs–

Vs+

Vs+

Vs+

1

3

2

4

9

10

11

12

3

THS4541-Q1

www.ti.com.cn

ZHCSEK0A –NOVEMBER 2015–REVISED NOVEMBER 2015

Copyright © 2015, Texas Instruments Incorporated

5 Device Family Comparison

DEVICE BW (MHz) I

Q

(mA) THD (dBc) 2 V

PP

AT 100 kHz

INPUT NOISE

(nV/√Hz)

RAIL-TO-RAIL

THS4531A 36 0.25 –104 10 Out

THS4521 145 0.95 –102 4.6 Out

THS4520 620 14.2 –107 2 Out

(1) Solder the exposed thermal pad to a heat-spreading power or ground plane. This pad is electrically isolated from the die, but must be

connected to a power or ground plane and not floated.

6 Pin Configuration and Functions

RGT Package

16-Pin VQFN With Exposed Thermal Pad

Top View

Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

(1)

FB+ 4 O Noninverted (positive) output feedback

FB– 1 O Inverted (negative) output feedback

IN+ 2 I Noninverting (positive) amplifier input

IN– 3 I Inverting (negative) amplifier input

NC — — No internal connection

OUT+ 10 O Noninverted (positive) amplifier output

OUT– 11 O Inverted (negative) amplifier output

PD 12 I Power down. PD = logic low = power off mode; PD = logic high = normal operation.

Vocm 9 I Common-mode voltage input

Vs+

5

I Positive power-supply input

6

7

8

Vs–

13

I Negative power-supply input

14

15

16

4

THS4541-Q1

ZHCSEK0A –NOVEMBER 2015–REVISED NOVEMBER 2015

www.ti.com.cn

Copyright © 2015, Texas Instruments Incorporated

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

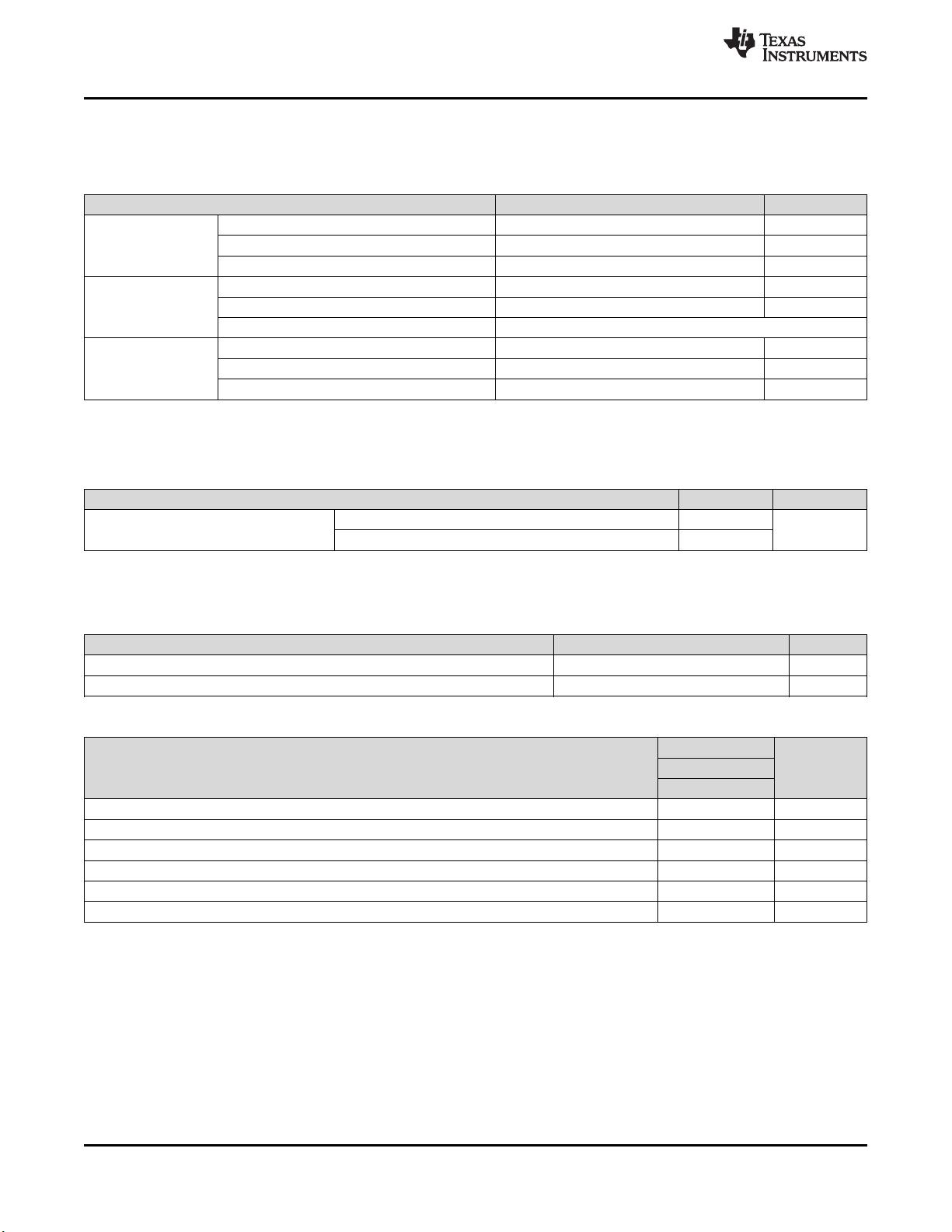

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)

MIN MAX UNIT

Voltage

Supply voltage, (Vs+) – Vs– 5.5 V

Input/output voltage range (Vs–) – 0.5 (Vs+) + 0.5 V

Differential input voltage ±1 V

Current

Continuous input current ±20 mA

Continuous output current ±80 mA

Continuous power dissipation See Thermal Information table and Thermal Analysis section

Temperature

Maximum junction temperature 150 °C

Operating free-air temperature range –40 125 °C

Storage temperature, T

stg

–65 150 °C

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

7.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human-body model (HBM), per AEC Q100-002

(1)

±2000

V

Charged-device model (CDM), per AEC Q100-011 ±1000

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

Vs+ Single-supply voltage 2.7 5 5.4 V

T

A

Ambient temperature –40 25 125 °C

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

7.4 Thermal Information

THERMAL METRIC

(1)

THS4541-Q1

UNITRGT (VQFN)

16 PINS

R

θJA

Junction-to-ambient thermal resistance 52 °C/W

R

θJC(top)

Junction-to-case (top) thermal resistance 69 °C/W

R

θJB

Junction-to-board thermal resistance 25 °C/W

ψ

JT

Junction-to-top characterization parameter 2.7 °C/W

ψ

JB

Junction-to-board characterization parameter 25 °C/W

R

θJC(bot)

Junction-to-case (bottom) thermal resistance 9.3 °C/W

5

THS4541-Q1

www.ti.com.cn

ZHCSEK0A –NOVEMBER 2015–REVISED NOVEMBER 2015

Copyright © 2015, Texas Instruments Incorporated

(1) Test levels (all values set by characterization and simulation): (A) 100% tested at T

A

≈ 25°C; over temperature limits by characterization

and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

(2) This slew rate is the average of the rising and falling time estimated from the large-signal bandwidth as: (V

P

/ √2) · 2π · f

–3dB

.

7.5 Electrical Characteristics: (Vs+) – Vs– = 5 V

At T

A

≈ 25°C, Vocm = open (defaults midsupply), V

OUT

= 2 V

PP

, Rf = 402 Ω, Rload = 499 Ω, 50-Ω input match, G = 2 V/V,

single-ended input, differential output, and PD = +Vs, unless otherwise noted. See Figure 61 for an AC-coupled gain of a 2-

V/V test circuit, and Figure 63 for a DC-coupled gain of a 2-V/V test circuit.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

TEST

LEVEL

(1)

AC PERFORMANCE

Small-signal bandwidth

Vout = 100 mV

PP

, G = 1 620 MHz C

Vout = 100 mV

PP

, G = 2 (see Figure 61) 500 MHz C

Vout = 100 mV

PP

, G = 5 210 MHz C

Vout = 100 mV

PP

, G = 10 125 MHz C

Gain-bandwidth product Vout = 100 mV

PP

, G = 20 850 MHz C

Large-signal bandwidth Vout = 2 V

PP

, G = 2 (see Figure 61) 340 MHz C

Bandwidth for 0.1-dB flatness Vout = 2 V

PP

, G = 2 (see Figure 61) 100 MHz C

Slew rate

(2)

Vout = 2-V

PP

, FPBW (see Figure 61) 1500 V/µs C

Rise/fall time

Vout = 2-V step, G = 2 input ≤ 0.3 ns t

r

(see Figure 63)

1.4 ns C

Settling time

To 1%, Vout = 2-V step, t

r

= 2 ns, G = 2

(seeFigure 63)

4 ns C

To 0.1%,Vout = 2-V step, t

r

= 2 ns, G = 2 (see

Figure 63)

8 ns C

Overshoot and undershoot

Vout = 2-V step G = 2, input ≤ 0.3 ns t

r

(see Figure 63)

10% C

100-kHz harmonic distortion

Vout = 2 V

PP

, G = 2, HD2 (see Figure 61) –140 dBc C

Vout = 2 V

PP

, G = 2, HD3 (see Figure 61) –140 dBc C

10-MHz harmonic distortion

Vout = 2 V

PP

, G = 2, HD2 (see Figure 61) –95 dBc C

Vout = 2 V

PP

, G = 2, HD3 (see Figure 61) –90 dBc C

2nd-order intermodulation

distortion

f = 10 MHz, 100-kHz tone spacing,

Vout envelope = 2 V

PP

(1 V

PP

per tone)

(see Figure 61)

–90 dBc C

3rd-order intermodulation

distortion

f = 10 MHz, 100-kHz tone spacing,

Vout envelope = 2 V

PP

(1 V

PP

per tone)

(see Figure 61)

–85 dBc C

Input voltage noise f > 100 kHz 2.2 nV/√Hz C

Input current noise f > 1 MHz 1.9 pA/√Hz C

Overdrive recovery time 2x output overdrive, either polarity 20 ns C

Closed-loop output impedance f = 10 MHz (differential) 0.1 Ω C

剩余64页未读,继续阅读

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0

最新资源