TI-SN74ACT2235-60FN.pdf

需积分: 0 178 浏览量

更新于2022-12-11

5

收藏 248KB PDF 举报

TI-SN74ACT2235是一款高性能的异步双向FIFO(First-In, First-Out)内存芯片,主要用于高速数据传输和独立的数据写入与读取操作。该芯片采用低功耗的先进CMOS技术制造,具备双1024位×9位的数据存储能力,能够提供快速的存取时间。

这款FIFO内存的独特之处在于其独立的异步输入和输出,这意味着写入和读取操作可以在不同的速度下独立进行,这对于处理不同速率的数据流非常有用。它还配备了可编程的“几乎满”/“几乎空”标志,以及空、满和半满标志,这些标志能帮助用户监控内存的状态,以便于实现高效的数据管理和同步。

SN74ACT2235具有25纳秒的存取时间,即使在50皮法负载条件下,也能达到25纳秒的访问速度,支持高达50MHz的数据速率,这使得它在高速数据处理应用中表现出色。此外,它还具备最长达22纳秒的最大下降时间,确保了数据传输的及时性。

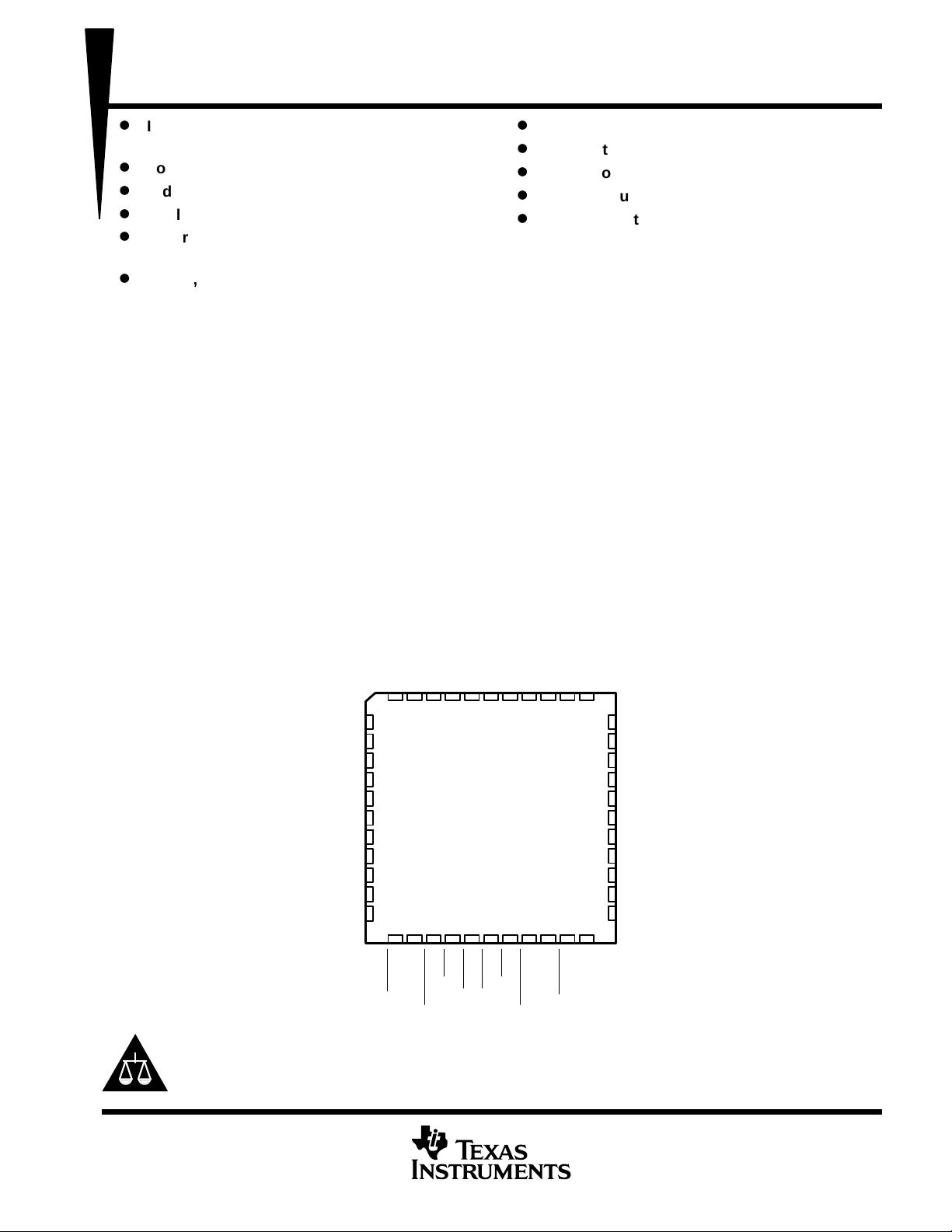

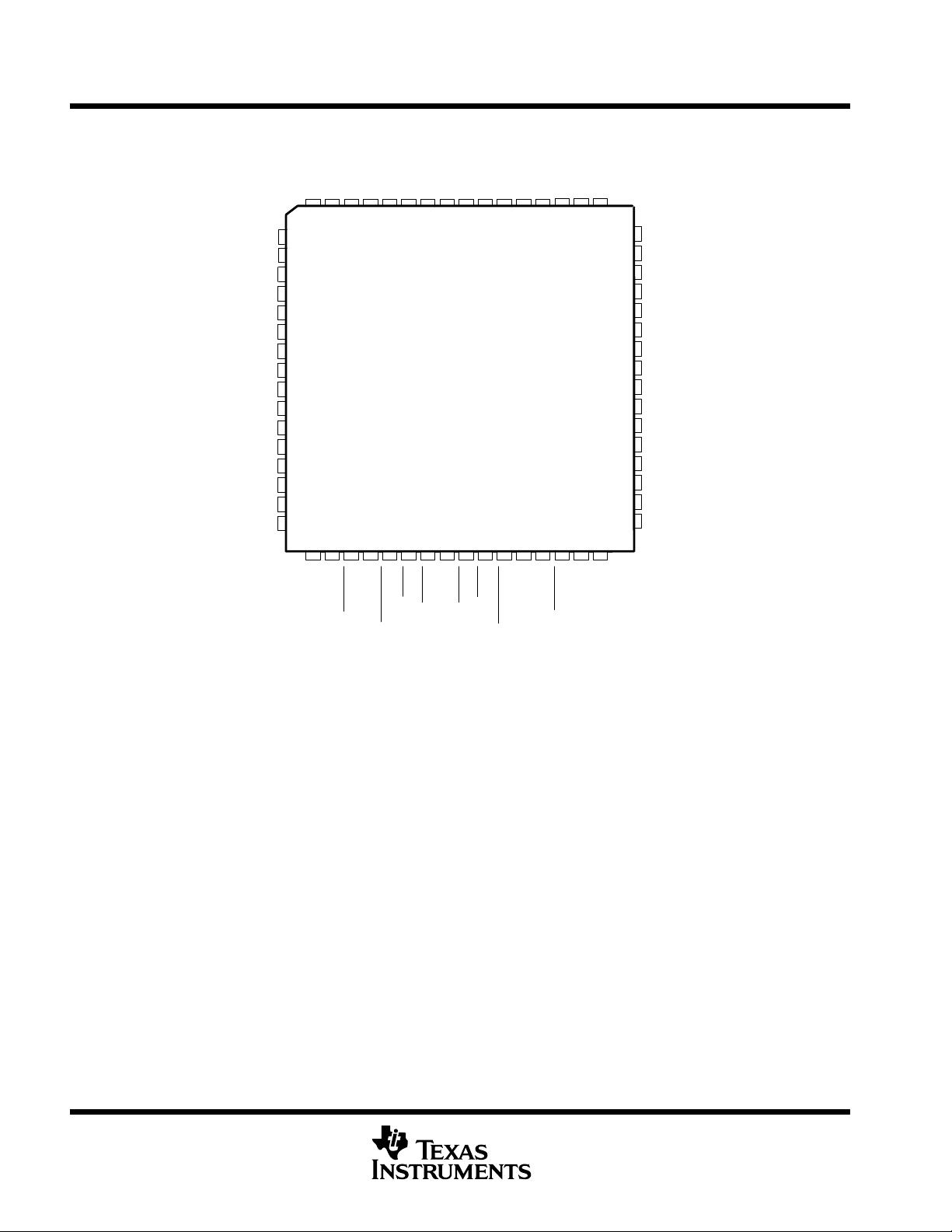

该器件还设计有高输出驱动能力,适合直接与总线接口,提供了44引脚塑封引脚芯片载体(FN)和64引脚薄型四边扁平封装(PAG, PM)等不同的封装选项,以适应不同的应用场景需求。

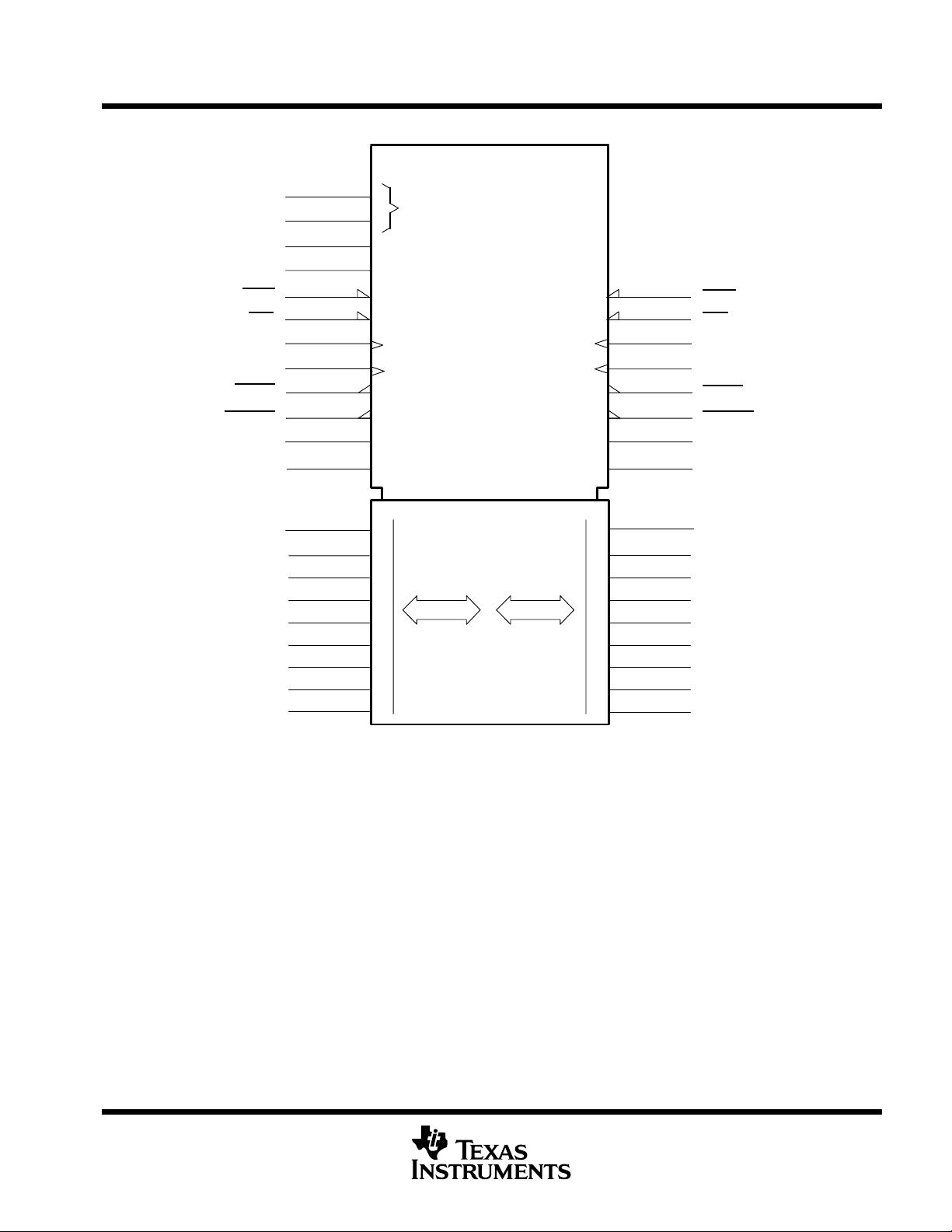

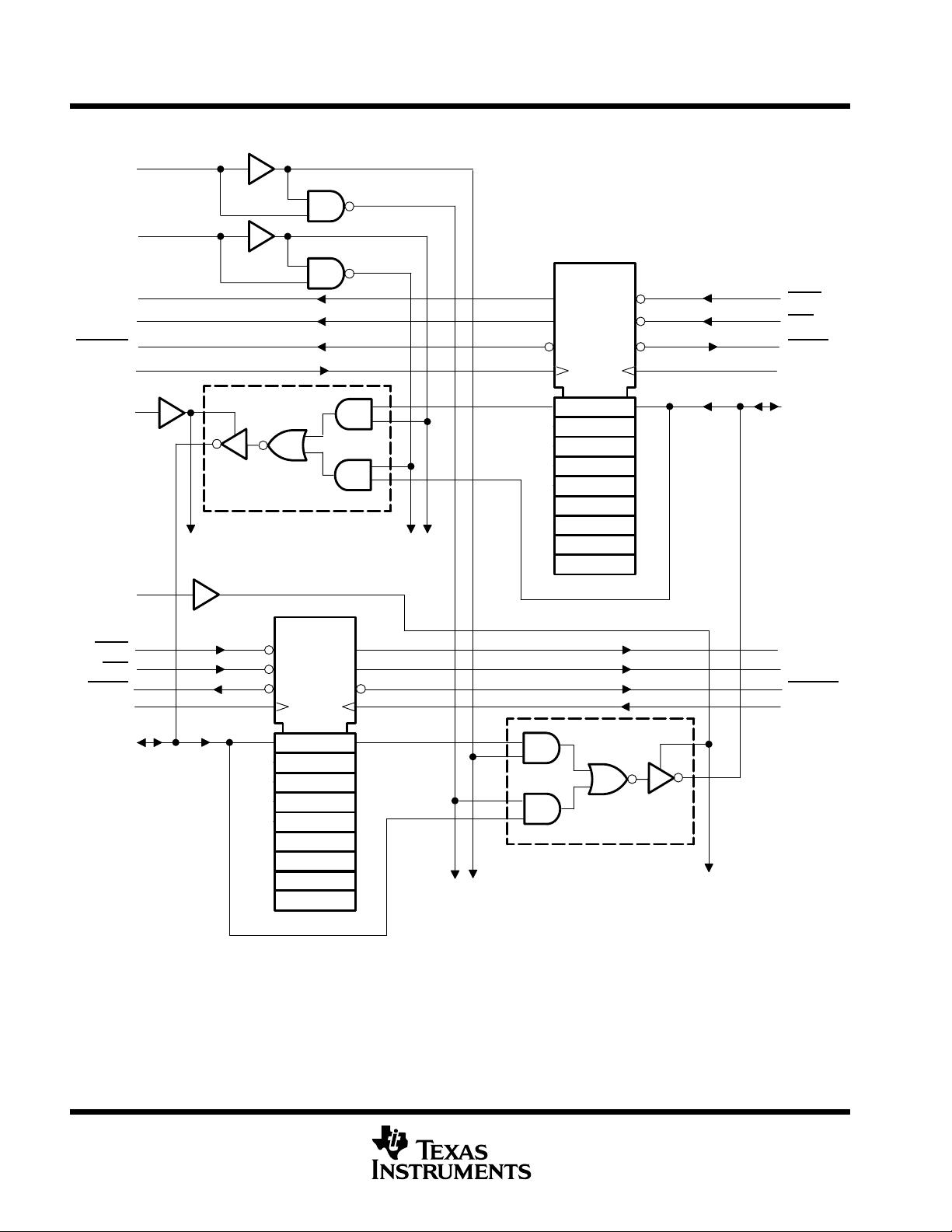

SN74ACT2235的内部结构包括总线转换器电路、两个1024位×9位的FIFO和控制电路。通过启用(GAB和GBA)输入可以控制转换器功能,而选择控制(SAB和SBA)输入则用于选择是实时传输数据还是从内部FIFO内存传输。这种选择控制电路消除了在存储数据和实时数据之间转换时通常出现的解码毛刺问题,提高了系统性能。

如图2所示,SN74ACT2235能够执行八种基本的总线管理功能,这使得它在各种复杂的系统环境中都能灵活地处理数据传输。为了获取更多关于该设备家族的信息,可以参考应用报告《1K × 9 × 2 Asynchronous FIFO SN74ACT2235》,文献编号SCAA010。

SN74ACT2235被规定在0°C至70°C的温度范围内工作,确保了其在广泛环境条件下的稳定性。该芯片的引脚布局包括VCC电源引脚、接地引脚(GND)、数据输入输出引脚(A0到A8和B0到B8)、控制信号引脚(如GAB、GNDB、AF/AE、LDA、CK等),以及状态标志引脚(如EMPTY、FULL等)。

TI-SN74ACT2235是一种高性能、低功耗的异步FIFO内存解决方案,适用于需要高速、高容量数据缓冲的应用,如通信、数据处理和工业自动化等领域。其强大的功能集、灵活的封装选项和广泛的温度操作范围使其成为许多现代电子系统设计的理想选择。

不觉明了

- 粉丝: 7423

- 资源: 5764

最新资源

- 基于微信小程序图书馆座位再利用系统-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于微信小程序校园订餐的设计与开发+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于微信小程序的科创微应用平台设计与实现+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- Python 实现粒子群优化(PSO)算法的深度置信网络(DBN)进行多输入单输出回归预测的实例(含完整的程序,GUI设计和代码详解)

- 基于小程序的物流管理系统---论文-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于小程序的购物系统设计与实现+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于微信小程序的教学质量评价系统ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- Python 实现贝叶斯优化卷积神经网络(BO-CNN)进行时间序列预测的详细项目实例(含完整的程序,GUI设计和代码详解)

- 基于小程序的老孙电子点菜系统开发设计与实现+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于微信小程序的社区垃圾回收管理系统ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- Python 项目实例,展示如何使用LSTM(长短期记忆)神经网络进行时间序列预测(含完整的程序,GUI设计和代码详解)

- 基于微信小程序的企业职工薪资查询系统设计与实现+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于微信小程序的商品展示+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于智能推荐的校园社区服务微信小程序_5x8ot-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于微信小程序的体育课评分系统+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- Python 实现BO-CNN(贝叶斯优化卷积神经网络)模型的详细项目实例(含完整的程序,GUI设计和代码详解)