没有合适的资源?快使用搜索试试~ 我知道了~

TI-SN74ACT7807.pdf

需积分: 9 0 下载量 108 浏览量

2022-12-11

13:58:32

上传

评论 5

收藏 205KB PDF 举报

温馨提示

试读

15页

TI-SN74ACT7807.pdf

资源推荐

资源详情

资源评论

SN74ACT7807

2048 × 9

CLOCKED FIRST-IN, FIRST-OUT MEMORY

SCAS200D – JANUARY 1991 – REVISED APRIL 1998

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Free-Running Read and Write Clocks Can

Be Asynchronous or Coincident

D

Read and Write Operations Synchronized

to Independent System Clocks

D

Input-Ready Flag Synchronized to Write

Clock

D

Output-Ready Flag Synchronized to Read

Clock

D

2048 Words by 9 Bits

D

Low-Power Advanced CMOS Technology

D

Programmable Almost-Full/Almost-Empty

Flag

D

Input-Ready, Output-Ready, and Half-Full

Flags

D

Cascadable in Word Width and/or Word

Depth

D

Fast Access Times of 12 ns With a 50-pF

Load

D

Data Rates up to 67 MHz

D

3-State Outputs

D

Package Options Include 44-Pin Plastic

Leaded Chip Carrier (FN) and 64-Pin Thin

Quad Flat (PAG, PM) Packages

description

The SN74ACT7807 is a 2048-word by 9-bit FIFO with high speed and fast access times. It processes data at

rates up to 67 MHz and access times of 12 ns in a bit-parallel format. Data outputs are noninverting with respect

to the data inputs. Expansion is easily accomplished in both word width and word depth.

The write-clock (WRTCLK) and read-clock (RDCLK) inputs should be free running and can be asynchronous

or coincident. Data is written to memory on the rising edge of WRTCLK when the write-enable (WRTEN1/DP9,

WRTEN2) inputs are high and the input-ready (IR) flag output is high. Data is read from memory on the rising

edge of RDCLK when the read-enable (RDEN1, RDEN2) and output-enable (OE) inputs are high and the

output-ready (OR) flag output is high. The first word written to memory is clocked through to the output buffer

regardless of the levels on RDEN1, RDEN2, and OE. The OR flag indicates that valid data is present on the

output buffer.

The FIFO can be reset asynchronous to WRTCLK and RDCLK. RESET

must be asserted while at least four

WRTCLK and four RDCLK cycles occur to clear the synchronizing registers. Resetting the FIFO initializes the

IR, OR, and half-full (HF) flags low and the almost-full/almost-empty (AF/AE) flag high. The FIFO must be reset

upon power up.

The SN74ACT7807 is characterized for operation from 0°C to 70°C.

Copyright 1998, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SN74ACT7807

2048 × 9

CLOCKED FIRST-IN, FIRST-OUT MEMORY

SCAS200D – JANUARY 1991 – REVISED APRIL 1998

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

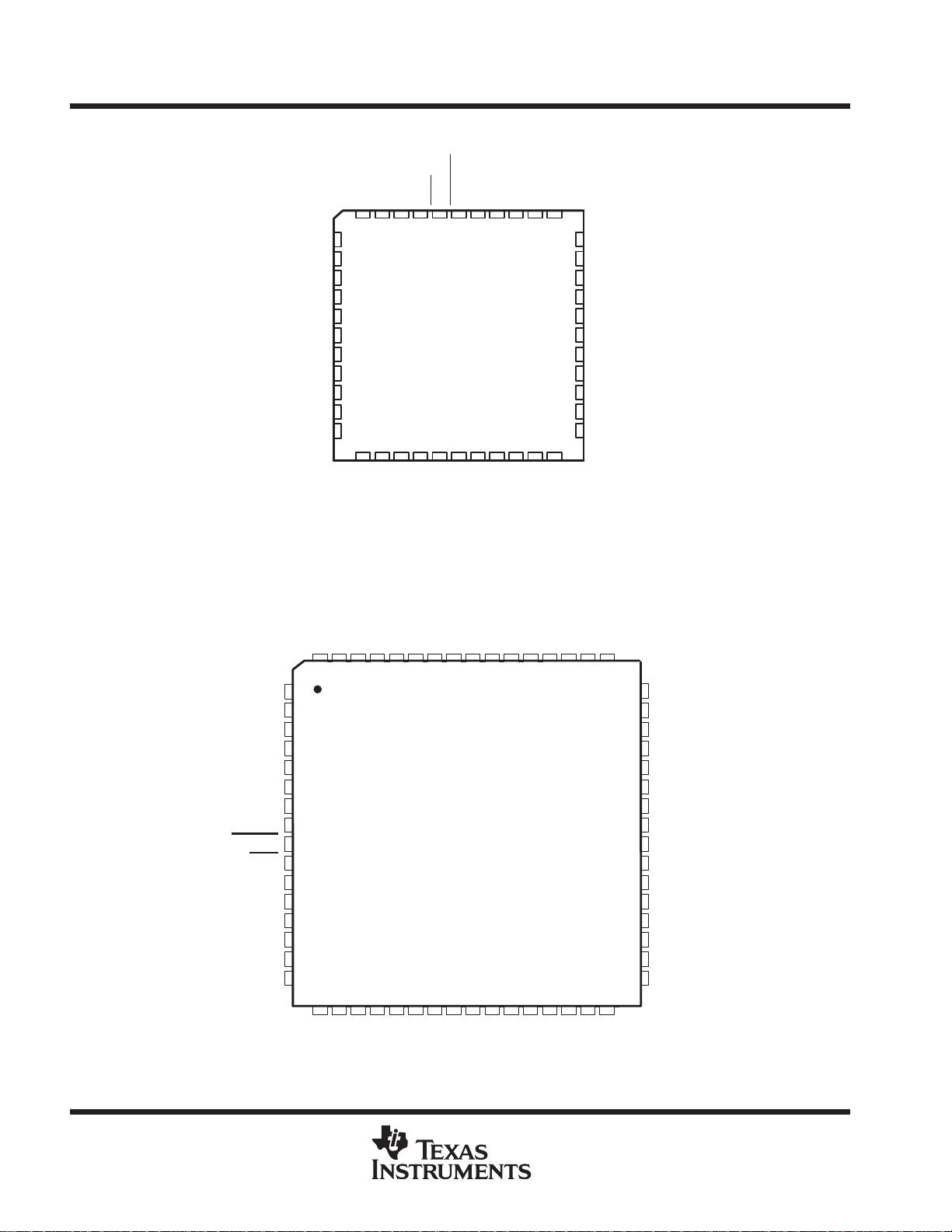

Q1

V

CC

Q2

Q3

GND

Q4

V

CC

Q5

Q6

GND

Q7

39

38

37

36

35

34

33

32

31

30

29

18 19

7

8

9

10

11

12

13

14

15

16

17

D0

D1

D2

GND

D3

D4

D5

V

CC

D6

D7

D8

20 21 22 23

FN PACKAGE

(TOP VIEW)

NC

OE

GND

Q0

54321644

HF

AF/AE

GND

PEN

RESET

RDEN1

RDCLK

Q8

GND

WRTCLK

WRTEN1/DP9

WRTEN2

IR

OR

RDEN2

42 41 4043

24 25 26 27 28

V

CC

V

CC

V

CC

Q2

GND

GND

Q3

Q4

Q5

Q6

GND

Q7

GND

NC

D1

D2

GND

GND

D4

D8

NC

NC

D0

D3

NC

D5

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

17 18 19 20 21 22 25 26 27 28 29 30 31 322423

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

D6

D7

Q1

PAG OR PM PACKAGE

(TOP VIEW)

NC

Q0

GND

GND

OE

NC

V

CC

V

CC

RESET

PEN

GND

GND

AF/AE

HF

V

CC

V

CC

NC

Q8

V

CC

V

CC

RDCLK

RDEN1

NC

RDEN2

OR

IR

WRTEN2

WRTEN1/DP9

WRTCLK

GND

GND

NC

NC – No internal connection

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

SN74ACT7807

2048 × 9

CLOCKED FIRST-IN, FIRST-OUT MEMORY

SCAS200D – JANUARY 1991 – REVISED APRIL 1998

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

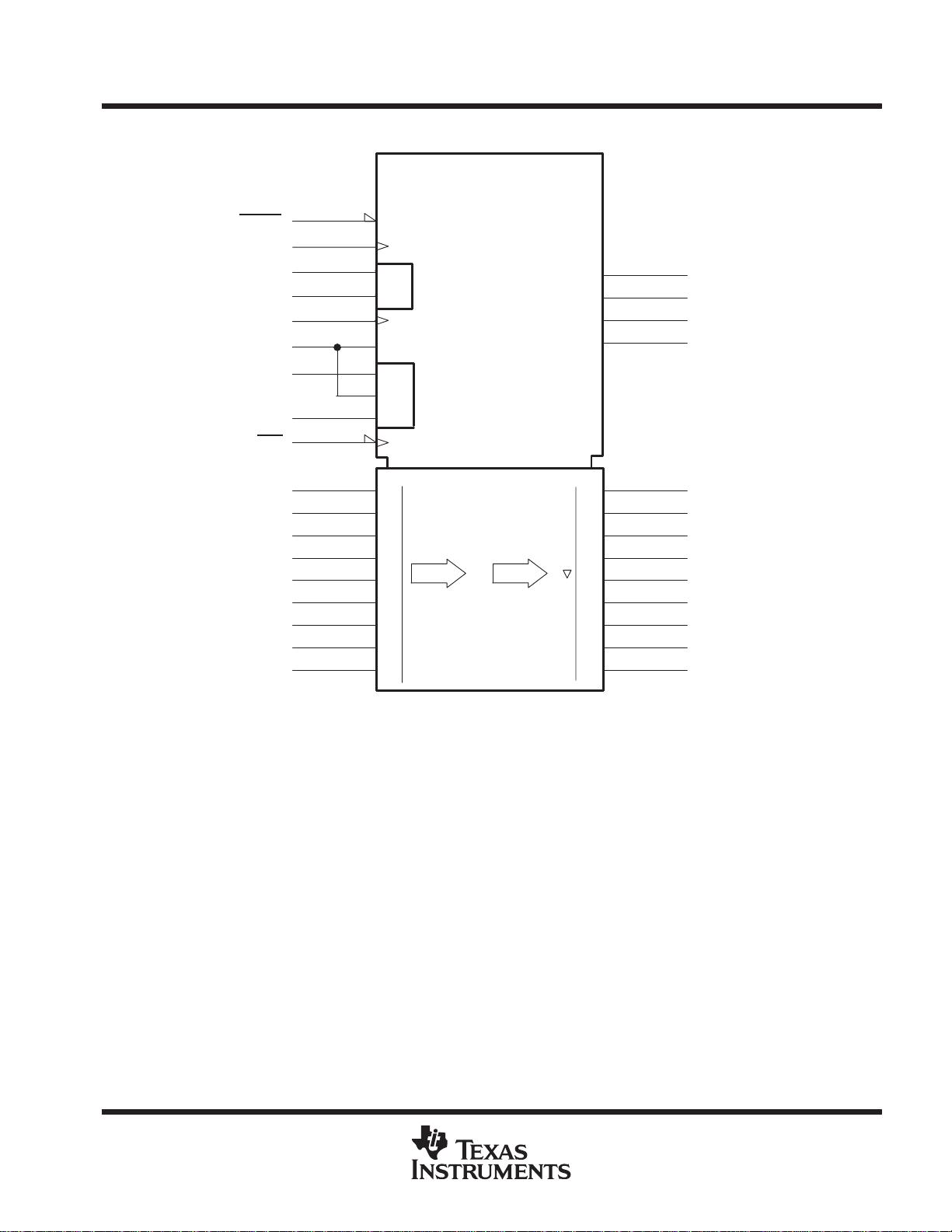

logic symbol

†

WRTEN

&

RDEN

&

0

7

D0

8

D1

9

D2

11

D3

12

D4

13

D5

15

D6

16

D7

8

17

D8

Q0

40

0

Q1

39

Q2

37

Q3

36

Q4

34

IR

22

IN RDY

HF

5

HALF FULL

AF/AE

4

ALMOST FULL/EMPTY

OR

23

OUT RDY

Q5

32

Q6

31

Q7

29

Q8

28

8

Data

1

RESET

25

RDEN1

EN1

42

OE

PEN

RESET

1

19

WRTCLK

WRTCLK

20

WRTEN1/DP9

21

WRTEN2

2

26

RDCLK

RDCLK

PROGRAM ENABLE

24

RDEN2

Data

Φ

FIFO 2048 × 9

SN74ACT7807

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the FN package.

剩余14页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3138

- 资源: 5392

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功