没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS90CP04.pdf

需积分: 5 0 下载量 155 浏览量

2022-12-03

09:47:04

上传

评论 4

收藏 948KB PDF 举报

温馨提示

试读

24页

TI-DS90CP04.pdf

资源推荐

资源详情

资源评论

IN1+

IN1-

IN2+

IN2-

IN3+

IN3-

IN4+

IN4-

OUT1+

OUT1-

OUT2+

OUT2-

OUT3+

OUT3-

OUT4+

OUT4-

SCLK

SI/SEL1

CSO

CSCLK

EN1 EN2 EN3 EN4

4:1 MUX1

4:1 MUX2 4:1 MUX3

4:1 MUX4

LOAD

MODE

Digital Control

Interface

RSO

RSCLK

SEL0

DS90CP04

www.ti.com

SNLS154I –JANUARY 2002–REVISED APRIL 2013

DS90CP04 1.5 Gbps 4x4 LVDS Crosspoint Switch

Check for Samples: DS90CP04

1

FEATURES

DESCRIPTION

DS90CP04 is a 4x4 digital cross-point switch with

2

• DC - 1.5 Gbps Low Jitter, Low Skew Operation

broadside input and output pins for efficient board

• Pin and Serial Interface Configurable, Fully

layout. It utilizes Low Voltage Differential Swing

Differential, Non-blocking Architecture

(LVDS) technology for low power, high-speed

• Wide Input Common Mode Voltage Range

operation. Data paths are fully differential from input

to output for low noise. The non-blocking architecture

Enables Easy Interface to LVDS/LVPECL/2.5V-

allows connections of any input to any output or

CML Drivers

outputs. The switch matrix consists of four differential

• TRI-STATE LVDS Outputs

4:1 multiplexes. Each output channel connects to one

• Serial Control Interface with Read-back

of the four inputs common to all multiplexers.

Capability

A simple serial control interface or a configuration

• Double Register Loading

select port is activated by the state of the MODE pin.

• Single +2.5V Supply

When utilizing the serial control interface a single

load command will update the new switch

• Small 6x6 mm WQFN-32 Space Saving

configuration for all outputs simultaneously.

Package

• Fabricated with Advanced CMOS Process

Technology

Functional Block Diagrams

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2002–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

SCLK

SI/SEL1

CSCLK

CSO

RSCLK

RSO

LOAD

MODE

INPUT

REGISTER

CLOCK AND

CONTROL

ROW

DECREMENT

COLUMN

DECREMENT

LOAD

REGISTER

ROW

OUTPUT

REGISTER

COLUMN

OUTPUT

REGISTER

SWITCH

CONFIGURATION

REGISTER

DIGITAL CONTROL INTERFACE

SEL0

DS90CP04

SNLS154I –JANUARY 2002–REVISED APRIL 2013

www.ti.com

Figure 1. Functional Block Diagram

2 Submit Documentation Feedback Copyright © 2002–2013, Texas Instruments Incorporated

Product Folder Links: DS90CP04

17 18 19 20 21 2322 24

25

26

27

28

29

30

31

32

16

15

14

13

12

11

10

9

8 7 6 5 4 23 1

DS90CP04

WQFN-32

6x6x0.75mm body size

0.5mm pitch

Top View Shown

DAP = GND

VDD

SCLK

RSO

SEL0

VDD

RSCLK

SI/SEL1

GND

OUT4-

OUT1+

OUT1-

OUT2+

OUT2-

OUT3+

OUT3-

OUT4+

IN4-

IN4+

IN3-

IN3+

IN2-

IN2+

IN1-

IN1+

CSO

MODE

VDD

CSCLK

LOAD

GND

VDD

GND

DS90CP04

www.ti.com

SNLS154I –JANUARY 2002–REVISED APRIL 2013

Connection Diagram

Figure 2. Connection Diagram - 32 Pin (Top View)

See Package Number NJE0032A

PIN DESCRIPTIONS

Pin Pin

I/O, Type Description

Name Number

DIFFERENTIAL INPUTS COMMON TO ALL MUXES

IN1+ 16 I, LVDS Inverting and non-inverting differential inputs.

IN1− 15

IN2+ 14 I, LVDS Inverting and non-inverting differential inputs.

IN2− 13

IN3+ 12 I, LVDS Inverting and non-inverting differential inputs.

IN3− 11

IN4+ 10 I, LVDS Inverting and non-inverting differential inputs.

IN4− 9

SWITCHED DIFFERENTIAL OUTPUTS

OUT1+ 25 O, LVDS Inverting and non-inverting differential outputs. OUT1± can be connected to any one pair

OUT1− 26 IN1±, IN2±, IN3±, or IN4±

OUT2+ 27 O, LVDS Inverting and non-inverting differential outputs. OUT2± can be connected to any one pair

OUT2− 28 IN1±, IN2±, IN3±, or IN4±

OUT3+ 29 O, LVDS Inverting and non-inverting differential outputs. OUT3± can be connected to any one pair

OUT3− 30 IN1±, IN2±, IN3±, or IN4

OUT4+ 31 O, LVDS Inverting and non-inverting differential outputs. OUT4± can be connected to any one pair

OUT4− 32 IN1±, IN2±, IN3±, or IN4±

Copyright © 2002–2013, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: DS90CP04

DS90CP04

SNLS154I –JANUARY 2002–REVISED APRIL 2013

www.ti.com

PIN DESCRIPTIONS (continued)

Pin Pin

I/O, Type Description

Name Number

DIGITAL CONTROL INTERFACE

SCLK 6 I, LVCMOS Control clock to latch in programming data at SI. SCLK can be 0 MHz to 100 MHz. SCLK

should be burst of clock pulses active only while accessing the device. After completion of

programming, SCLK should be kept at logic low to minimize potential noise injection into

the high-speed differential data paths.

SI / SEL1 7 I, LVCMOS Programming data to select the switch configuration. Data is latched into the input buffer

register at the rising edge of SCLK.

SEL0 5 I, LVCMOS Programming data to select the switch configuration.

CSO 18 O, LVCMOS With MODE low, control data is shifted out at CSO (RSO) for cascading to the next device

RSO 2 in the serial chain. The control data at CSO (RSO) is identical to that shifted in at SI with

the exception of the device column (row) address being decremented by one internally

before propagating to the next device in the chain. CSO (RSO) is clocked out at the rising

edge of SCLK.

CSCLK 19 O, LVCMOS With MODE low, these pins function as a buffered control clock from SCLK. CSCLK

RSCLK 3 (RSCLK) is used for cascading the serial control bus to the next device in the serial chain.

LOAD 22 I, LVCMOS When LOAD is high and SCLK makes a LH transition, the device transfers the

programming data in the load register into the configuration registers. The new switch

configuration for all outputs takes effect. LOAD needs to remain high for only one SCLK

cycle to complete the process, holding LOAD high longer repeats the transfer to the

configuration register.

MODE 23 I, LVCMOS When MODE is low, the SCLK is active and a buffered SCLK signal is present at the

CLKOUT output. When MODE is high, the SCLK signal is uncoupled from register and

state machine internals. Internal registers will see an active low signal until MODE is

brought Low again.

POWER

V

DD

1, 8, 17, I, Power V

DD

= 2.5V ±5%. At least 4 low ESR 0.01 µF bypass capacitors should be connected from

24 V

DD

to GND plane.

GND 4, 20, 21, I, Power Ground reference to LVDS and CMOS circuitry.

DAP DAP is the exposed metal contact at the bottom of the WQFN-32 package. The DAP is

used as the primary GND connection to the device. It should be connected to the ground

plane with at least 4 vias for optimal AC and thermal performance.

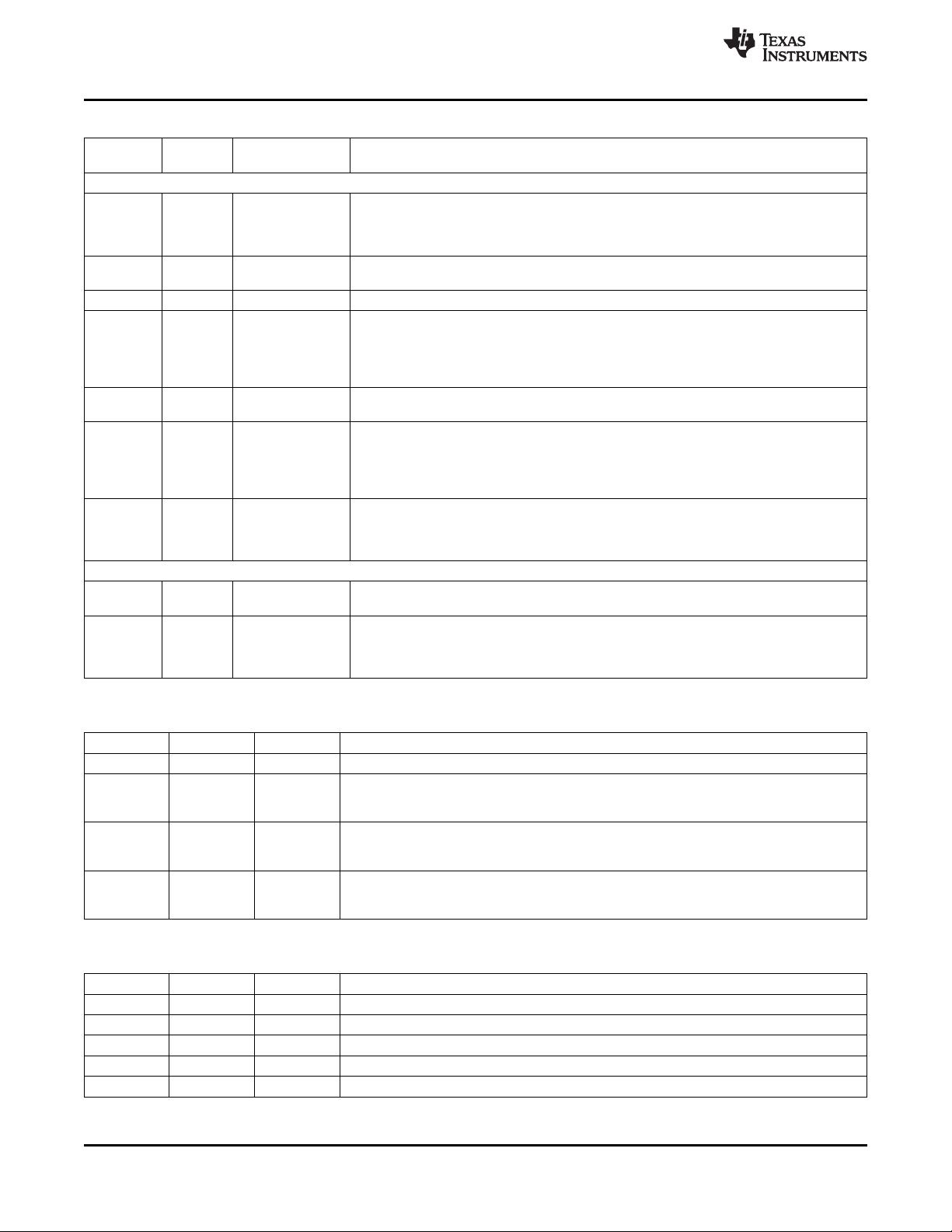

Serial Interface Truth Table

LOAD MODE SCLK Resulting Action

0 0 LH The current state on SI is clocked into the input shift register.

0 1 LH Uncouples SCLK input from internal registers and state machine inputs. The RSCLK and

CSCLK outputs will drive an active Low signal until MODE is brought Low again. See

Configuration Select Truth Table below.

LH 0 X Loads OUT1–OUT4 configuration information from last valid frame. Places contents of load

register into the configuration register. The switch configuration is updated asynchronously

from the SCLK input.

1 1 LH Uncouples SCLK input from internal registers and state machine inputs. The RSCLK and

CSCLK outputs will drive an active Low signal until MODE is brought Low again. See

Configuration Select Truth Table below.

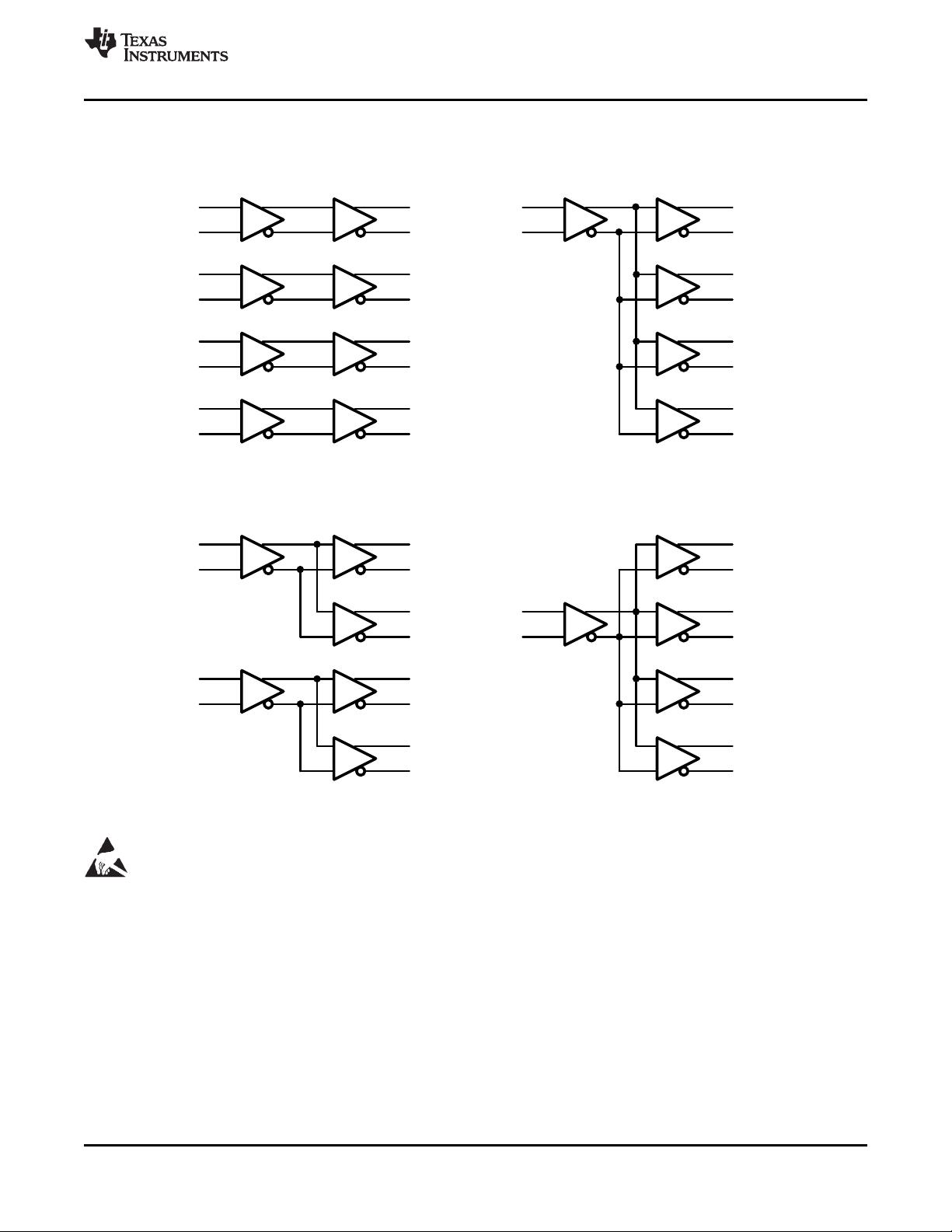

Configuration Select Truth Table

MODE SEL1 SEL0 Resulting Action

0 X X The SEL0/1 pins only function in configuration select mode. See below.

1 0 0 Distribution: IN1 - OUT1 OUT2 OUT3 OUT4

1 0 1 Distribution: IN2 - OUT1 OUT2 OUT3 OUT4

1 1 0 Redundancy: IN1 - OUT1 OUT2 and IN3 - OUT3 OUT4

1 1 1 Broadside: IN1 - OUT1, IN2 - OUT2, IN3 - OUT3, IN4 - OUT4

4 Submit Documentation Feedback Copyright © 2002–2013, Texas Instruments Incorporated

Product Folder Links: DS90CP04

IN1+

IN1-

OUT1+

OUT1-

OUT2+

OUT2-

OUT3+

OUT3-

OUT4+

OUT4-

IN2+

IN2-

IN3+

IN3-

IN4+

IN4-

IN1+

IN1-

OUT1+

OUT1-

OUT2+

OUT2-

OUT3+

OUT3-

OUT4+

OUT4-

IN1+

IN1-

OUT1+

OUT1-

OUT2+

OUT2-

OUT3+

OUT3-

OUT4+

OUT4-

IN3+

IN3-

OUT1+

OUT1-

OUT2+

OUT2-

OUT3+

OUT3-

OUT4+

OUT4-

IN2+

IN2-

SEL0 = 1

SEL1 = 1

SEL0 = 1

SEL1 = 0

SEL0 = 0

SEL1 = 0

SEL0 = 0

SEL1 = 1

DS90CP04

www.ti.com

SNLS154I –JANUARY 2002–REVISED APRIL 2013

Figure 3. DS90CP04 Configuration Select Decode

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Copyright © 2002–2013, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Links: DS90CP04

剩余23页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3175

- 资源: 5443

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功