没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS64EV100.pdf

需积分: 5 0 下载量 97 浏览量

2022-12-04

00:17:44

上传

评论 3

收藏 1.59MB PDF 举报

温馨提示

试读

16页

TI-DS64EV100.pdf

资源详情

资源评论

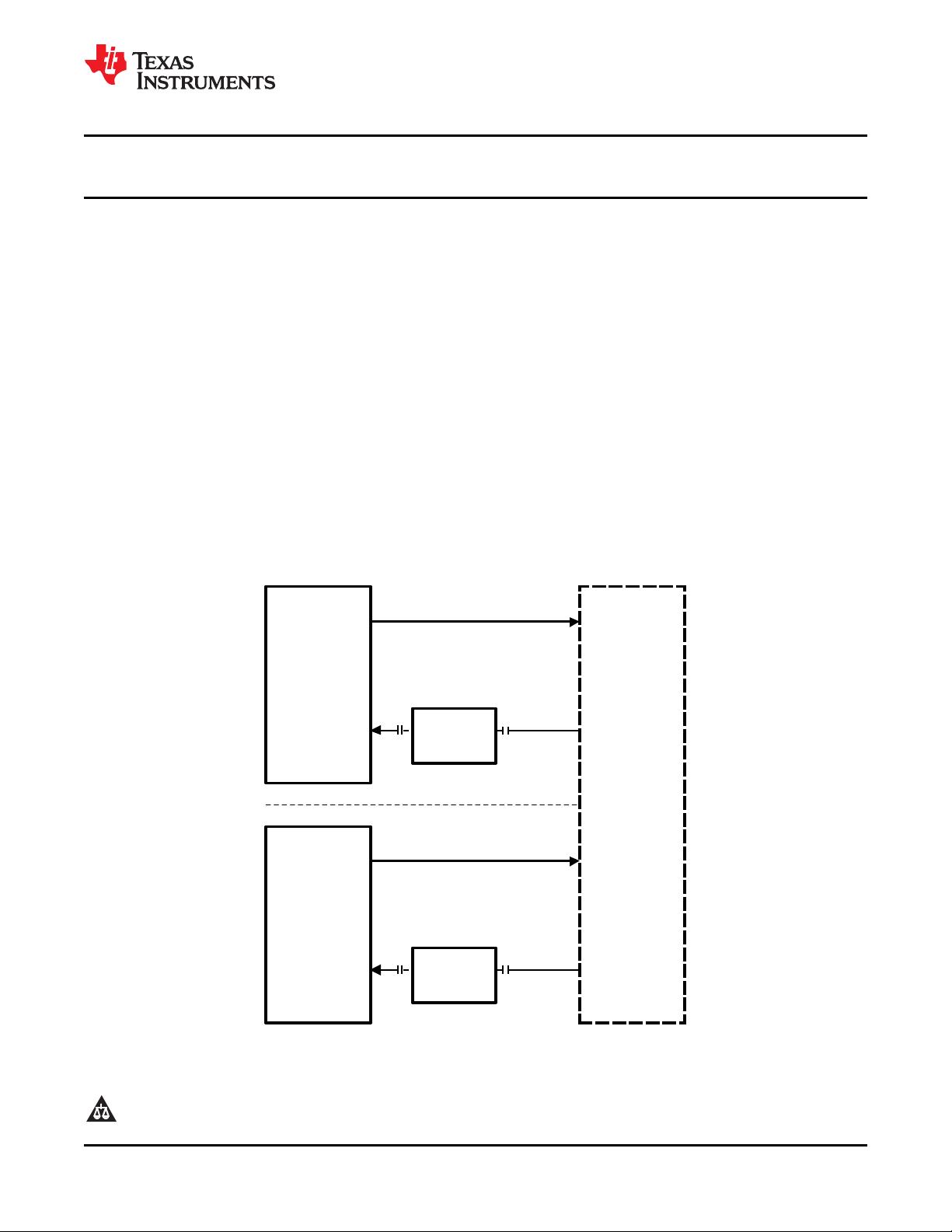

ASIC/FPGA

High Speed

I/O

Backplane/Cable

Sub-system

Switch Fabric Card

Line Card

OUT IN

DS64EV100

OUT IN

Tx

Tx

Rx

Rx

ASIC/FPGA

High Speed

I/O

DS64EV100

DS64EV100

www.ti.com

SNLS232E –OCTOBER 2006–REVISED FEBRUARY 2013

DS64EV100 Programmable Single Equalizer

Check for Samples: DS64EV100

1

FEATURES

DESCRIPTION

The DS64EV100 programmable equalizer provides

2

• Equalizes up to 24 dB loss at 10 Gbps

compensation for transmission medium losses and

• Equalizes up to 22 dB loss at 6.4 Gbps

reduces the medium-induced deterministic jitter for

• 8 levels of programmable equalization

NRZ data channel. The DS64EV100 is optimized for

operation up to 10 Gbps for both cables and FR4

• Operates up to 10 Gbps with 30” FR4 traces

traces. The equalizer channel has eight levels of

• Operates up to 6.4 Gbps with 40” FR4 traces

input equalization that can be programmed by three

• 0.175 UI residual deterministic jitter at 6.4

control pins.

Gbps with 40” FR4 traces

The equalizer supports both AC and DC-coupled data

• Single 2.5V or 3.3V power supply

paths for long run length data patterns such as

• Supports AC or DC-Coupling with wide input

PRBS-31, and balanced codes such as 8b/10b. The

device uses differential current-mode logic (CML)

common-mode

inputs and outputs. The DS64EV100 is available in a

• Low power consumption: 100 mW Typ at 2.5V

3 mm x 4 mm 14-pin leadless WSON package.

• Small 3 mm x 4 mm 14-pin WSON package

Power is supplied from either a 2.5V or 3.3V supply.

• > 8 kV HBM ESD Rating

• -40 to 85°C operating temperature range

Simplified Application Diagram

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2006–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

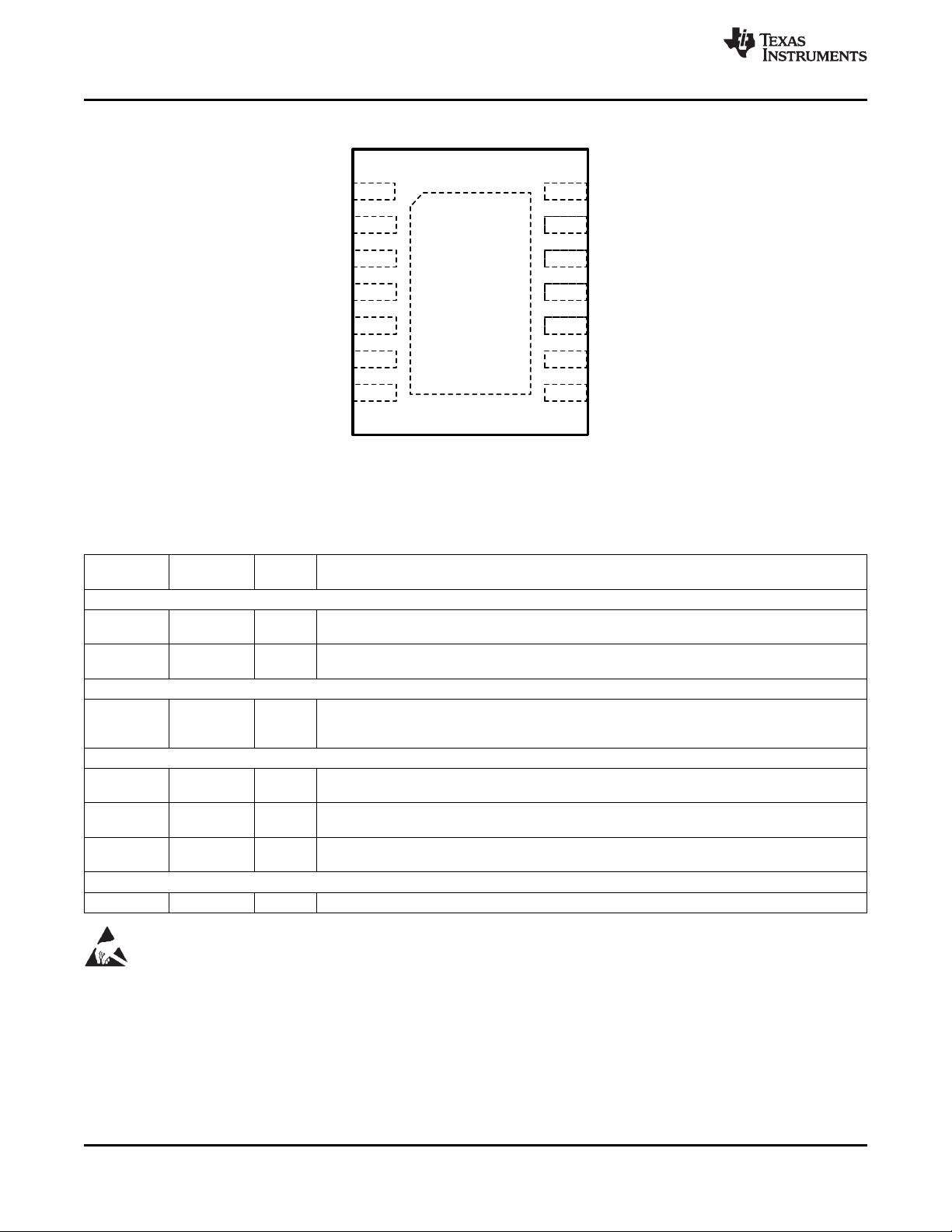

1

2

3

4

5

6

7

14

13

12

11

10

9

8

IN+

IN-

VDD

GND

GND

BST_1

NC BST_2

GND

OUT_+

OUT_-

GND

GND

BST_0

DS64EV100

TOP VIEW

DAP = GND

DS64EV100

SNLS232E –OCTOBER 2006–REVISED FEBRUARY 2013

www.ti.com

Pin Diagram

Figure 1. 14-Pin WSON Package

(3 mm x 4 mm x 0.8 mm, 0.5 mm pitch)

See Package Number NHK0014A

Table 1. Pin Descriptions

I/O,

Pin Name Pin # Description

Type

HIGH SPEED DIFFERENTIAL I/O

IN+ 3 I, CML Inverting and non-inverting CML differential inputs to the equalizer. An on-chip 100Ω terminating

IN− 4 resistor is connected between IN+ and IN-. Refer to Figure 4.

OUT+ 12 O, CML Inverting and non-inverting CML differential outputs from the equalizer. An on-chip 50Ω

OUT− 11 terminating resistor connects OUT+ to V

DD

and OUT- to V

DD

.

EQUALIZATION CONTROL

BST_2 14 I, CMOS BST_2, BST_1, and BST_0 select the equalizer strength. BST_2 is internally pulled high. BST_1

BST_1 7 and BST_0 are internally pulled low.

BST_0 8

POWER

V

DD

5 I, Power V

DD

= 2.5V ±5% or 3.3V ±10%. V

DD

pins should be tied to V

DD

plane through low inductance

path. A 0.01μF bypass capacitor should be connected between each V

DD

pin to GND planes.

GND 2, 6, 9, 10, I, Power Ground reference. GND should be tied to a solid ground plane through a low impedance path.

13

DAP PAD I, Power Ground reference. The exposed pad at the center of the package must be connected to ground

plane of the board.

OTHER

NC 1 Reserved. Do not connect.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

2 Submit Documentation Feedback Copyright © 2006–2013, Texas Instruments Incorporated

Product Folder Links: DS64EV100

DS64EV100

www.ti.com

SNLS232E –OCTOBER 2006–REVISED FEBRUARY 2013

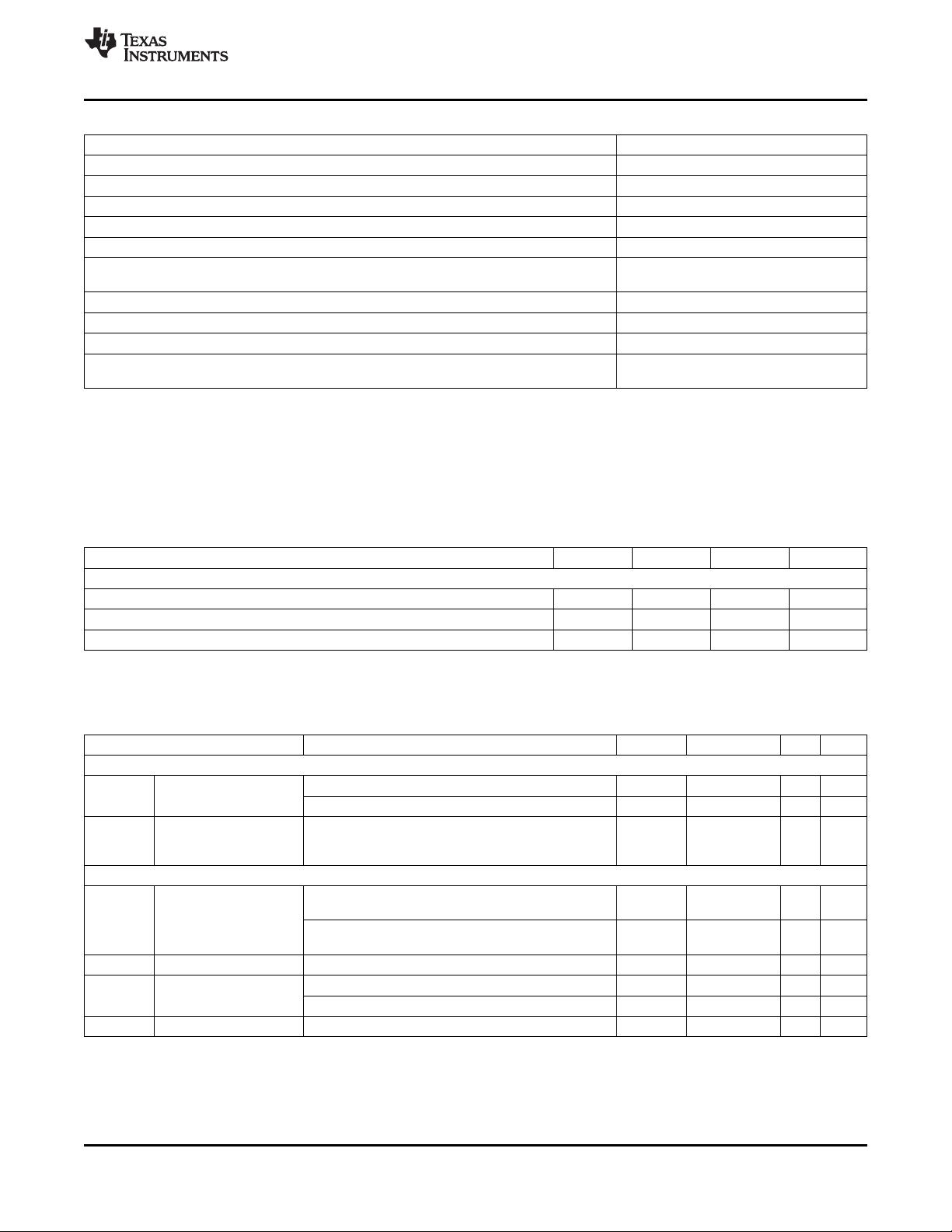

Absolute Maximum Ratings

(1)(2)

Supply Voltage (V

DD

) −0.5V to +4V

CMOS Input Voltage −0.5V to +4.0V

CMOS Output Voltage −0.5V to +4.0V

CML Input/Output Voltage −0.5V to +4.0V

Junction Temperature +150°C

Storage Temperature −65°C to +150°C

Lead Temperature

Soldering, 4 sec +260°C

ESD Rating

HBM, 1.5 kΩ, 100 pF > 8 kV

EIAJ, 0Ω, 200 pF > 250 V

Thermal Resistance, θ

JA

,

No Airflow 40 °C/W

(1) “Absolute Maximum Ratings” indicate limits beyond which damage to the device may occur, including inoperability and degradation of

device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or

other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating

Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. Absolute

Maximum Numbers are guaranteed for a junction temperature range of –40°C to +125°C. Models are validated to Maximum Operating

Voltages only.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office / Distributors for

availability and specifications.

Recommended Operating Conditions

MIN TYP MAX UNIT

Supply Voltage

(1)

V

DD2.5

to GND 2.375 2.5 2.625 V

V

DD3.3

to GND 3.0 3.3 3.6 V

Ambient Temperature −40 25 +85 °C

(1) The V

DD2.5

is V

DD

= 2.5V ± 5% and V

DD3.3

is V

DD

= 3.3V ± 10%.

Electrical Characteristics

Over recommended operating supply and temperature ranges unless other specified.

(1) (2)

PARAMETER TEST CONDITIONS MIN TYP

(1)

MAX UNIT

POWER

V

DD3.3

140 200 mW

Power Supply

P

Consumption

V

DD2.5

100 150 mW

50 Hz – 100 Hz 100 mV

P-P

Supply Noise Tolerance

N 100 Hz – 10 MHz 40 mV

P-P

(3)

10 MHz – 1.6 GHz 10 mV

P-P

LVTTL DC SPECIFICATIONS

V

DD2.

V

DD2.5

1.6 V

5

V

IH

High Level Input Voltage

V

DD3.

V

IL

2.0 V

3

V

IL

Low Level Input Voltage −0.3 0.8 V

I

OH

= –3 mA, V

DD3.3

2.4 V

V

OH

High Level Input Voltage

I

IN

2.0 V

V

OL

Low Level Input Voltage I

OL

= 3 mA 0.4 V

(1) Typical values represent most likely parametric norms at V

DD

= 3.3V or 2.5V, T

A

= 25°C., and at the Recommended Operation

Conditions at the time of product characterization and are not guaranteed.

(2) The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as

otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and

are not guaranteed.

(3) Allowed supply noise (mV

P-P

sine wave) under typical conditions.

Copyright © 2006–2013, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: DS64EV100

DS64EV100

SNLS232E –OCTOBER 2006–REVISED FEBRUARY 2013

www.ti.com

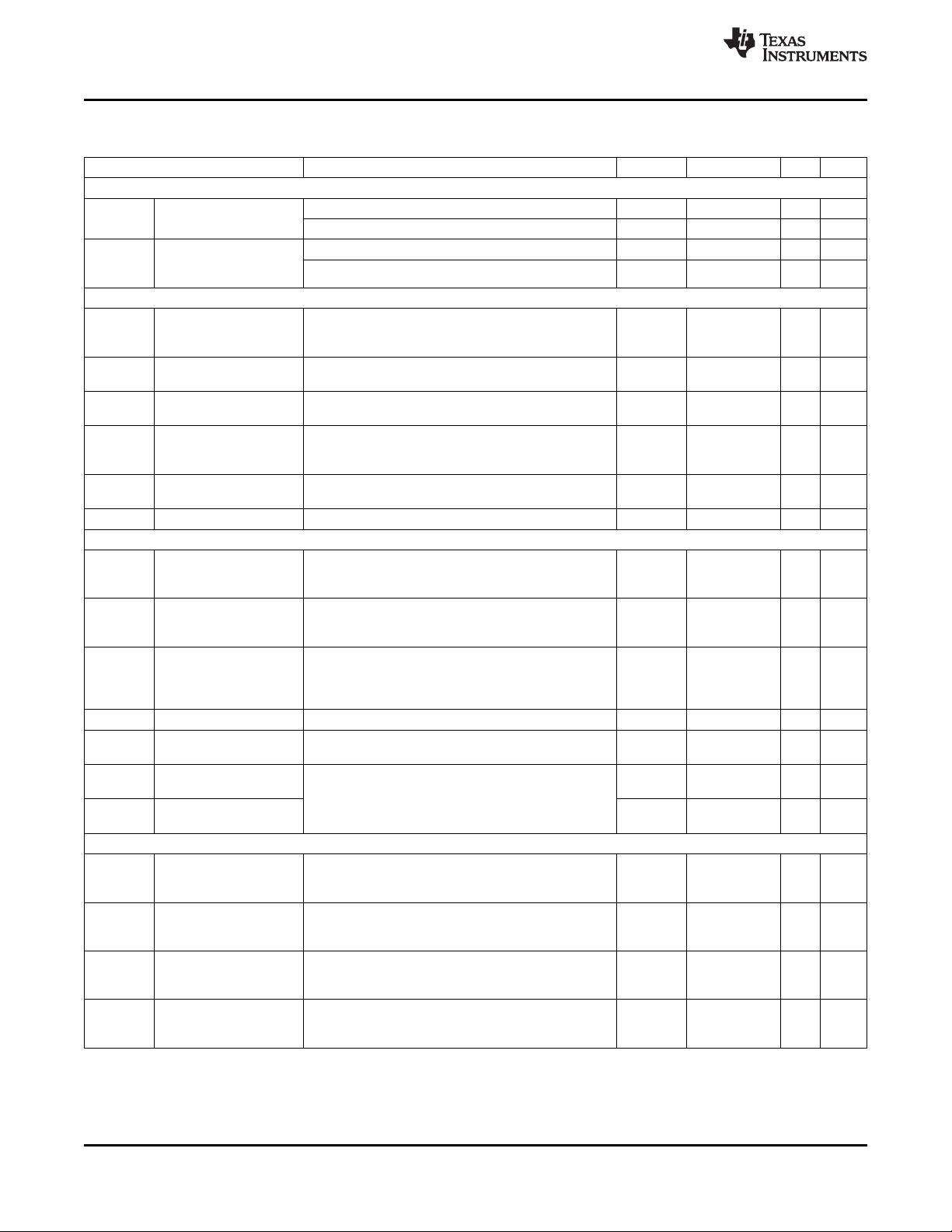

Electrical Characteristics (continued)

Over recommended operating supply and temperature ranges unless other specified.

(1) (2)

PARAMETER TEST CONDITIONS MIN TYP

(1)

MAX UNIT

POWER

V

IN

= V

DD

+1.8 +15 µA

I

IN

Input Current

V

IN

= GND −15 0 µA

Input Leakage Current V

IN

= GND, with internal pull-down resistors +95 µA

I

IN-P

with Internal Pull-

V

IN

= GND, with internal pull-up resistors –20 µA

Down/Up Resistors

CML RECEIVER INPUTS (IN+, IN−)

AC-Coupled or DC-Coupled Requirement, Differential

Source Transmit Launch

V

TX

measurement at point A. 400 1600 mV

P-P

Signal Level (IN diff)

Figure 1

Differential measurement at point B .

V

INTRE

Input Threshold Voltage 120 mV

P-P

Figure 1

Supply Voltage of

V

DDTX

DC-Coupled Requirement 1.6 V

DD

V

Transmitter to EQ

DC-Coupled Requirement Differential measurement at

Input Common-Mode V

DDT

V

ICMDC

point A. V

DDTX

-0.8 V

Voltage

X

-0.2

Figure 1

(4)

Differential Input Return

R

LI

100 MHz – 3.2 GHz, with fixture’s effect de-embedded 10 dB

Loss

R

IN

Input Resistance Differential Across IN+ and IN-. Figure 4 85 100 115 Ω

CML OUTPUTS (OUT+, OUT−)

Differential measurement with OUT+ and OUT-

Output Differential

V

OD

terminated by 50Ω to GND, AC-Coupled 550 620 725 mV

P-P

Voltage Level (OUT diff)

Figure 2

Single-ended measurement DC-Coupled with 50Ω

Output Common-Mode V

DD

-

V

OCM

terminations V

DD

-0.2 V

Voltage 0.1

(5)

20% to 80% of differential output voltage, measured

within 1” from output pins.

t

R

, t

F

Transition Time 20 60 ps

Figure 2

(5)

R

O

Output Resistance Single-ended to V

DD

42 50 58 Ω

Differential Output 100 MHz – 1.6 GHz, with fixture’s effect de-

R

LO

10 dB

Return Loss embedded. IN+ = static high.

Differential Low to High Propagation delay measurement at 50% V

OD

between

t

PLHD

240 ps

Propagation Delay input to output, 100 Mbps

Figure 3

(5)

Differential High to Low

t

PHLD

240 ps

Propagation Delay

EQUALIZATION

30” of 6 mil microstrip FR4, EQ Setting 0x06, PRBS-7

Residual Deterministic

DJ1 (2

7

-1) pattern 0.20 UI

P-P

Jitter at 10 Gbps

(6)(7)

40” of 6 mil microstrip FR4, EQ Setting 0x06, PRBS-7

Residual Deterministic

DJ2 (2

7

-1) pattern 0.17 0.26 UI

P-P

Jitter at 6.4 Gbps

(6)(7)

40” of 6 mil microstrip FR4, EQ Setting 0x07, PRBS-7

Residual Deterministic

DJ3 (2

7

-1) pattern 0.12 0.20 UI

P-P

Jitter at 5 Gbps

(6)(7)

40” of 6 mil microstrip FR4, EQ Setting 0x07, PRBS-7

Residual Deterministic

DJ4 (2

7

-1) pattern 0.10 0.16 UI

P-P

Jitter at 2.5 Gbps

(6)(7)

(4) Measured with clock-like {11111 00000} pattern.

(5) Measured with clock-like {11111 00000} pattern.

(6) Specification is guaranteed by characterization at optimal boost setting and is not tested in production.

(7) Deterministic jitter is measured at the differential outputs (point C of Figure 1), minus the deterministic jitter before the test channel (point

A of Figure 1). Random jitter is removed through the use of averaging or similar means.

4 Submit Documentation Feedback Copyright © 2006–2013, Texas Instruments Incorporated

Product Folder Links: DS64EV100

剩余15页未读,继续阅读

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0

最新资源