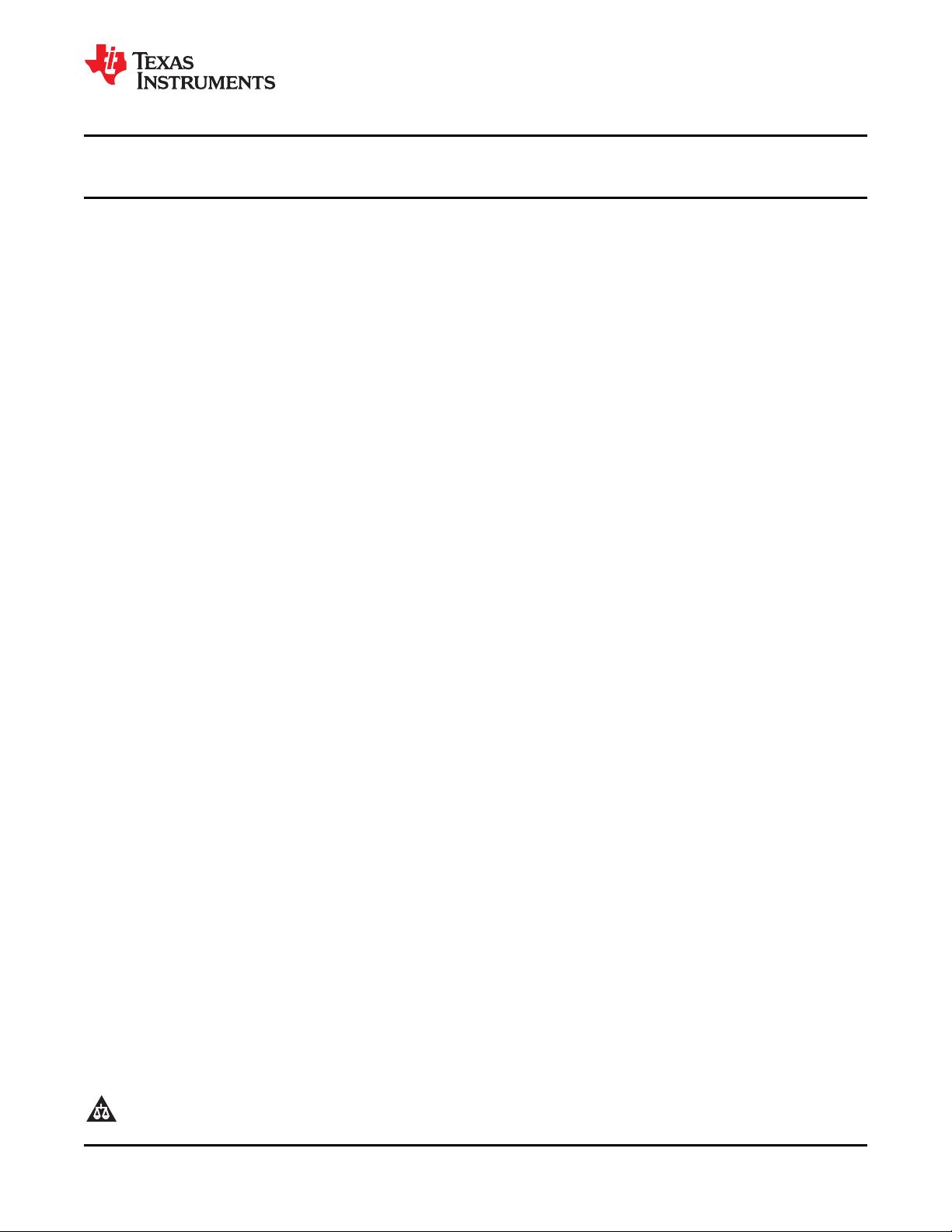

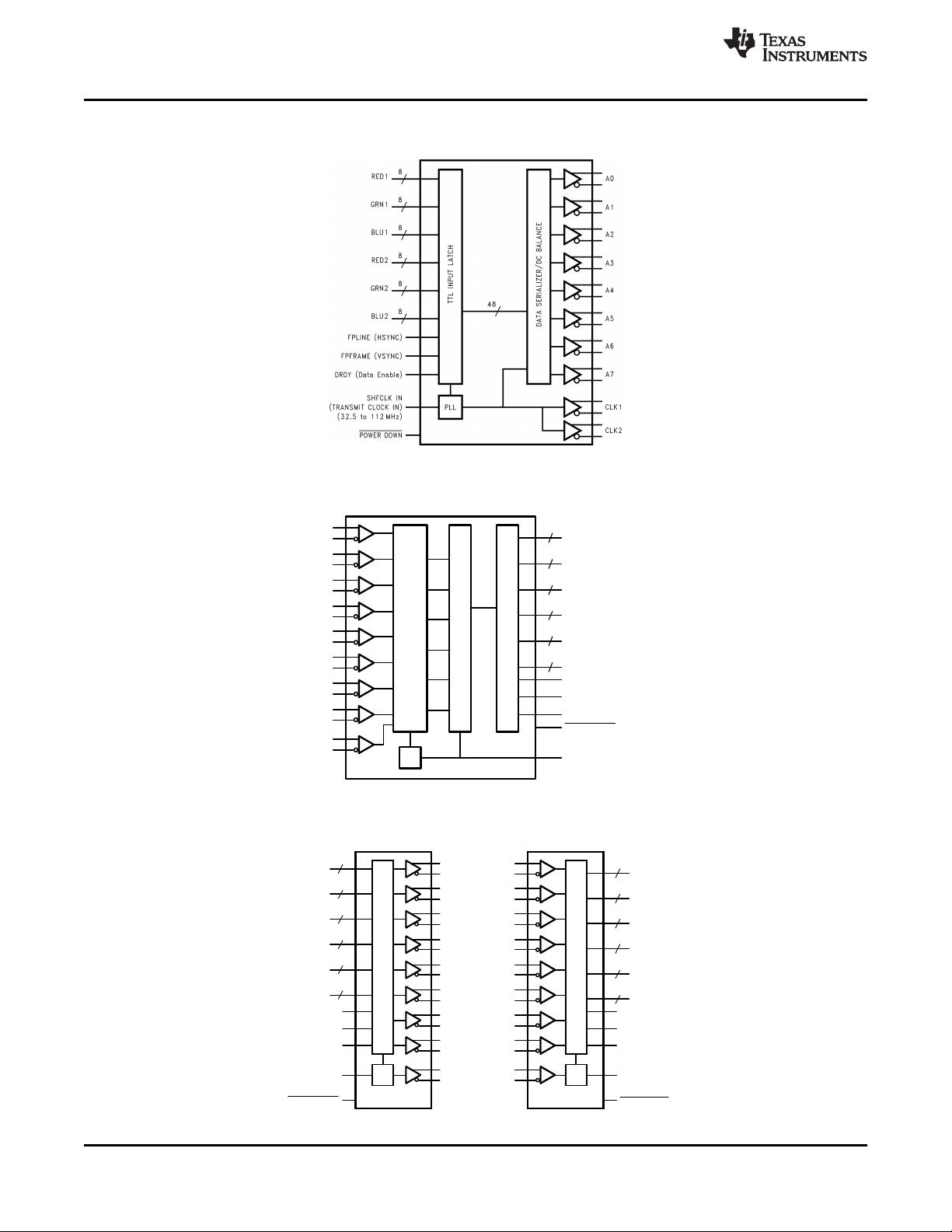

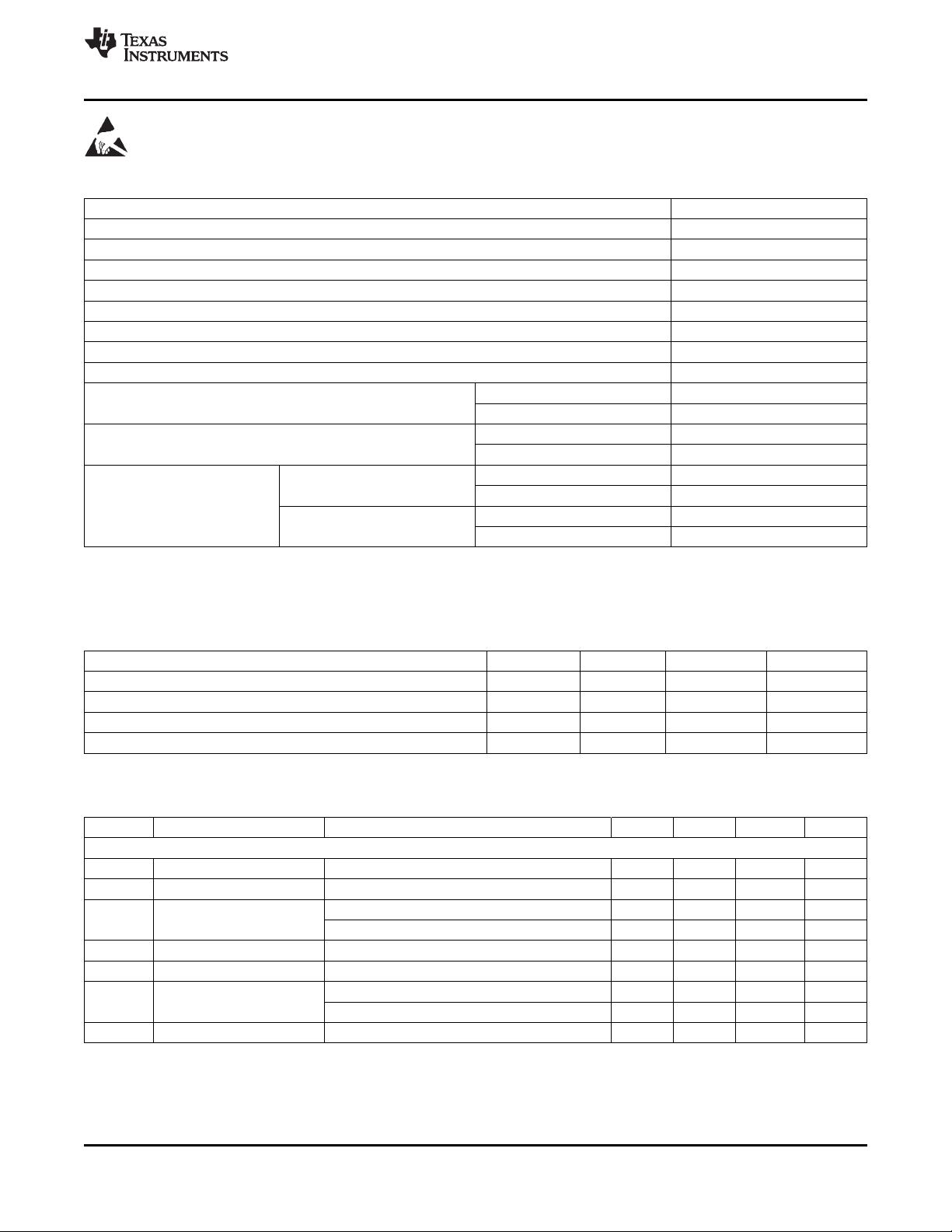

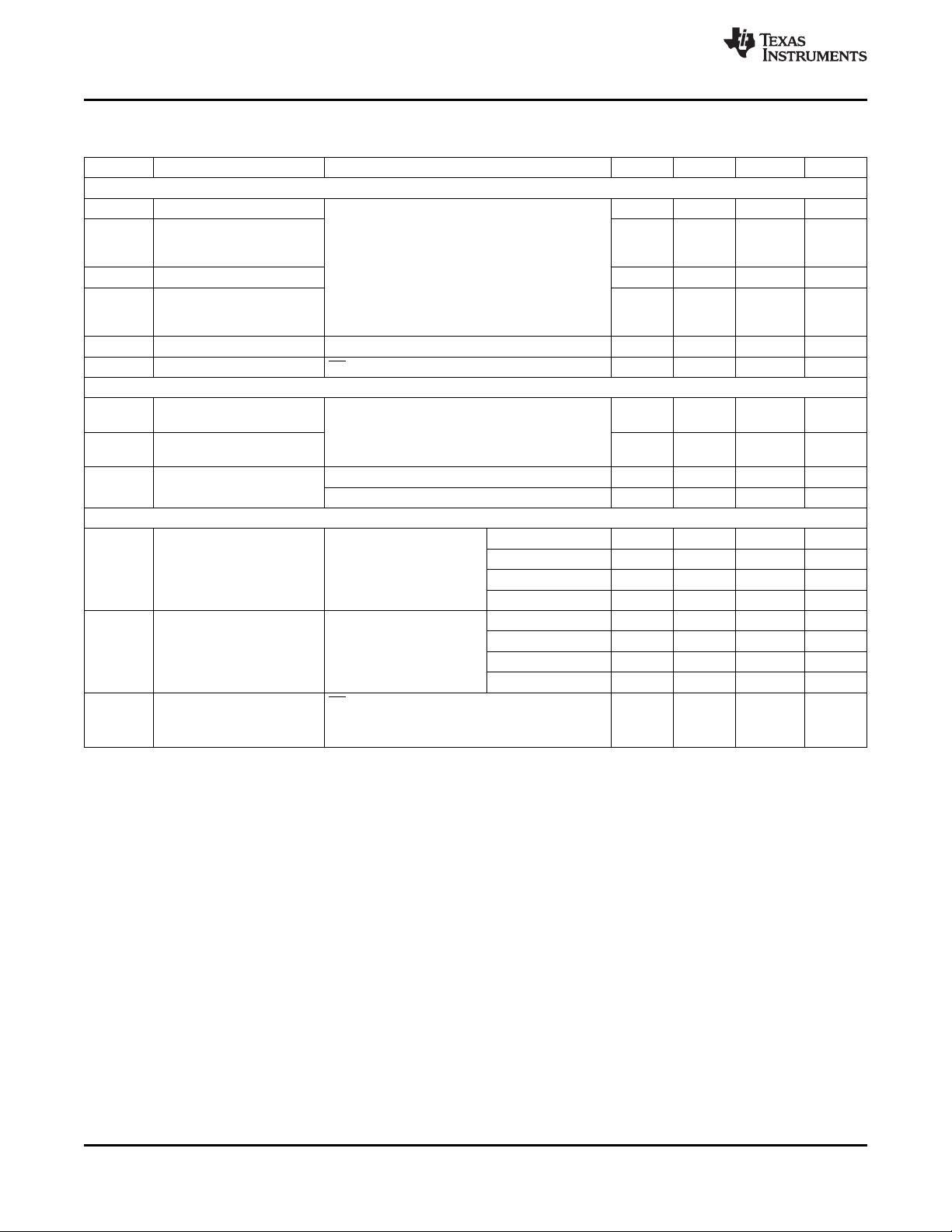

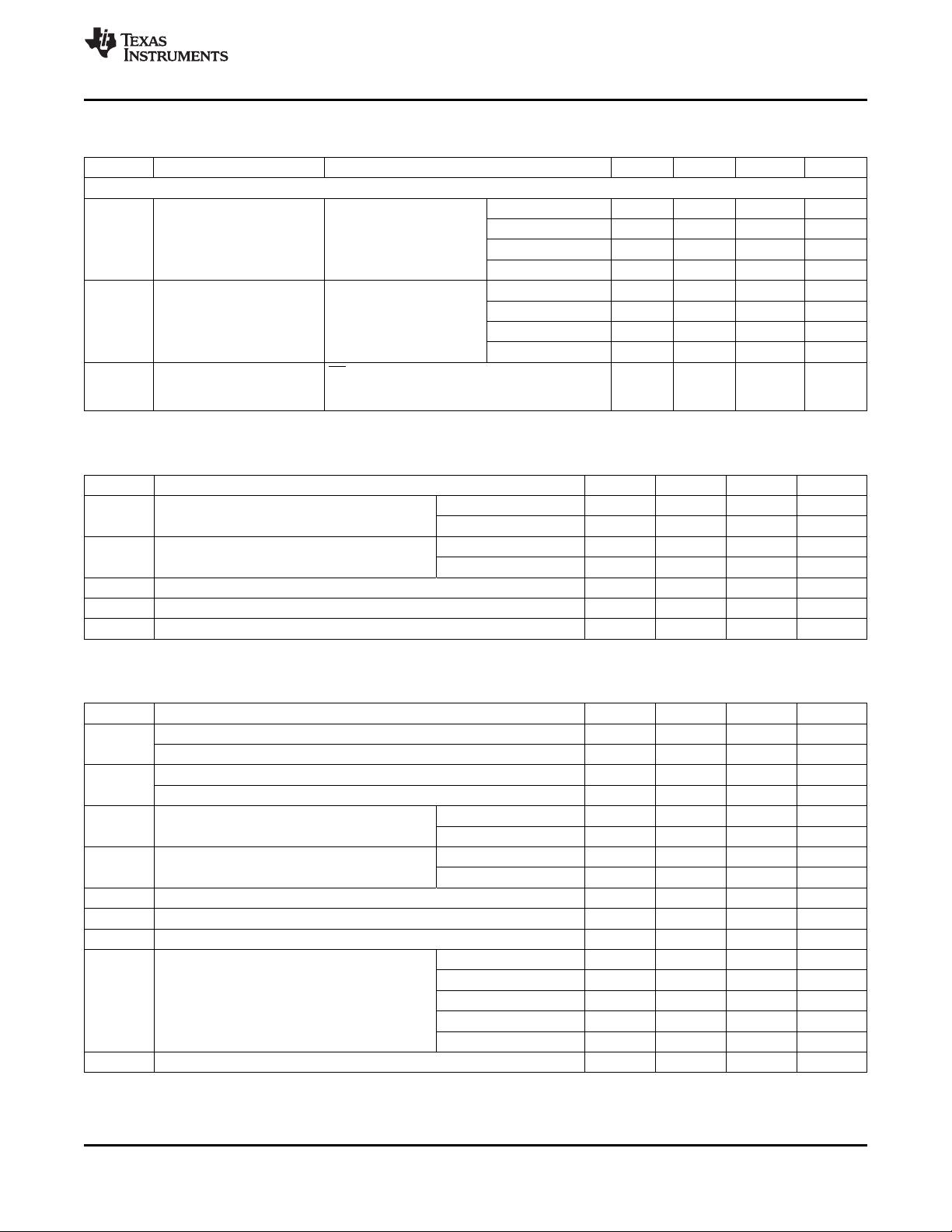

TI的DS90C387和DS90CF388是专为FPD-Link(Flat Panel Display Link)接口设计的双像素LVDS显示接口(LDI)发射器和接收器。这两个器件主要用于在主机和平板显示器之间传输双像素数据,最高支持QXGA分辨率,即2048x1536像素。以下是对这两个器件主要特性和功能的详细解释: 1. **兼容性与规格**:DS90C387和DS90CF388遵循OpenLDI(开放的数字显示接口)规范,适用于数字显示接口。它们可以支持从SVGA(800x600)到QXGA的各种面板分辨率。 2. **时钟支持**:DS90C387支持32.5到112MHz的时钟频率,而DS90CF388则支持40到112MHz的时钟频率。此外,DS90CF388还有一个模式,可以处理高达170MHz的单像素时钟输入。 3. **数据速率**:在最大112MHz的双像素率下,LVDS数据线速度达到672Mbps,总带宽可达5.38Gbps,即每秒672兆字节的数据传输量。 4. **信号控制**:除了48位(双像素24位色)CMOS/TTL数据转换为8个LVDS数据流外,DS90C387/DS90CF388还会在消隐期间发送控制信号,如垂直同步(VSYNC)、水平同步(HSYNC)、数据使能(DE)以及两个用户自定义信号。 5. **增强功能**: - **预加重**:减少电缆负载效应,提高信号质量。 - **直流平衡数据传输**:由发射器提供,减少因ISI( intersymbol interference,符号间干扰)引起的失真。 - **电缆时钟偏移校正**:允许+/−1 LVDS数据位时间(最高达80MHz时钟率)的对对时钟偏移校正,同时具有对内对 skew 的容忍度为300ps。 - **双像素架构**:支持与图形用户界面(GUI)和时序控制器的接口,可选单像素发射器输入支持单像素GUI接口。 6. **互操作性**:第三个模式提供了与FPD-Link设备的互操作性,确保了与不同系统的兼容性。 7. **性能提升**:相比前代FPD-Link设备,这些LDI芯片组在三个方面进行了增强,以提高带宽、支持更高的时钟频率和更长的电缆驱动距离: - **增加带宽**:最大像素时钟率提高至112(170)MHz。 - **电缆驱动能力**:通过提供8个串行LVDS输出来增强电缆驱动能力。 - **抗噪声能力**:发射器能够抵抗噪声干扰,确保数据传输的稳定性。 DS90C387和DS90CF388是高性能的FPD-Link解决方案,用于高分辨率视频传输,它们优化了数据传输效率,支持长距离低成本电缆,并具有强大的兼容性和互操作性。

剩余32页未读,继续阅读

- 粉丝: 6674

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Java源码jsp景区票务管理系统-毕业设计-期末大作业.zip

- Java源码jsp酒店管理系统-毕业设计-期末大作业.zip

- Java源码jsp教学设备报修系统-毕业设计-期末大作业.zip

- 通讯线速内编织切除机sw18可编辑全套技术资料100%好用.zip

- 减速器含设计文档实验用减速器的设计

- Java源码jsp酒店人员管理系统-毕业设计-期末大作业.zip

- Java源码jsp酒品销售系统-毕业设计-期末大作业.zip

- Java源码jsp咖啡馆管理系统-毕业设计-期末大作业.zip

- ActivityGroup + GridView + ViewFlipper 实现选项卡-仅用于Android项目学习

- MATLAB 图像分解与重构:以 woman 图像为例详解 dwt2、idwt2、wavedec2 和 waverec2 命令的应用.m

- 分布式电动汽车稳定性控制 carsim simulink联合仿真,控制车辆稳定性 上层采用lqr控制输出期望横摆力矩 下层才用二次规划输出制动力矩,并采用平均分配实现四轮力矩分配 输入到轮毂电机中

- 毕设-java-[搜索链接]Java网络爬虫(蜘蛛)源码_zhizhu28.zip

- 毕设-java-[新闻文章]NTsky新闻发布(提供JavaBean)v1.0_ntskynewsv1.0javabean29.zip

- 毕设-java-[搜索链接]java(结合lucene)版的公交搜索系统_javaso27.zip

- 毕设-java-[信息办公]学生课绩管理系统 jsp + servlet + javaBean + sql_server_scm32.zip

- 毕设-java-[信息办公]凯撒java版SaaS OA协同办公软件 v2.0_saas-oa31.zip

信息提交成功

信息提交成功