HD3SS213

ZHCSBL2A –SEPTEMBER 2013–REVISED SEPTEMBER 2013

www.ti.com.cn

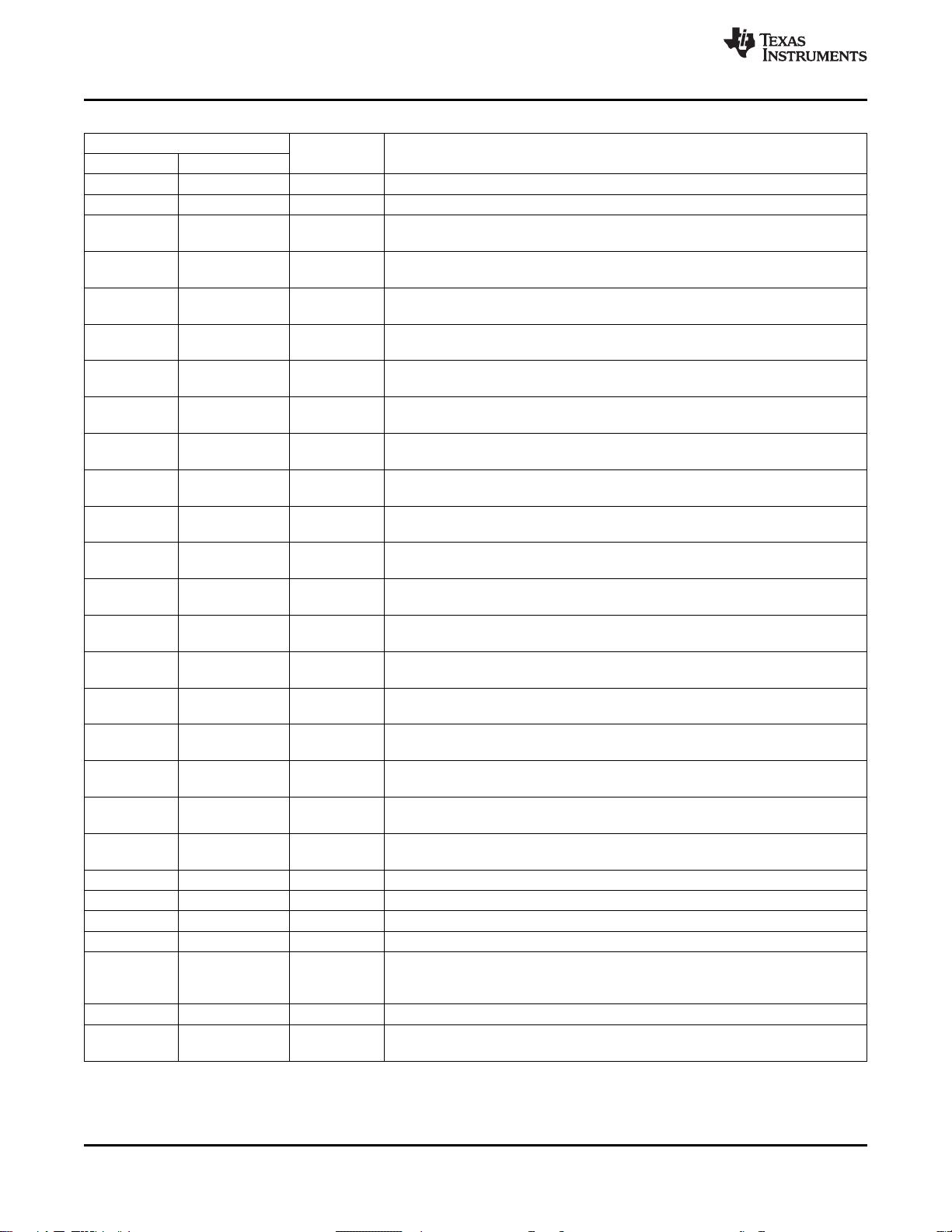

PIN DESCRIPTIONS

PIN

I/O DESCRIPTION

(1)

ZQE NAME

A1 Dx_SEL Control I High Speed Port Selection Control Pins

C2 AUX_SEL Control I AUX/DDC Selection Control Pin in Conjunction with Dx_SEL Pin

B4 DA0(p) Port A, Channel 0, High Speed Positive Signal

I/O

A4 DA0(n) Port A, Channel 0, High Speed Negative Signal

B5 DA1(p) Port A, Channel 1, High Speed Positive Signal

I/O

A5 DA1(n) Port A, Channel 1, High Speed Negative Signal

B6 DA2(p) Port A, Channel 2, High Speed Positive Signal

I/O

A6 DA2(n) Port A, Channel 2, High Speed Negative Signal

A8 DA3(p) Port A, Channel 3, High Speed Positive Signal

I/O

A9 DA3(n) Port A, Channel 3, High Speed Negative Signal

B8 DB0(p) Port B, Channel 0, High Speed Positive Signal

I/O

B9 DB0(n) Port B, Channel 0, High Speed Negative Signal

D8 DB1(p) Port B, Channel 1, High Speed Positive Signal

I/O

D9 DB1(n) Port B, Channel 1, High Speed Negative Signal

E8 DB2(p) Port B, Channel 2, High Speed Positive Signal

I/O

E9 DB2(n) Port B, Channel 2, High Speed Negative Signal

F8 DB3(p) Port B, Channel 3, High Speed Positive Signal

I/O

F9 DB3(n) Port B, Channel 3, High Speed Negative Signal

B2 DC0(p) Port C, Channel 0, High Speed Positive Signal

I/O

B1 DC0(n) Port C, Channel 0, High Speed Negative Signal

D2 DC1(p) Port C, Channel 1, High Speed Positive Signal

I/O

D1 DC1(n) Port C, Channel 1, High Speed Negative Signal

E2 DC2(p) Port C, Channel 2, High Speed Positive Signal

I/O

E1 DC2(n) Port C, Channel 2, High Speed Negative Signal

F2 DC3(p) Port C, Channel 3, High Speed Positive Signal

I/O

F1 DC3(n) Port C, Channel 3, High Speed Negative Signal

H9 AUXA(p) Port A AUX Positive Signal

I/O

J9 AUXA(n) Port A AUX Negative Signal

H6 AUXB(p) Port B AUX Positive Signal

I/O

J6 AUXB(n) Port B AUX Negative Signal

H2 AUXC(p) Port C AUX Positive Signal

I/O

H1 AUXC(n) Port C AUX Negative Signal

H8 DDCCLK_A Port A DDC Clock Signal

I/O

J8 DDCDAT_A Port A DDC Data Signal

H5 DDCCLK_B Port B DDC Clock Signal

I/O

J5 DDCDAT_B Port B DDC Data Signal

J3 DDCCLK_C Port C DDC Clock Signal

I/O

J7 DDCDAT_C Port C DDC Data Signal

J2 HPDA I/O Port A Hot Plug Detect

H3 HPDB I/O Port B Hot Plug Detect

J1 HPDC I/O Port C Hot Plug Detect

NA CADA/B/C I/O Port A/B/C Cable Activity Detect

Output Enable:

B7 OE I OE = V

IH

: Normal Operation

OE = V

IL

: Standby Mode

J4 VDD Supply 3.3V Positive power supply voltage

B3, C8, G2,

GND Supply Ground

G8 H4, H7

(1) The high speed data ports incorporate 20kΩ pull down resistors that are switched in when a port is not selected and switched out when

the port is selected.

4 Copyright © 2013, Texas Instruments Incorporated

评论0

最新资源