2

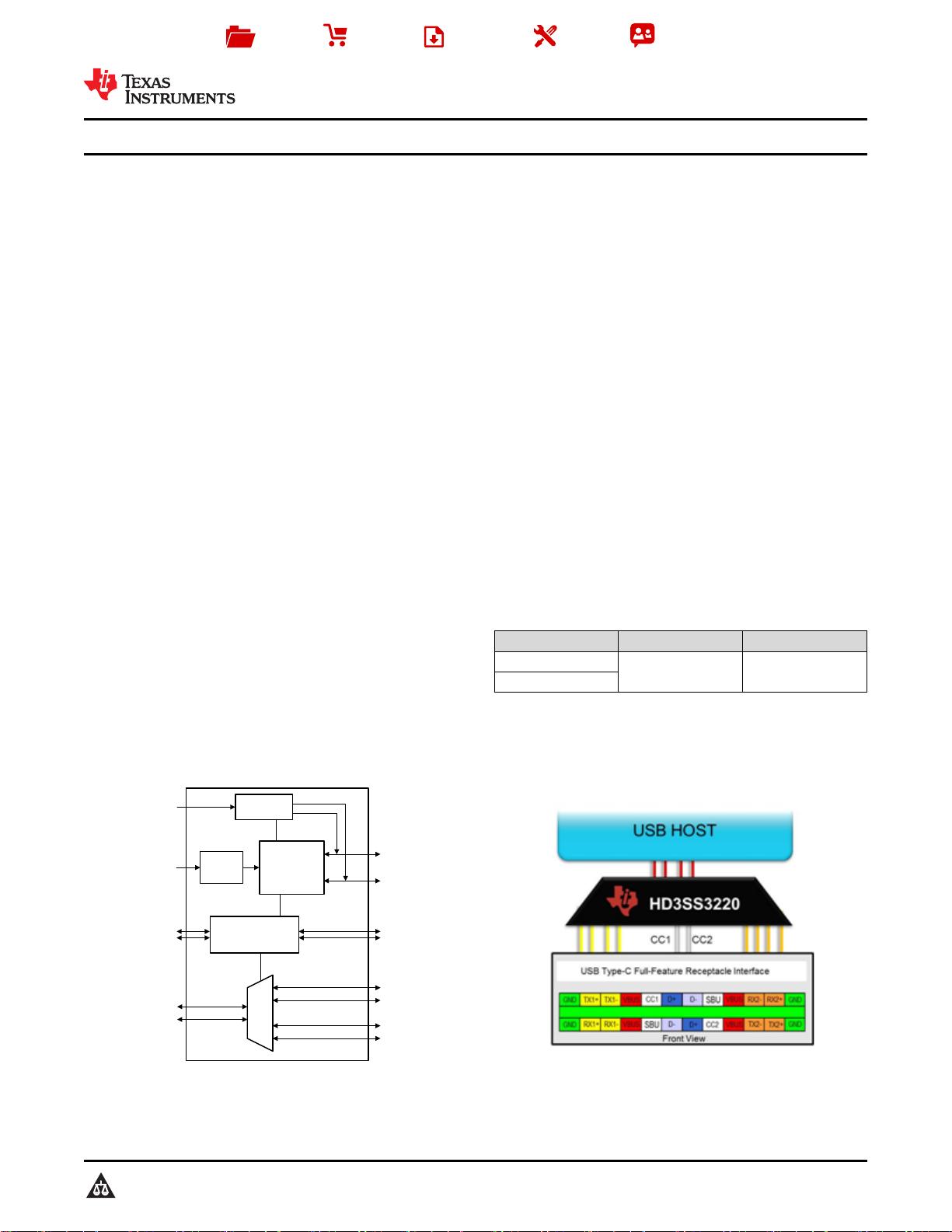

HD3SS3220

ZHCSFC4A –DECEMBER 2015–REVISED AUGUST 2016

www.ti.com.cn

Copyright © 2015–2016, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

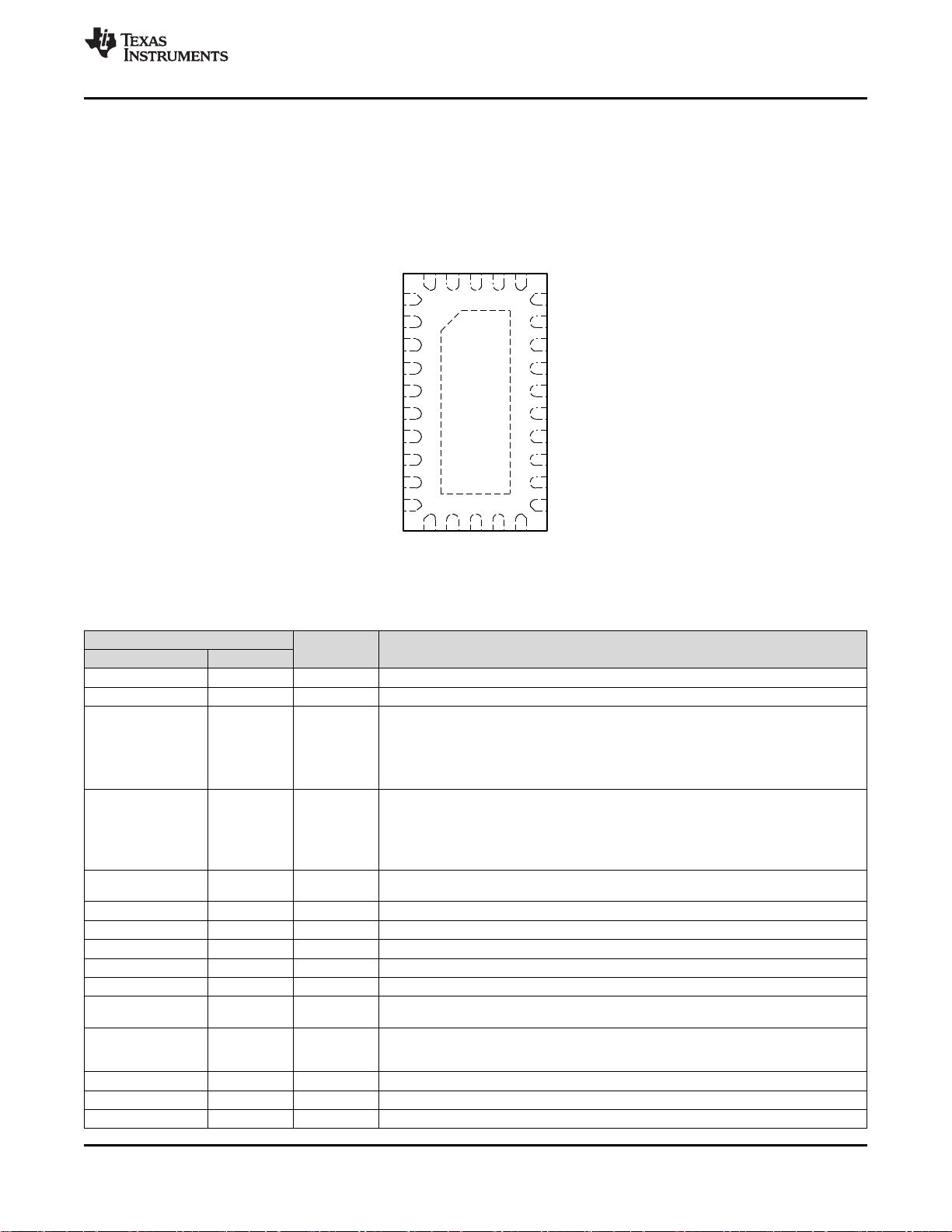

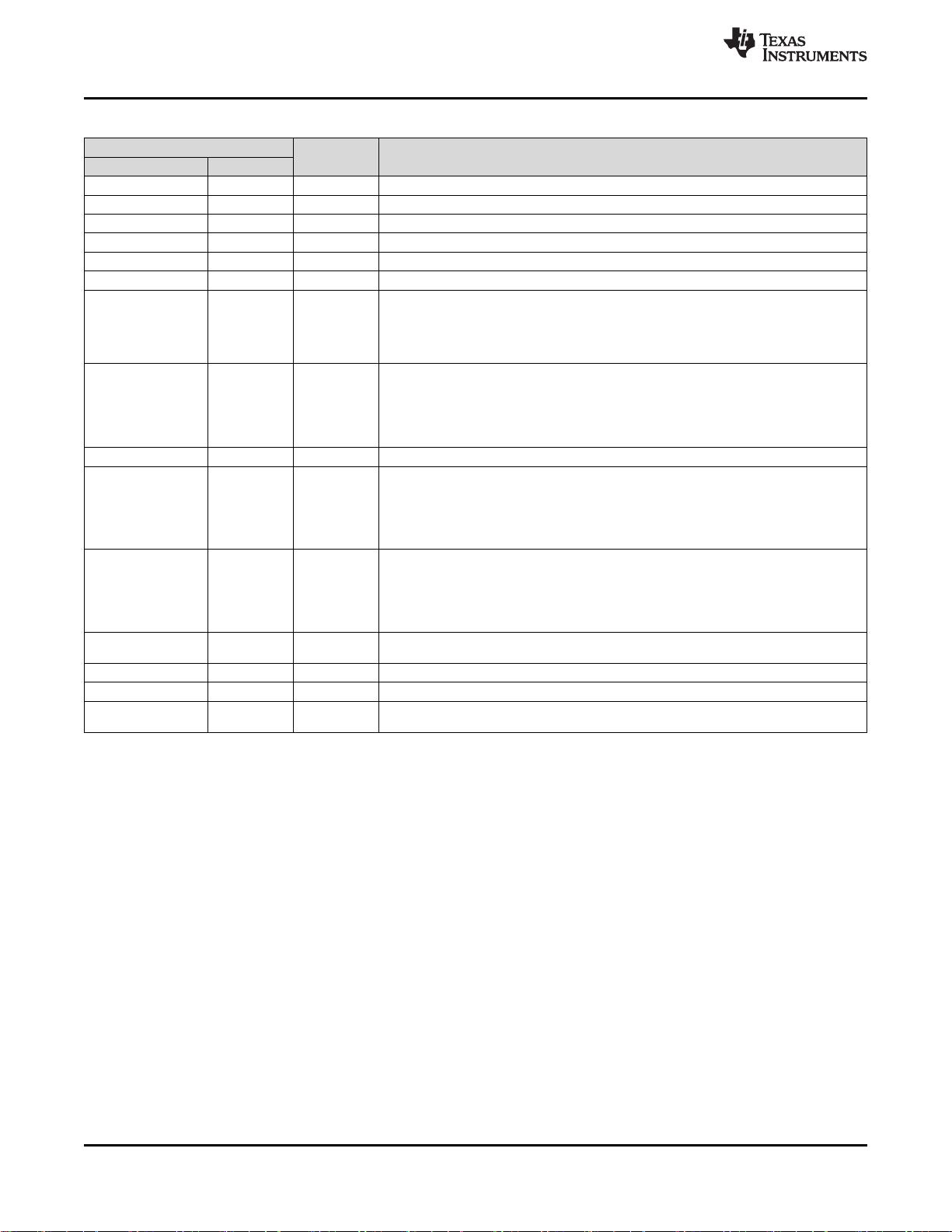

5 Pin Configuration and Functions......................... 3

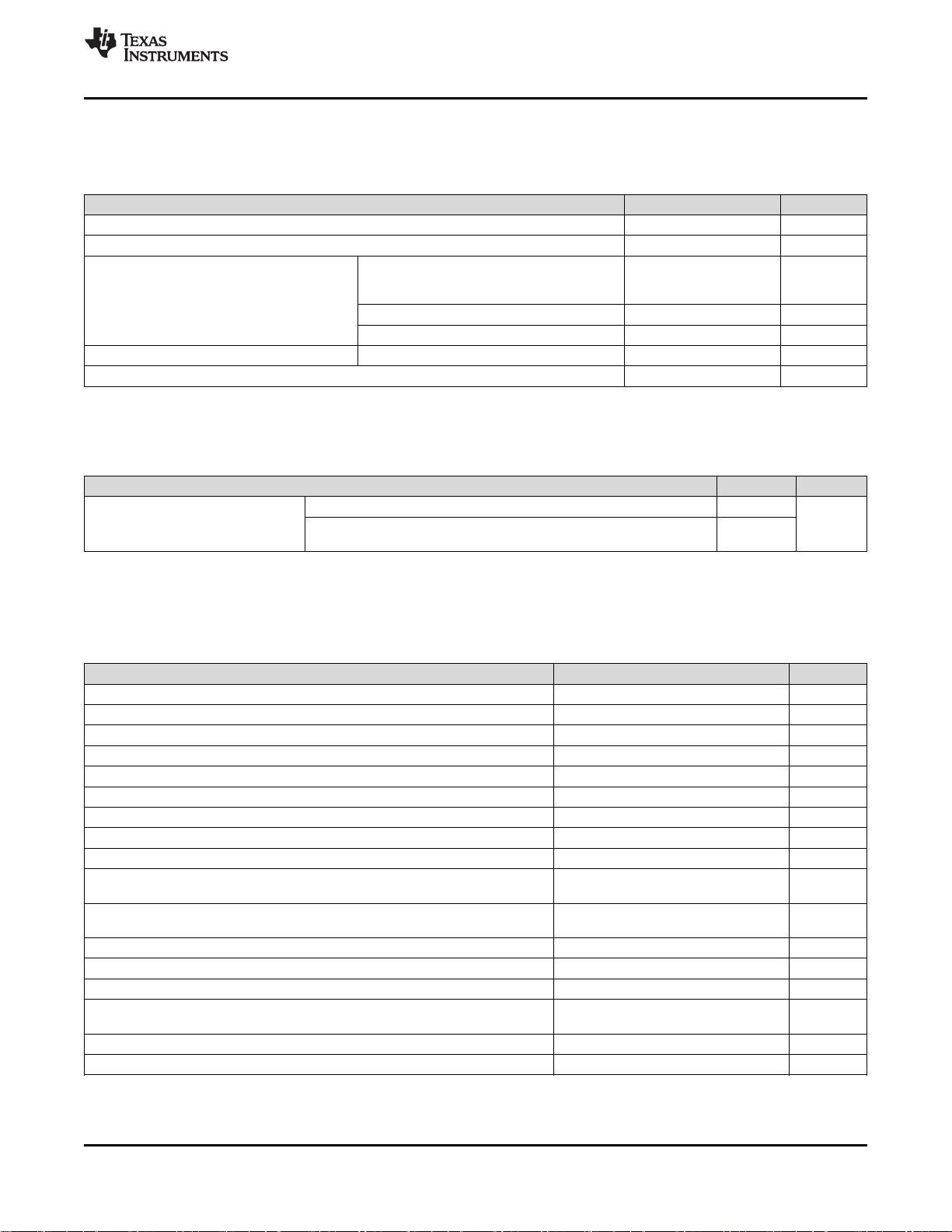

6 Specifications......................................................... 5

6.1 Absolute Maximum Ratings ...................................... 5

6.2 ESD Ratings.............................................................. 5

6.3 Recommended Operating Conditions....................... 5

6.4 Thermal Information.................................................. 6

6.5 Electrical Characteristics........................................... 6

6.6 Timing Requirements................................................ 8

7 Detailed Description............................................ 10

7.1 Overview ................................................................. 10

7.2 Functional Block Diagram ....................................... 12

7.3 Feature Description................................................. 13

7.4 Device Functional Modes........................................ 16

7.5 Programming........................................................... 18

7.6 Register Maps ........................................................ 19

8 Application and Implementation ........................ 23

8.1 Application Information............................................ 23

8.2 Typical Application, DRP Port ................................ 24

9 Power Supply Recommendations...................... 29

10 Layout................................................................... 30

10.1 Layout Guidelines ................................................. 30

10.2 Layout ................................................................... 36

11 器器件件和和文文档档支支持持 ..................................................... 37

11.1 接收文档更新通知 ................................................. 37

11.2 社区资源................................................................ 37

11.3 商标 ....................................................................... 37

11.4 静电放电警告......................................................... 37

11.5 Glossary................................................................ 37

12 机机械械、、封封装装和和可可订订购购信信息息....................................... 37

4 修修订订历历史史记记录录

Changes from Original (December 2016) to Revision A Page

• Absolute Maximum Ratings, Deleted "ENn_MUX" from the Control Pins.............................................................................. 5

• ESD Ratings, Deleted text "Pins listed as ± XXX V may actually have higher performance." from Note 1............................ 5

• Recommended Operating Conditions, Added "VDD5 supply ramp time" ............................................................................. 5

• Recommended Operating Conditions, Changed "External resistor on VBUS_DET pin" MIN value From: 890 KΩ To:

880 KΩ.................................................................................................................................................................................... 5

• Switch the position of CC1 and CC2 in Figure 10 ............................................................................................................... 24

• Switch the position of CC1 and CC2 in Figure 11 ............................................................................................................... 26

• Switch the position of CC1 and CC2 in Figure 12 ............................................................................................................... 28

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功