TMS55160, TMS55161, TMS55170, TMS55171

262144 BY 16-BIT MULTIPORT VIDEO RAMS

SMVS464 – MARCH1996

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

description

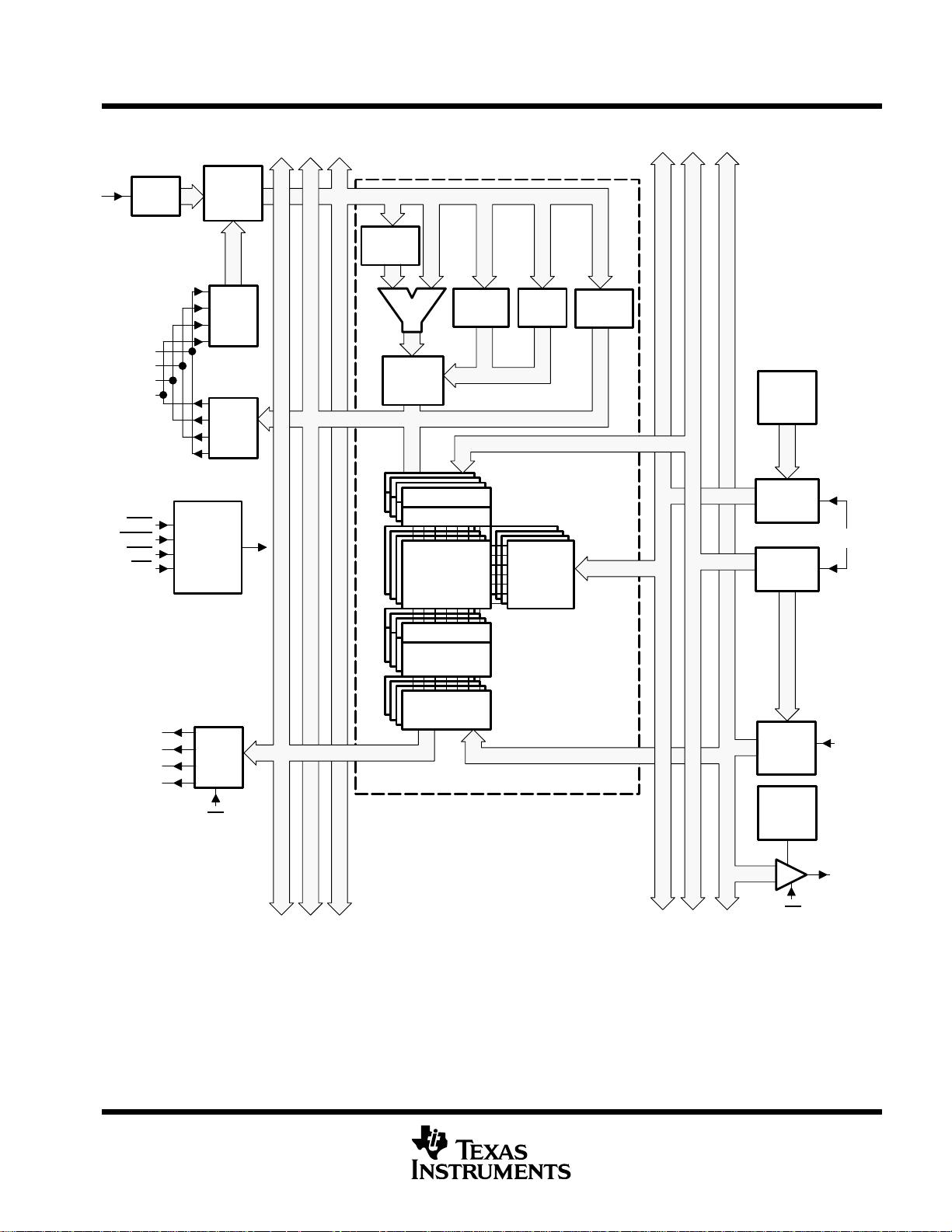

The TMS551xx multiport video RAMs (VRAMs) are high-speed dual-ported memory devices. Each consists of

a dynamic random-access memory (DRAM) organized as 262 144 words of 16 bits each interfaced to a

serial-data register [serial-access memory (SAM)] organized as 256 words of 16 bits each. These devices

support three basic types of operation: random access to and from the DRAM, serial access from the serial

register, and transfer of data from the DRAM to the SAM. Except during transfer operations, these devices can

be accessed simultaneously and asynchronously from the DRAM and SAM ports.

The TMS551xx multiport VRAMs provide several functions designed to provide higher system-level bandwidth

and to simplify design integration on both the DRAM and SAM ports (see Table 2). On the DRAM port, greater

pixel draw rates are achieved by the block-write function. The TMS5516x devices’ 4-column block-write function

allows 16 bits of data (present in an on-chip color-data register) to be written to any combination of four adjacent

column-address locations, up to a total of 64 bits of data per CASx

cycle time. Similarly, the TMS5517x devices’

8-column block-write function allows 16 bits of data to be written to any combination of eight adjacent

column-address locations, up to a total of 128 bits of data per CASx

cycle time. Also on the DRAM port, the

write-per-bit (or write-mask) function allows masking of any combination of the 16 DQs on any write cycle. The

persistent write-per-bit function uses a mask register that, once loaded, can be used on subsequent write cycles

without reloading. All TMS551xx devices offer byte control. Byte control can be applied in write cycles, read

cycles, block-write cycles, load-write-mask-register cycles, and load-color-register cycles. The TMS551xx

devices offer enhanced-page-mode operation that results in faster access time. The TMS551x1 devices also

offer extended-data-output (EDO) mode. The EDO mode is effective in both the page-mode and the standard

DRAM cycles.

The TMS551xx devices offer a split-register-transfer (DRAM to SAM) function. This feature enables real-time

register load implementation for continuous serial-data streams without critical timing requirements. The serial

register is divided into a high half and a low half. While one half is being read out of the SAM port, the other half

can be loaded from the DRAM. For applications not requiring real-time register load (for example, loads done

during CRT-retrace periods), the full-register-transfer operation is retained to simplify system design.

The SAM port is designed for maximum performance. Data can be accessed from the SAM at serial rates up

to 55 MHz. A separate output, QSF, is included to indicate which half of the serial register is active. Refreshing

the SAM is not required because the data register that comprises the SAM is static.

All inputs, outputs, and clock signals on the TMS551xx devices are compatible with Series 74 TTL. All address

lines and data-in lines are latched on-chip to simplify system design. All data-out lines are unlatched to allow

greater system flexibility.

All TMS551xx employ TI’s state-of-the-art EPIC technology combining very high performance with improved

reliability.

All TMS551xx are offered in a 64-pin small-outline gull-wing-leaded package (DGH suffix) for direct surface

mounting.

The TMS551xx VRAMs and other TI multiport VRAMs are supported by a broad line of graphics processors

and control devices from Texas Instruments.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功