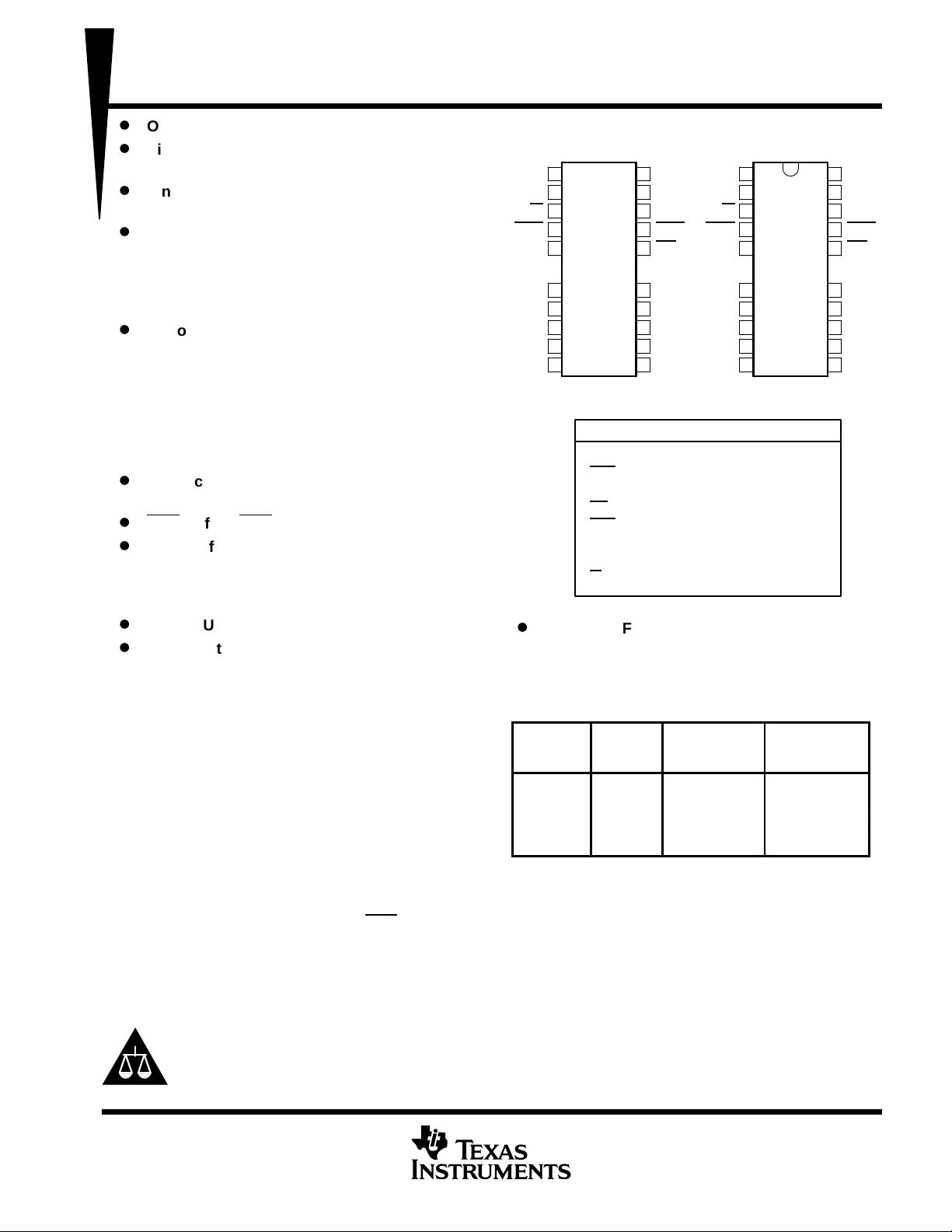

TMS44400, TMS44400P, TMS46400, TMS46400P

1048576-WORD BY 4-BIT

DYNAMIC RANDOM-ACCESS MEMORIES

SMHS562C – MAY 1995 – REVISED NOVEMBER 1996

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

operation

enhanced page mode

Enhanced-page-mode operation allows faster memory access by keeping the same row address while

selecting random column addresses. The time for row-address setup and hold and address multiplex is

eliminated. The maximum number of columns that can be accessed is determined by the maximum RAS

low

time and the CAS

page cycle time used. With minimum CAS page cycle time, all 1024 columns specified by

column addresses A0 through A9 can be accessed without intervening RAS

cycles.

Unlike conventional page-mode DRAMs, the column-address buffers in this device are activated on the falling

edge of RAS

. The buffers act as transparent or flow-through latches while CAS is high. The falling edge of CAS

latches the column addresses. This feature allows the TMS4x400 to operate at a higher data bandwidth than

conventional page-mode parts because data retrieval begins as soon as the column address is valid rather than

when CAS

transitions low. This performance improvement is referred to as enhanced page mode. A valid

column address can be presented immediately after row-address hold time has been satisfied, usually well in

advance of the falling edge of CAS

. In this case, data is obtained after t

CAC

maximum (access time from CAS

low) if t

AA

maximum (access time from column address) has been satisfied. In the event that column addresses

for the next cycle are valid at the time CAS

goes high, access time for the next cycle is determined by the later

occurrence of t

CAC

(acces time from CAS low) or t

CPA

(access time from column precharge).

address (A0–A9)

Twenty address bits are required to decode any one of the 1048576 storage-cell locations. Ten row-address

bits are set up on inputs A0 through A9 and latched onto the chip by RAS

. The ten column-address bits are set

up on A0 through A9 and latched onto the chip by CAS

. All addresses must be stable on or before the falling

edges of RAS

and CAS. RAS is similar to a chip enable because it activates the sense amplifiers as well as the

row decoder. CAS

is used as a chip select, activating the output buffer, as well as latching the address bits into

the column-address buffer.

write enable (W

)

The read or write mode is selected through W

input. A logic high on W selects the read mode and a logic low

selects the write mode. W

can be driven from standard TTL circuits (TMS44400/P) or low voltage TTL circuits

(TMS46400/P) without a pullup resistor. The data input is disabled when the read mode is selected. When W

goes low prior to CAS (early write), data out remains in the high-impedance state for the entire cycle, permitting

a write operation independent of the state of OE

. This permits early-write operation to complete with OE

grounded.

data in/out (DQ1–DQ4)

Data out is the same polarity as data in. The output is in the high-impedance (floating) state until CAS

and OE

are brought low. In a read cycle, the output becomes valid after all access times are satisfied. The output remains

valid while CAS

and OE are low. CAS or OE going high returns the output to a high-impedance state. This is

accomplished by bringing OE

high prior to applying data, satisfying the OE to data delay hold time (t

OED

).

output enable (OE

)

OE

controls the impedance of the output buffers. When OE is high, the buffers remain in the high-impedance

state. Bringing OE

low during a normal cycle activates the output buffers, putting them in the low-impedance

state. It is necessary for both RAS

and CAS to be brought low for the output buffers to go into the low-impedance

state. They remain in the low-impedance state until either OE

or CAS is brought high.

ADVANCE INFORMATION

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功