TMS4C2972

245760 BY 12-BIT

FIELD MEMORY

SMGS671 – OCTOBER 1997

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

D

2949120 Bits of Memory

D

Organization: 245760 Words × 12 Bits

D

Single 5-V Power Supply (± 10% Tolerance)

D

Upwardly and Pin-to-Pin Compatible With

TMS4C2970 and TMS4C2971

D

2-Port Memory With FIFO Operation

– Full-Word Continuous Read/Write

– Asynchronous Read/Write

D

Optional Random-Block Access Function

(40 Words per Block) Enabled During Reset

Operation, Two Modes for Write Access:

D0- or IE-Controlled

D

Fully Static (Refresh-Free and Infinite

Length of Clocking Pauses)

D

Write-Mask Function by Input Enable (IE)

D

Cascade Connection Capability

D

High-Speed Read/Write Operation

ACCESS CYCLE TIME

TIME READ WRITE

(MAX) (MIN) (MIN)

TMS4C2972-24 19 ns 24 ns 24 ns

TMS4C2972-26 21 ns 26 ns 26 ns

TMS4C2972-28 23 ns 28 ns 28 ns

D

16M-Bit CMOS DRAM Process

Technology

D

High-Reliability Plastic 36-Lead

Surface-Mount Shrink Small-Outline

Package (SSOP) (DT Suffix)

description

The TMS4C2972 is a field memory (FMEM) that is upwardly and pin-to-pin compatible with the TMS4C2970

and TMS4C2971, except for the consequences of the block size change (40 instead of 80 words per block) on

old data access mode enabling (see the section titled ‘‘old-/new-data access”).

The device is a two-port memory; data is written in through a 12-bit-wide write port and is read out through a

12-bit-wide read port. Both ports may be operated simultaneously and/or asynchronously. Dynamic storage

cells are employed for main data memory to achieve high storage density, but the TMS4C2972 refreshes its

cells automatically so that device operation appears fully static to the user. All internal pointers and registers

are fully static so that read and write operations can be interrupted for indefinite periods of time without loss of

data.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

IE Input Enable

WE Write Enable

SWCK Serial-Write Clock

RSTW Reset Write

D0– D11 Data Inputs

OE Output Enable

RE Read Enable

SRCK Serial-Read Clock

RSTR Reset Read

Q0– Q11 Data Outputs

V

DD1

– V

DD2

Power

V

SS1

–V

SS2

Ground

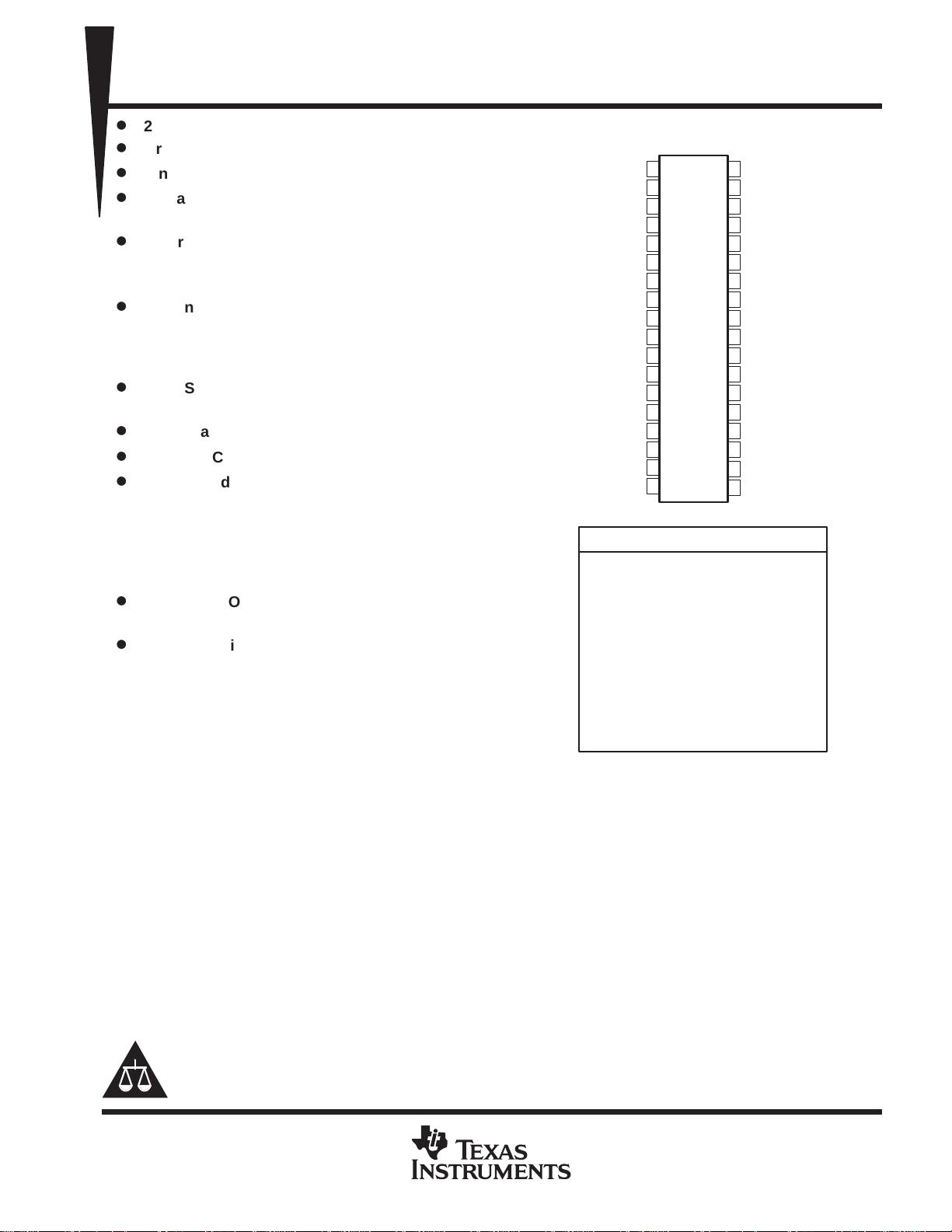

PIN NOMENCLATURE

DT PACKAGE

(TOP VIEW)

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

V

SS2

Q11

Q10

Q9

Q8

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

SRCK

RSTR

RE

OE

V

DD2

V

SS1

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

SWCK

RSTW

WE

IE

V

DD1

Copyright 1997, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功