Table of Contents

1 特性................................................................................... 1

2 应用................................................................................... 1

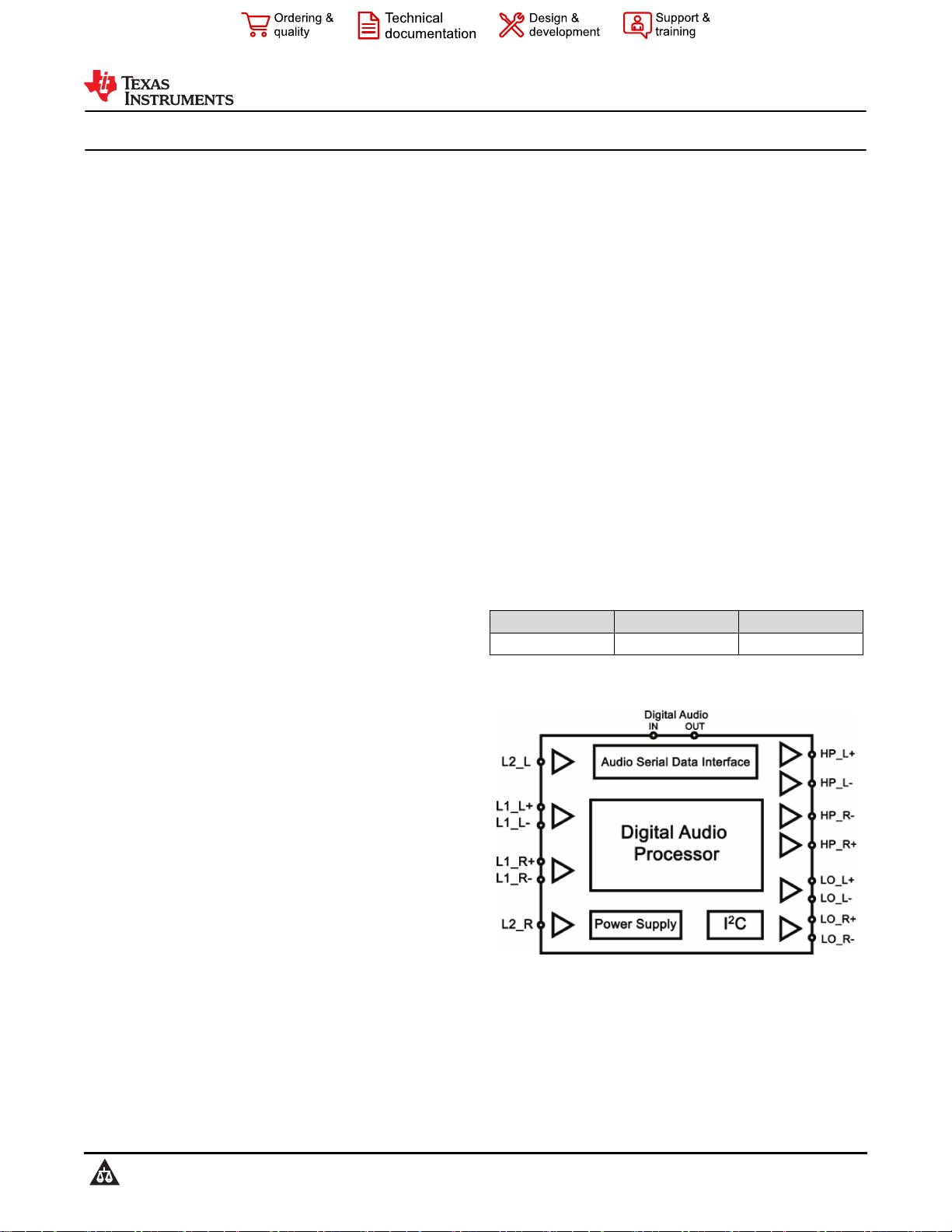

3 说明................................................................................... 1

4 Revision History.............................................................. 2

5 Description (Continued)..................................................4

6 Device Comparison Table............................................... 4

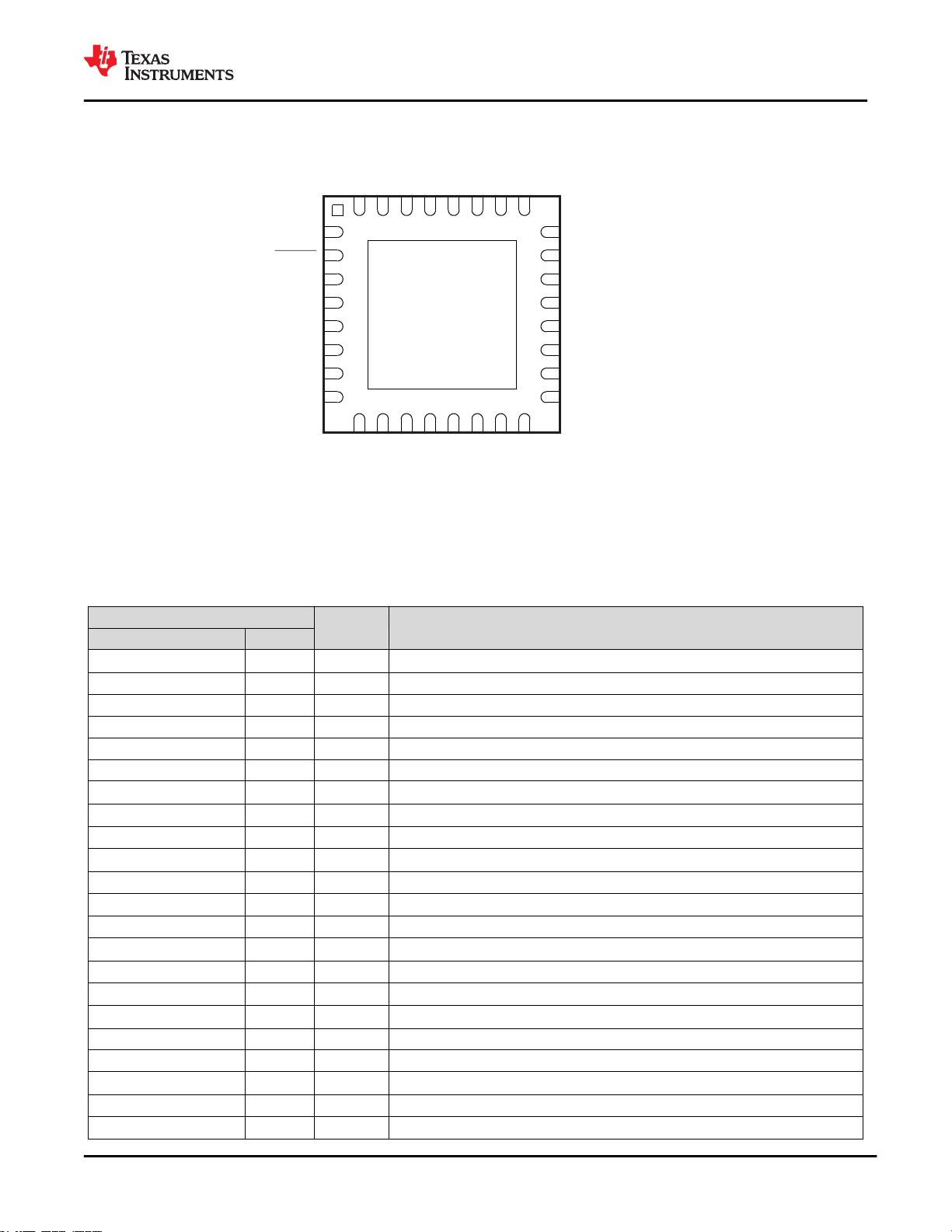

7 Pin Configuration and Functions...................................5

8 Specifications.................................................................. 7

8.1 Absolute Maximum Ratings........................................ 7

8.2 ESD Ratings............................................................... 7

8.3 Recommended Operating Conditions.........................7

8.4 Thermal Information....................................................8

8.5 Electrical Characteristics.............................................8

8.6 Audio Data Serial Interface Timing Requirements....13

8.7 Timing Diagrams.......................................................14

8.8 Typical Characteristics.............................................. 17

9 Parameter Measurement Information.......................... 19

10 Detailed Description....................................................19

10.1 Overview................................................................. 19

10.2 Functional Block Diagrams..................................... 20

10.3 Feature Description.................................................22

10.4 Device Functional Modes........................................43

10.5 Programming.......................................................... 45

10.6 Register Maps.........................................................48

11 Application and Implementation................................ 89

11.1 Application Information............................................89

11.2 Typical Applications.................................................89

12 Power Supply Recommendations..............................92

13 Layout...........................................................................93

13.1 Layout Guidelines................................................... 93

13.2 Layout Example...................................................... 94

14 Device and Documentation Support..........................95

14.1 接收文档更新通知................................................... 95

14.2 支持资源..................................................................95

14.3 Trademarks.............................................................95

14.4 静电放电警告.......................................................... 95

14.5 术语表..................................................................... 95

4 Revision History

Changes from Revision F (December 2016) to Revision G (February 2021) Page

•

更新了整个文档的表、图和交叉参考的编号格式

............................................................................................... 1

• 通篇将 QFN 更改为 VQFN..................................................................................................................................1

• 更改了

应用

部分..................................................................................................................................................1

• Changed Device Comparison Table: changed title, added TLV320AIC3109-Q1 row.........................................4

• Deleted System Thermal Characteristics table...................................................................................................8

• Added input impedance parameter in Electrical Characteristics table: added single-ended to test conditions of

first two rows, added last two rows to parameter................................................................................................8

• Deleted current consumption parameter, Stereo line in to stereo line out , no signal test condition.................. 8

• Changed list of intended applications in Overview section...............................................................................19

• Added Functional Block Diagram With Registers figure and added caption to Functional Block Diagram figure

..........................................................................................................................................................................20

• Added note to Audio Clock Generation section................................................................................................ 26

• Changed 2 MHz to 512 kHz in 512 kHz

≤

(PLLCLK_IN/P)

≤

20 MHz PLL example in Audio Clock

Generation section............................................................................................................................................26

• Added Left Channel Signal Path and Right Channel Signal Path figures to Audio Analog Inputs section....... 35

• Deleted Analog Input Bypass Path Functionality section................................................................................. 43

• Changed Passive Analog Bypass Mode Configuration figure to remove LINE 2L/R input bypass ................. 43

• Added reset value to D0 row in Page 0, Register 9: Audio Serial Data Interface Control Register B table......48

• Changed D3–D0 row reset value from 000 to 0000 in Page 0, Register 37: DAC Power and Output Driver

Control Register table....................................................................................................................................... 48

• Changed reset value from 1 to 0 and changed description of bit D1 in Page 0, Register 51: HPLOUT Output

Level Control Register ..................................................................................................................................... 65

• Changed reset value from 1 to 0 and changed description of bit D1 in Page 0, Register 58: HPLCOM Output

Level Control Register ..................................................................................................................................... 65

• Changed reset value from 1 to 0 and changed description of bit D1 in Page 0, Register 65: HPROUT Output

Level Control Register ..................................................................................................................................... 65

• Changed reset value from 1 to 0 and changed description of bit D1 in Page 0, Register 72: HPRCOM Output

Level Control Register ..................................................................................................................................... 65

TLV320AIC3104

ZHCSNE2G – MARCH 2007 – REVISED FEBRUARY 2021

www.ti.com.cn

2

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TLV320AIC3104

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功