没有合适的资源?快使用搜索试试~ 我知道了~

TI-TMP141.pdf

需积分: 5 0 下载量 80 浏览量

2023-04-22

16:10:58

上传

评论

收藏 1.02MB PDF 举报

温馨提示

试读

25页

TI-TMP141.pdf

资源推荐

资源详情

资源评论

FEATURES

D SensorPath INTERFACE

D FOUR ADDRESSES

D RESOLUTION: +0.25°C (10-bit)

D WIDE TEMPERATURE RANGE:

−40°C to +125°C

D LOW QUIESCENT CURRENT: 110µA (typ)

D TEMPERATURE ACCURACY: ±2°C (max)

D EXTENDED SUPPLY RANGE: +2.7V to +5.5V

D MICRO-SIZE PACKAGES:

SOT23-6 or MSOP-8

APPLICATIONS

D MOTHERBOARDS

D VIDEO CARDS

D BASE STATIONS

D ROUTERS

DESCRIPTION

The TMP141 is a digital output temperature sensor that

utilizes the single-wire SensorPath interface. The TMP141

is capable of measuring temperatures within 2°C of

accuracy over a temperature range of −25°C to +85°C and

3°C of accuracy over −40°C to +125°C. Low supply

current, and a supply range from 2.7V to 5.5V, make the

TMP141 an excellent candidate for a wide range of

low-power applications. The TMP141 is available in

SOT23-6 and MSOP-8 packages.

The TMP141 provides a simple, low-cost way to do

temperature measurement/monitoring and is ideal as a

part of an overall hardware health monitoring system. Up

to four TMP141s can be attached to a SensorPath bus. A

master configures the TMP141s and reads the

temperature output from all devices. No external sensing

components are needed for the TMP141 to measure and

report temperature.

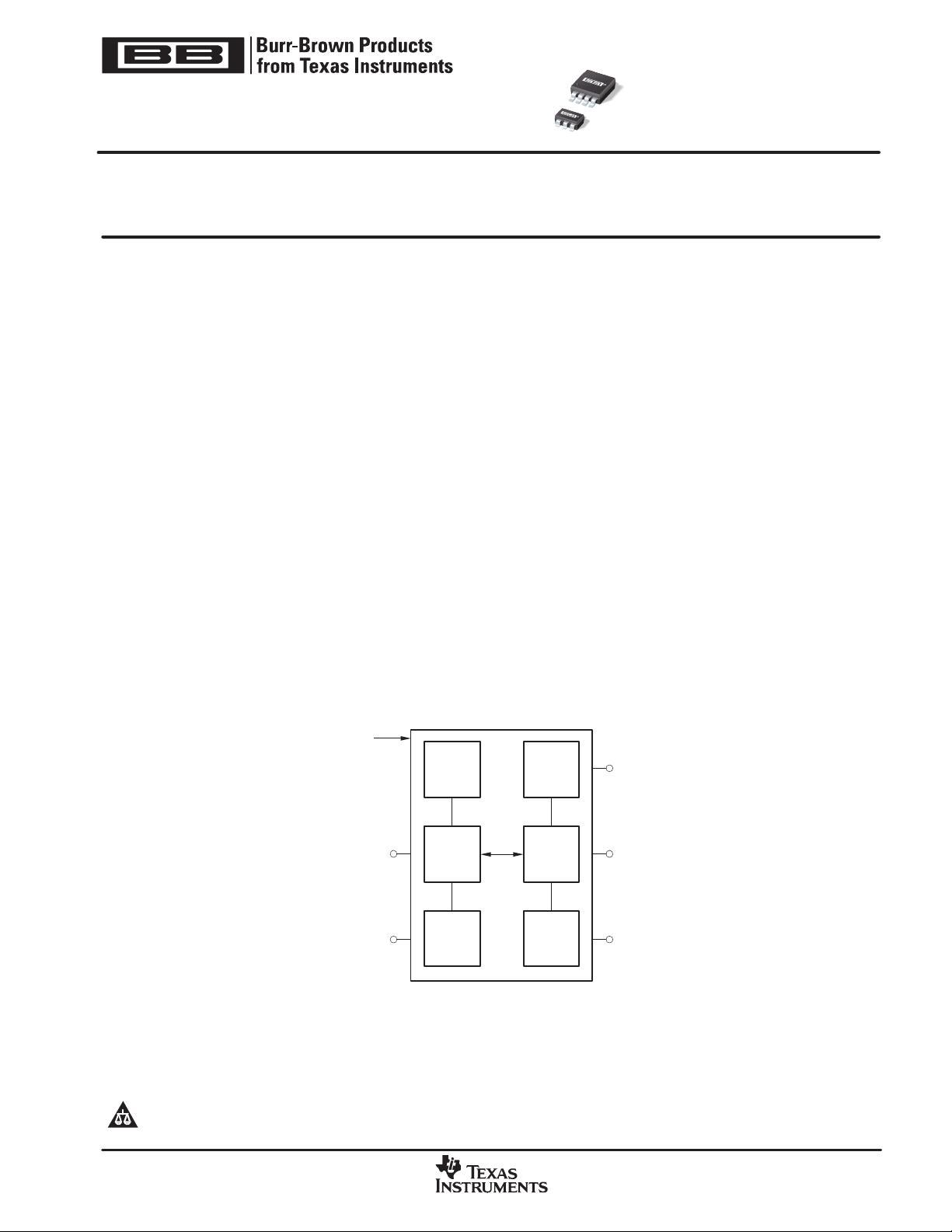

Diode

Te m p .

Sensor

∆Σ

A/D

Converter

OSC

Control

Logic

Serial

Interface

Config.

and Temp.

Register

TMP141

Temperature

V+

GND

ADD0

ADD1

SWD

TMP141

SBAS347A − MARCH 2005 − REVISED JULY 2006

Digital Out Temperature Sensor with

Single-Wire SensorPath Bus

! !

www.ti.com

Copyright 2005−2006, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments

semiconductor products and disclaimers thereto appears at the end of this data sheet.

SensorPath is a trademark of National Semiconductor. All other trademarks are the property of their respective owners.

"#$#

SBAS347A − MARCH 2005 − REVISED JULY 2006

www.ti.com

2

ABSOLUTE MAXIMUM RATINGS

(1)

Supply Voltage +7V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Input Terminals, Voltage

(2)

(V−) −0.5V to (V+) + 0.5V. . . .

Signal Input Terminals, Current

(2)

10mA. . . . . . . . . . . . . . . . . . . . .

Maximum Output Current (SWD low) 10mA. . . . . . . . . . . . . . . . . . .

Operating Temperature −55°C to +127°C. . . . . . . . . . . . . . . . . . . . .

Storage Temperature −60°C to +150°C. . . . . . . . . . . . . . . . . . . . . . .

Junction Temperature +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ESD Rating:

Human Body Model (HBM) 4000V. . . . . . . . . . . . . . . . . . . . . . .

Charged-Device Model 1000V. . . . . . . . . . . . . . . . . . . . . . . . . .

(1)

Stresses above these ratings may cause permanent damage.

Exposure to absolute maximum conditions for extended periods

may degrade device reliability. These are stress ratings only, and

functional operation of the device at these or any other conditions

beyond those specified is not supported.

(2)

Input terminals should not be driven beyond the power-supply

rails. Input signals that can swing more than 0.5V beyond the

supply rails should be current-limited to 10mA or less.

This integrated circuit can be damaged by ESD. Texas

Instruments recommends that all integrated circuits be

handled with appropriate precautions. Failure to observe

proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to

complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could

cause the device not to meet its published specifications.

ORDERING INFORMATION

(1)

PRODUCT PACKAGE-LEAD

PACKAGE

DESIGNATOR

SPECIFIED

TEMPERATURE

RANGE

PACKAGE

MARKING

ORDERING

NUMBER

TRANSPORT

MEDIA, QUANTITY

TMP141

SOT23-6

DBV

−40°C to +125°C

T141

TMP141AIDBVT Tape and Reel, 250

TMP141

SOT23-6

DBV

−40

°

C to +125

°

C

T141

TMP141AIDBVR Tape and Reel, 3000

TMP141

MSOP-8

DGK

−40°C to +125°C

T14G

TMP141AIDGKT Tape and Reel, 250

TMP141

MSOP-8

DGK

−40

°

C to +125

°

C

T14G

TMP141AIDGKR Tape and Reel, 3000

(1)

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site

at www.ti.com.

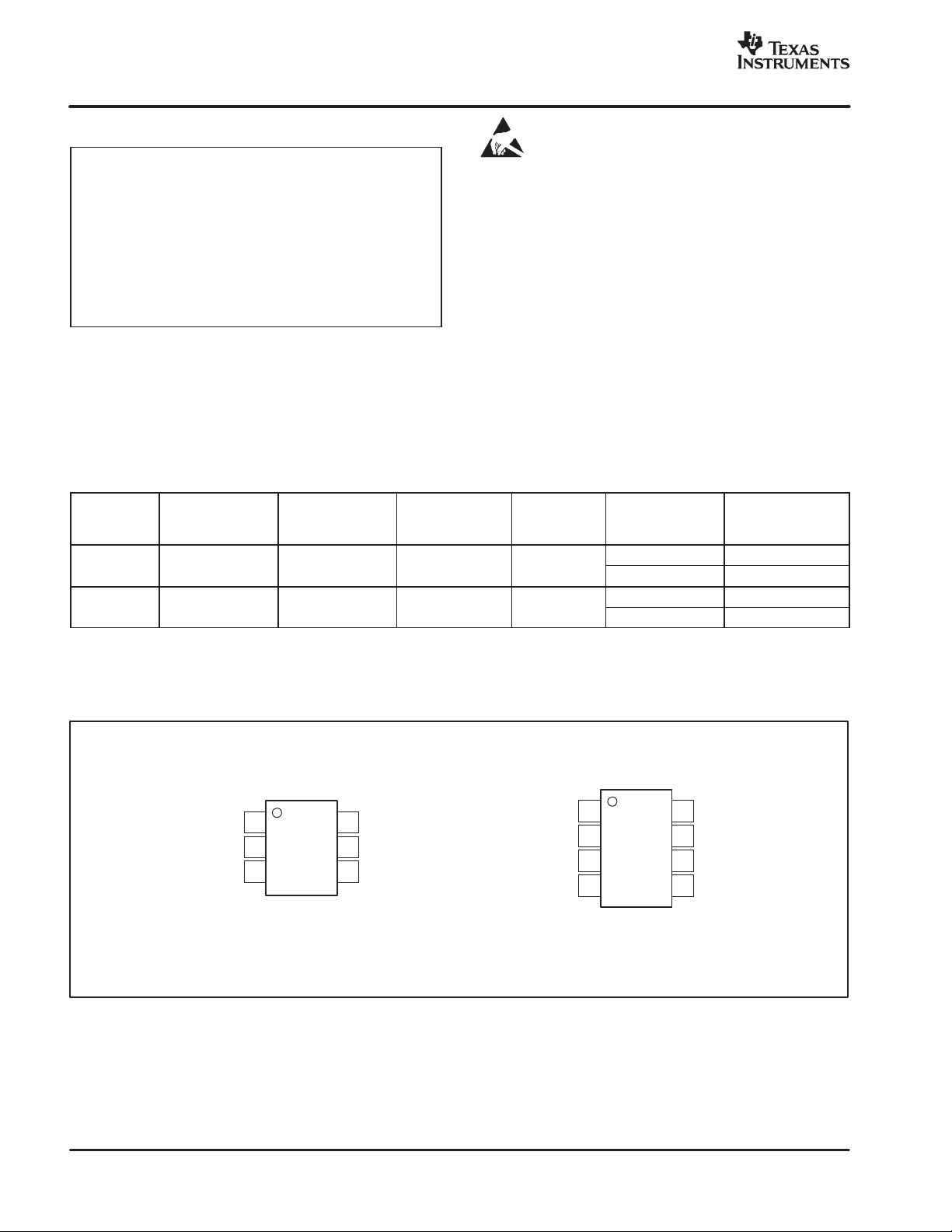

PIN CONFIGURATIONS

Top View

NOTE: Pin 1 is determined by orienting the package marking as indicated in the diagram.

ADD0

GND

GND

ADD1

SWD

V+

1

2

3

6

5

4

SOT23−6

T141

V+

GND

GND

GND

SWD

ADD1

ADD0

GND

1

2

3

4

8

7

6

5

MSOP−8

T14G

"#$#

SBAS347A − MARCH 2005 − REVISED JULY 2006

www.ti.com

3

ELECTRICAL CHARACTERISTICS

At T

A

= −40°C to +125°C and V

S

= +3.0V to +3.6V, unless otherwise noted.

TMP141

PARAMETER CONDITIONS MIN TYP MAX UNIT

TEMPERATURE INPUT

Range −40 +125 °C

Error T

ERROR

T = −25°C to +85°C ±0.2 ±2 °C

T = −40°C to +125°C ±3 °C

vs Supply ±0.2 ±0.5 °C/V

Resolution 10 Bits

0.25 °C

Default Conversion Time t

CONV

See Table 4 for conversion time settings. 162 190 218 ms

DIGITAL INPUT/OUTPUT PINS (SWD and ADD pins)

Input/Output Capacitance C

IN/OUT

3 pF

SWD PIN

Input Leakage Current I

L

GND < V

IN

< V

S

0.005 10 µA

I

L

GND < V

IN

< 5.5V and V

S

= GND/OPEN 0.005 µA

Input Logic Level Voltage (High) V

IH

2.1 V

S

+ 0.5 V

V

S

= 2.7V to 5.5V 0.6 × V

S

V

S

+ 0.5 V

Input Logic Level Voltage (Low) V

IL

−0.5 0.8 V

V

S

= 2.7V to 5.5V −0.5 0.25 × V

S

V

Input Hysteresis V

HYST

300 mV

Output Logic Level Voltage (Low) V

OL

I

OL

= 4mA 0.4 V

I

OL

= 50µA 0.2 V

Output OFF Current I

OH

0.005 10 µA

ADD0 and ADD1 PINS

Input Leakage Current I

L

GND < V

IN

< V

S

0.005 10 µA

Input Logic Level Voltage (High) V

IH

0.9 × V

S

V

S

+ 0.5 V

Input Logic Level Voltage (Low) V

IL

−0.5 0.1 × V

S

V

SensorPath CHARACTERISTICS

SWD Fall Time t

f

R

PULL-UP

= 1.25kΩ ± 30%, C

L

= 400pF 300 ns

SWD Rise Time t

r

R

PULL-UP

= 1.25kΩ ± 30%, C

L

= 400pF 1000 ns

Min. Inactive Time Between SWD Signals t

INACT

Bus at High Level 11 µs

Master or TMP141 Reset Drive Time t

RST

354 µs

TMP141 Detects Bus Activity t

SFEdet

9.6 µs

Master Drive Time

Data Bit 0 Write, Data Bit 0 Read t

Mtr0

11.8 17 µs

Data Bit 1 Write t

Mtr1

35.4 48.9 µs

Start Bit t

MtrS

80 109 µs

TMP141 Drive Time

Data Bit 0−1 Read t

SLout1

28.3 38.3 µs

Attention Request t

SLoutA

165 228 µs

Reset t

RST_MAX

After V

S

is Above 2.6V 95 500 ms

POWER SUPPLY

Specified Voltage Range 3.0 3.6 V

Operating Voltage Range 2.7 5.5 V

Quiescent Current I

Q

Standby 80 120 µA

While Converting

(1)

110 170 µA

Power-On Reset Voltage 1.5 2.6 V

TEMPERATURE RANGE

Specified Range −40 +125 °C

Operating Range −55 +127 °C

Storage Range −60 +150 °C

Thermal Resistance q

JA

MSOP-8 150 °C/W

SOT23-6 200 °C/W

(1)

SensorPath activity only has a slight effect on quiescent current.

"#$#

SBAS347A − MARCH 2005 − REVISED JULY 2006

www.ti.com

4

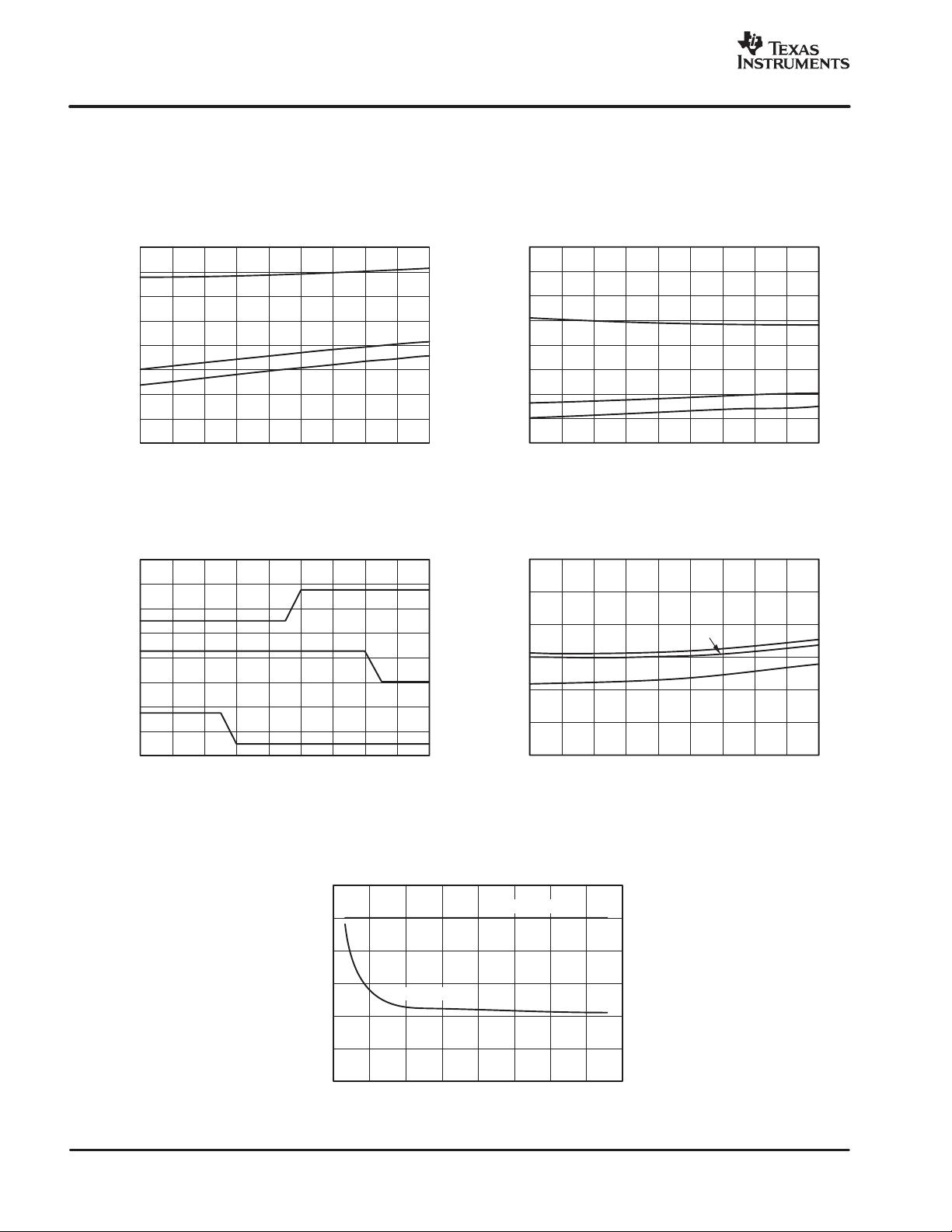

TYPICAL CHARACTERISTICS

At T

A

= −40°C to +125°C and V

S

= +3.0V to +3.6V, unless otherwise noted.

200

180

160

140

120

100

80

60

40

−

55

−

35

−

155 25456585105125

Temperature (

_

C)

I

Q

(

µ

A)

QUIESCENT CURRENT vs TEMPERATURE

3.3V

5.5V

2.7V

200

180

160

140

120

100

80

60

40

−

55

−

35

−

155 25456585105125

Temperature (

_

C)

I

STBY

(

µ

A)

I

STBY

vs TEMPERATURE

3.3V

5.5V

2.7V

1.0

0.8

0.6

0.4

0.2

0

−

0.2

−

0.4

−

0.6

−

55

−

35

−

155 25456585105125

Temperature (

_

C)

Error (

_

C)

TYPICAL PERFORMANCE FOR THREE UNITS

220

210

200

190

180

170

160

−

55

−

35

−

155 25456585105125

Temperature (

_

C)

Conversion Time −Default Setting (ms)

TYPICAL CONVERSION TIME vs TEMPERATURE

3.3V

5.5V

2.7V

120

110

100

90

80

70

60

0 200 400 600 800 1000 1200 1400 1600

Conversion Time (ms)

I

Q

(

µ

A)

QUIESCENT CURRENT vs CONVERSION TIME

Peak Current

Average Current

"#$#

SBAS347A − MARCH 2005 − REVISED JULY 2006

www.ti.com

5

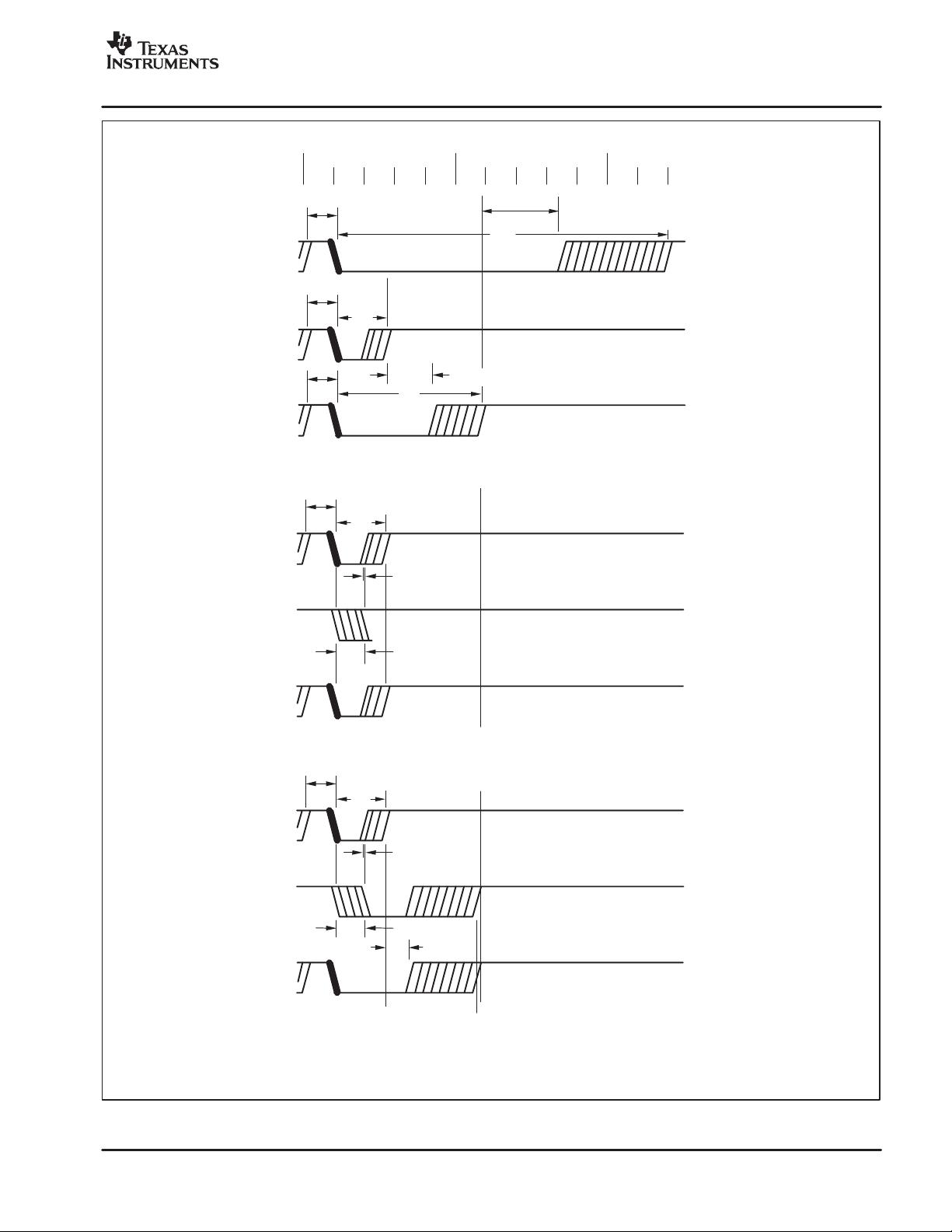

1a: Master Write timing and slave detection of the data placed on the SWD bus by the master.

1b: To place a ‘0’ on the bus, the slave does not drive the bus.

1c: To place a ‘1’ on the bus, the slave holds the bus low after detecting that the master has started a data bit.

0

µ

s50

µ

s 100

µ

s

Master Write 0

Master Write 1

t

INACT

t

INACT

t

Mtr1

t

Mtr0

SlvDetectData1

Master Write Start

t

INACT

t

MtrS

DetectStart

t

INACT

t

Mtr0

SlvDetect_st

(1)

t

SFEdet

Master starts a bit

Slave detects bus activity and

does nothing, leaving the bit a 0.

Master Read 0

t

INACT

t

Mtr0

SlvDetect_st

(1)

t

SFEdet

MstDetect_1

Master starts a bit

Slave pulls Bus low to send back a 1

Master Read 1

NOTE: (1) Margin from t

SFEdet

to t

Mtr0

is 2.2µs.

Figure 1. TMP141 Read and Write Signal Timing

剩余24页未读,继续阅读

资源评论

2301_76396056

- 粉丝: 1

- 资源: 21

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功