没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS92001.pdf

温馨提示

试读

19页

LVDS缓冲器

资源推荐

资源详情

资源评论

OUT-

OUT+

EN

IN-

IN+

GND

IN-

IN+

N/C

EN

OUT-

OUT+

VCC

1

2

3

4

8

6

5

7

GND

DAP

GND

IN-

IN+

N/C

EN

OUT-

OUT+

VCC

1

2

3

4

8

6

5

7

DS92001

www.ti.com

SNLS147F –JUNE 2002–REVISED APRIL 2013

DS92001 3.3V B/LVDS-BLVDS Buffer

Check for Samples: DS92001

1

FEATURES

DESCRIPTION

The DS92001 B/LVDS-BLVDS Buffer takes a BLVDS

2

• Single +3.3 V Supply

input signal and provides a BLVDS output signal. In

• Receiver Inputs Accept LVDS/CML/LVPECL

many large systems, signals are distributed across

Signals

backplanes. One of the limiting factors for system

• TRI-STATE Outputs

speed is the "stub length" or the distance between

the transmission line and the unterminated receivers

• Receiver Input Threshold < ±100 mV

on individual cards. Although it is generally

• Fast Propagation Delay of 1.4 ns (typ)

recognized that this distance should be as short as

• Low Jitter 400 Mbps Fully Differential Data

possible to maximize system performance, real-world

Path

packaging concerns often make it difficult to make the

stubs as short as the designer would like.

• Compatible with BLVDS 10-bit SerDes (40MHz)

The DS92001 has edge transitions optimized for

• Compatible with ANSI/TIA/EIA-644-A LVDS

multidrop backplanes where the switching frequency

Standard

is in the 200 MHz range or less. The output edge rate

• Available in SOIC and Space Saving WSON

is critical in some systems where long stubs may be

Package

present, and utilizing a slow transition allows for

• Industrial Temperature Range

longer stub lengths.

The DS92001, available in the WSON package, will

allow the receiver inputs to be placed very close to

the main transmission line, thus improving system

performance.

A wide input dynamic range allows the DS92001 to

receive differential signals from LVPECL, CML as

well as LVDS sources. This will allow the device to

also fill the role of an LVPECL-BLVDS or CML-

BLVDS translator.

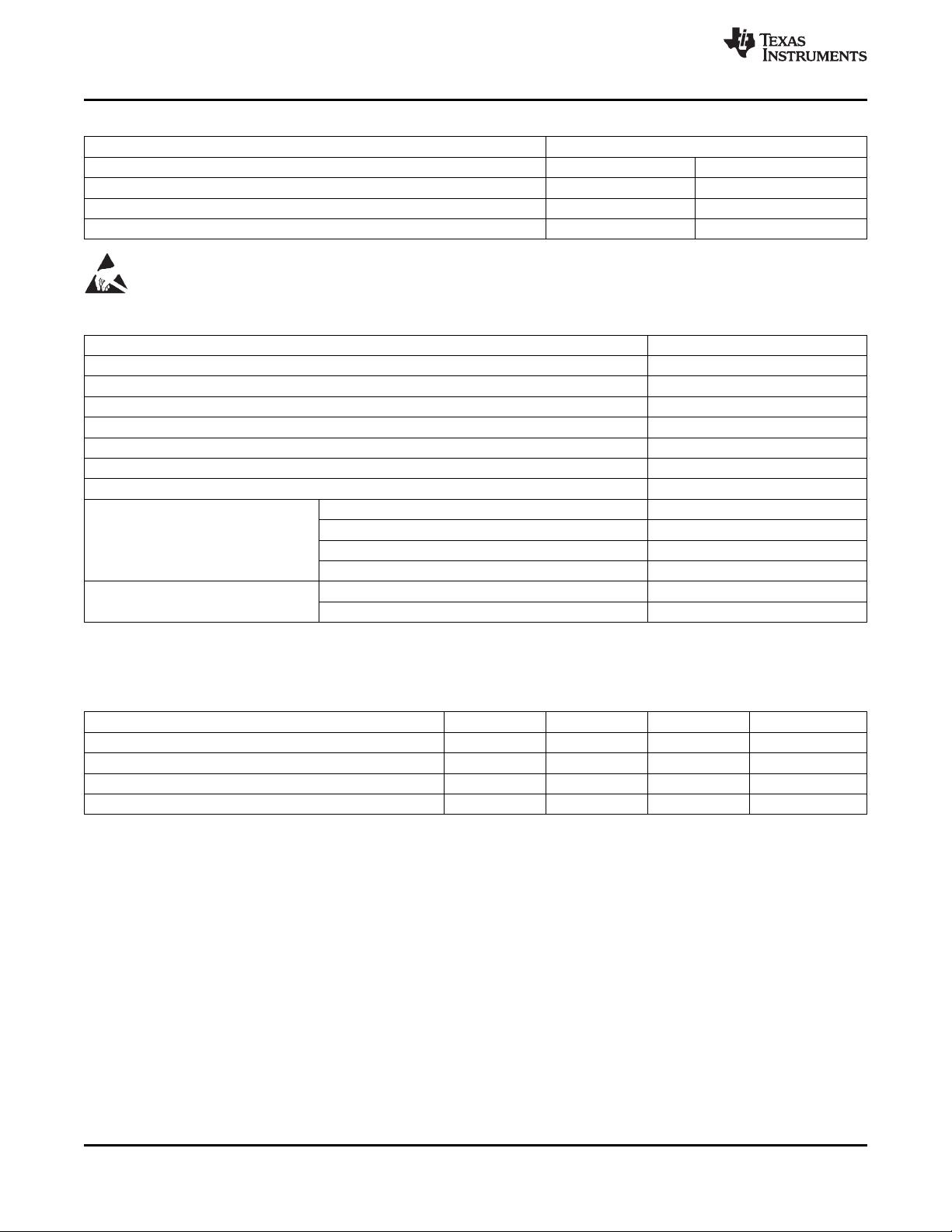

Connection and Block Diagrams

Figure 1. SOIC Package Number D0008A Figure 2. WSON Package Number NGK0008A

Top View Top View

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2002–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

DS92001

SNLS147F –JUNE 2002–REVISED APRIL 2013

www.ti.com

Table 1. Functional Operation

BLVDS Inputs BLVDS Outputs

[IN+] − [IN−] OUT+ OUT−

VID ≥ 0.1V H L

VID ≤ −0.1V L H

−0.1V ≤ VID ≤ 0.1V Undefined Undefined

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings

(1)(2)

Supply Voltage (V

CC

) −0.3V to +4V

LVCMOS/LVTTL Input Voltage (EN) −0.3V to (V

CC

+ 0.3V)

B/LVDS Receiver Input Voltage (IN+, IN−) −0.3V to +4V

BLVDS Driver Output Voltage (OUT+, OUT−) −0.3V to +4V

BLVDS Output Short Circuit Current Continuous

Junction Temperature +150°C

Storage Temperature Range −65°C to +150°C

Lead Temperature Range Soldering (4 sec.) +260°C

Maximum Package Power Dissipation at D Package 726 mW

25°C

Derate D Package 5.8 mW/°C above +25°C

NGK Package 2.44 W

Derate NGK Package 19.49 mW/°C above +25°C

ESD Ratings (HBM, 1.5kΩ, 100pF) ≥2.5kV

(EIAJ, 0Ω, 200pF) ≥250V

(1) “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be ensured. They are not meant to imply

that the device should be operated at these limits. The table of “Electrical Characteristics” specifies conditions of device operation.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

Recommended Operating Conditions

Min Typ Max Units

Supply Voltage (V

CC

) 3.0 3.3 3.6 V

Receiver Differential Input Voltage (V

ID

) with V

CM

=1.2V 0.1 2.4 |V|

Operating Free Air Temperature −40 +25 +85 °C

B/LVDS Input Rise/Fall 20% to 80% 2 20 ns

2 Submit Documentation Feedback Copyright © 2002–2013, Texas Instruments Incorporated

Product Folder Links: DS92001

DS92001

www.ti.com

SNLS147F –JUNE 2002–REVISED APRIL 2013

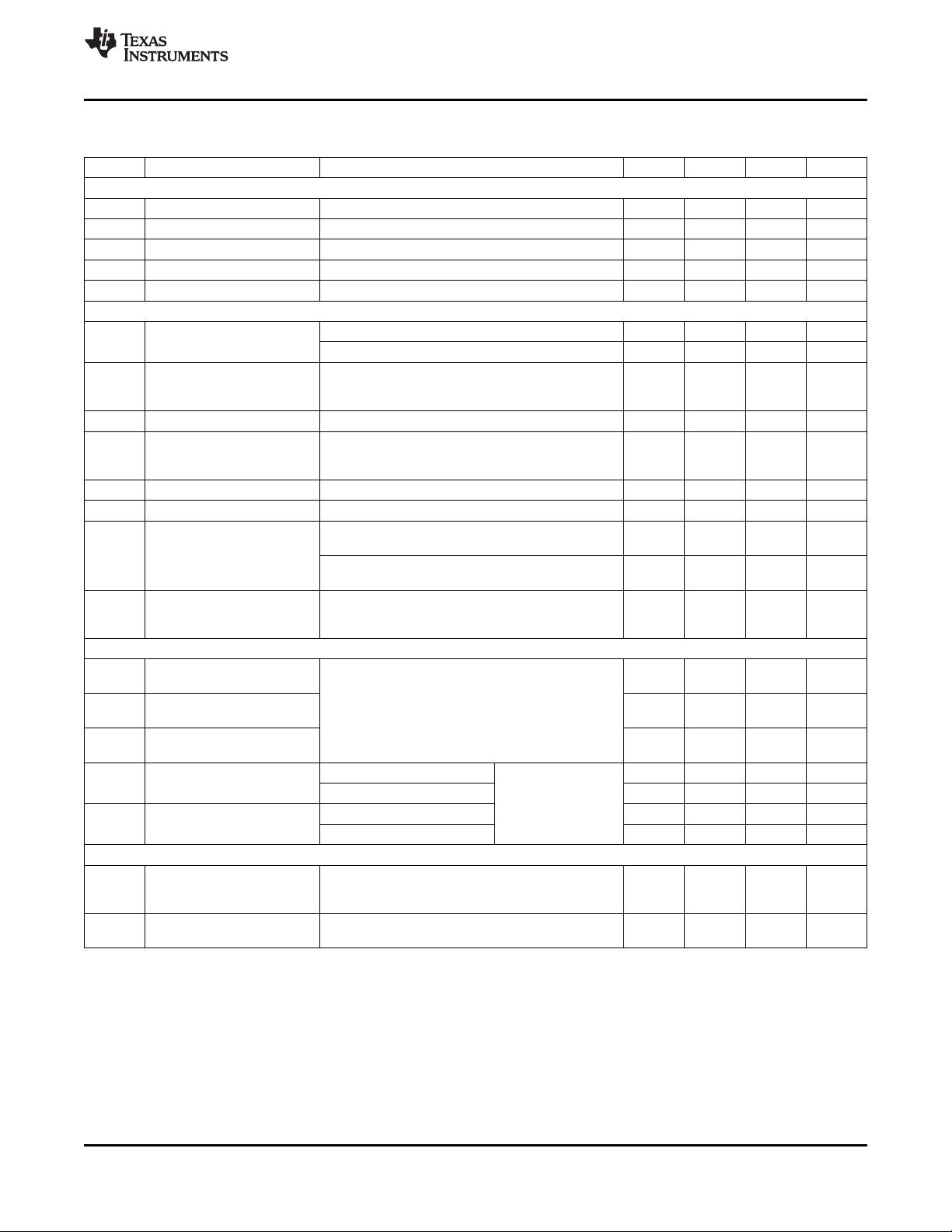

Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

(1)(2)

Symbol Parameter Conditions Min Typ Max Units

LVCMOS/LVTTL DC SPECIFICATIONS (EN)

V

IH

High Level Input Voltage 2.0 V

CC

V

V

IL

Low Level Input Voltage GND 0.8 V

I

IH

High Level Input Current V

IN

= V

CC

or 2.0V +7 +20 μA

I

IL

Low Level Input Current V

IN

= GND or 0.8V −10 ±1 +10 μA

V

CL

Input Clamp Voltage I

CL

= −18 mA −0.6 −1.5 V

BLVDS OUTPUT DC SPECIFICATIONS (OUT)

|V

OD

| Differential Output Voltage

(1)

R

L

= 27Ω 250 350 500 mV

R

L

= 50Ω 350 450 600 mV

ΔV

OD

Change in Magnitude of V

OD

for Complimentary Output RL = 27Ω or 50Ω See Figure 3 and Figure 4 20 mV

States

V

OS

Offset Voltage R

L

= 27Ω or R

L

= 50Ω 1.1 1.25 1.375 V

ΔV

OS

Change in Magnitude of V

OS

See Figure 3

for Complimentary Output 2 20 mV

States

I

OZ

Output TRI-STATE Current EN = 0V, V

OUT

= V

CC

or GND −20 ±5 +20 μA

I

OFF

Power-Off Leakage Current V

CC

= 0V or Open Circuit, V

OUT

= 3.6V −20 ±5 +20 μA

I

OS1

Output Short Circuit EN = V

CC

, V

CM

= 1.2V,V

ID

= 200mV, V

OUT+

= 0V, or

−30 −60 mA

Current

(3)

V

ID

= −200mV, V

CM

= 1.2V, V

OUT−

= 0V

V

ID

= −200mV, V

CM

= 1.2V, V

OUT+

= V

CC

, or

53 80 mA

V

ID

= 200mV, V

CM

=1.2V, V

OUT−

= V

CC

I

OSD

Differential Output Short EN = V

CC

, V

ID

= |200mV|, V

CM

. = 1.2V, V

OD

= 0V

Circuit Current

(3)

(connect true and complement outputs through a |30| |42| mA

current meter)

B/LVDS RECEIVER DC SPECIFICATIONS (IN)

V

TH

Differential Input High V

CM

= +0.05V, +1.2V or +3.25V −30 −5 mV

Threshold

(4)

V

TL

Differential Input Low −70 −30 mV

Threshold

(4)

V

CMR

Common Mode Voltage |V

ID

|/2 V

CC

V

Range

(4)

−|V

ID

|/2

I

IN

Input Current V

IN

= V

CC

V

CC

= 3.6V or 0V |1.5| |20| μA

V

IN

= 0V |1.5| |20| μA

ΔI

IN

Change in Magnitude of I

IN

V

IN

= V

CC

1 6 μA

V

IN

= 0V 1 6 μA

SUPPLY CURRENT

I

CCD

Total Dynamic Supply EN = V

CC

, R

L

= 27Ω or 50Ω, C

L

= 15 pF, 50 65 mA

Current (includes load Freq. = 200MHz 50% duty cycle,

current) V

ID

= 200mV, V

CM

= 1.2V

I

CCZ

TRI-STATE Supply Current EN = 0V,Freq. = 200MHz 50% duty cycle, 36 46 mA

V

ID

= 200mV, V

CM

= 1.2V

(1) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground

except V

ID

, V

OD

, V

TH

, V

TL

, and ΔV

OD

. V

OD

has a value and direction. Positive direction means OUT+ is a more positive voltage than

OUT−.

(2) All typical are given for V

CC

= +3.3V and T

A

= +25°C, unless otherwise stated.

(3) Output short circuit current (I

OS

) is specified as magnitude only, minus sign indicates direction only.

(4) The parameters are specified by design. The limits are based on statistical analysis of the device performance over the PVT (process,

voltage and temperature) range.

Copyright © 2002–2013, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: DS92001

DS92001

SNLS147F –JUNE 2002–REVISED APRIL 2013

www.ti.com

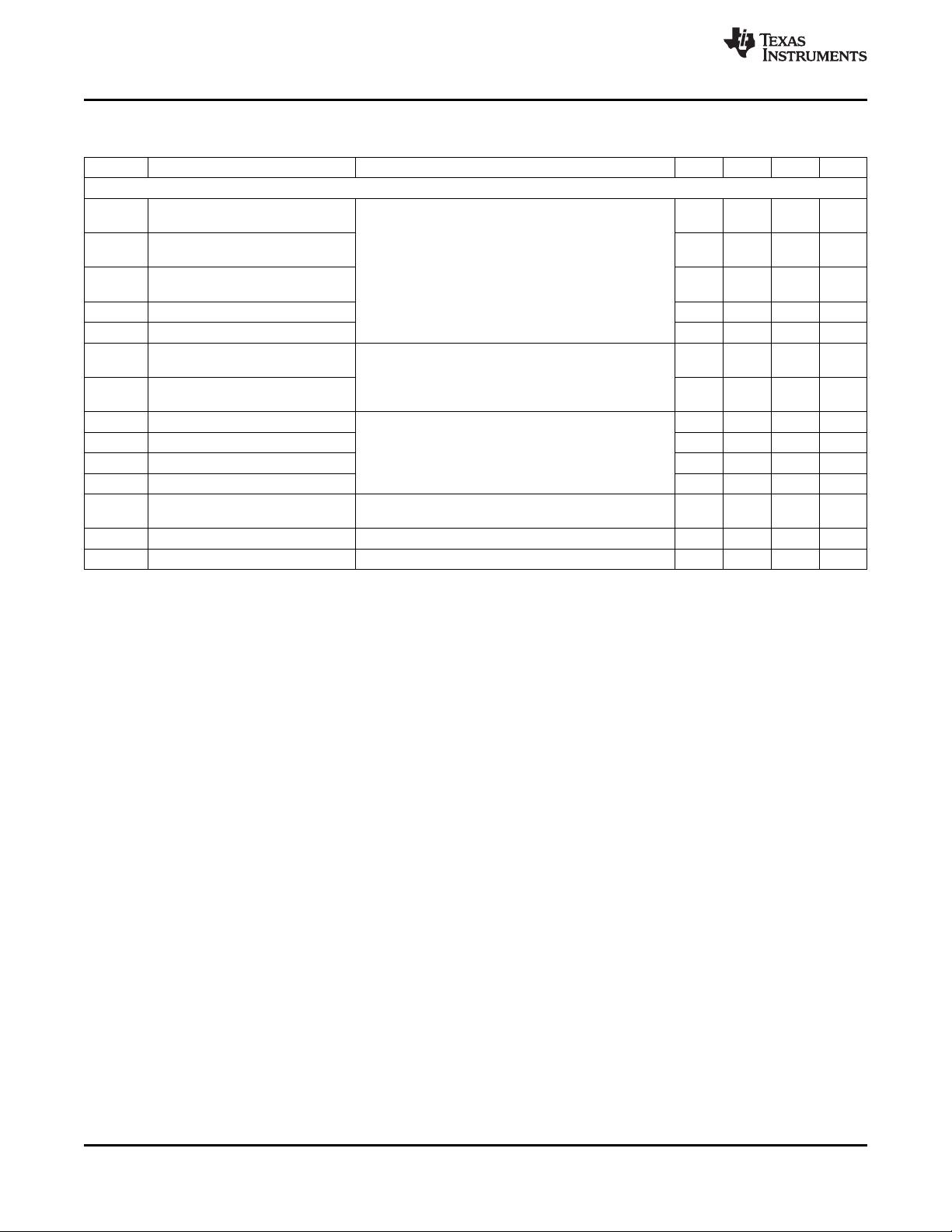

AC Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

(1)

Symbol Parameter Conditions Min Typ Max Units

LVDS OUTPUT AC SPECIFICATIONS (OUT)

t

PHLD

Differential Propagation Delay High V

ID

= 200mV, V

CM

= 1.2V, 1.0 1.4 2.0 ns

to Low

(2)

R

L

= 27Ω or 50Ω, C

L

= 15pF

See Figure 5 and Figure 6

t

PLHD

Differential Propagation Delay Low 1.0 1.4 2.0 ns

to High

(2)

t

SKD1

Pulse Skew |t

PLHD

− t

PHLD

| 0 20 200 ps

(measure of duty cycle)

(3)(4)

t

SKD3

Part-to-Part Skew

(3)(5)

0 200 300 ps

t

SKD4

Part-to-Part Skew

(3)(6)

0 1 ns

t

LHT

Rise Time

(3)(2)

R

L

= 50Ω or 27Ω, C

L

= 15pF 0.350 0.6 1.0 ns

20% to 80% points See Figure 5 and Figure 7

t

HLT

Fall Time

(3)(2)

0.350 0.6 1.0 ns

80% to 20% points

t

PHZ

Disable Time (Active High to Z) R

L

= 50Ω, C

L

= 15pF See Figure 8 and Figure 9 3 25 ns

t

PLZ

Disable Time (Active Low to Z) 3 25 ns

t

PZH

Enable Time (Z to Active High) 100 120 ns

t

PZL

Enable Time (Z to Active Low) 100 120 ns

t

DJ

LVDS Data Jitter, Deterministic V

ID

= 300mV; PRBS = 2

23

− 1 data; V

CM

= 1.2V at

78 ps

(Peak-to-Peak)

(7)

400Mbps (NRZ)

t

RJ

LVDS Clock Jitter, Random

(7)

V

ID

= 300mV; V

CM

= 1.2V at 200MHz clock 36 ps

f

MAX

Maximum specified frequency

(8)

V

ID

= 200mV, V

CM

= 1.2V 200 300 MHz

(1) All typical are given for V

CC

= +3.3V and T

A

= +25°C, unless otherwise stated.

(2) Propagation delay, rise and fall times are specified by design and characterization to 200MHz. Generator for these tests: 50MHz ≤ f ≤

200MHz, Zo = 50Ω, tr, tf ≤ 0.5ns. Generator used was HP8130A (300MHz capability).

(3) The parameters are specified by design. The limits are based on statistical analysis of the device performance over the PVT (process,

voltage and temperature) range.

(4) t

SKD1

, |t

PLHD

− t

PHLD

|, is the magnitude difference in differential propagation delay time between the positive going edge and the negative

going edge of the same channel (a measure of duty cycle).

(5) t

SKD3

, Part to Part Skew, is defined as the difference between the minimum and maximum specified differential propagation delays. This

specification applies to devices at the same V

CC

and within 5°C of each other within the operating temperature range. This parameter

specified by design and characterization.

(6) t

SKD4

, Part to Part Skew, is the differential channel-to- channel skew of any event between devices. This specification applies to devices

over recommended operating temperature and voltage ranges, and across process distribution. t

SKD4

is defined as |Max − Min|

differential propagation delay.

(7) The parameters are specified by design. The limits are based on statistical analysis of the device performance over the PVT range with

the following test equipment setup: Agilent 86130A used as stimulus, 5 feet of RG142B cable with DUT test board and Agilent 86100A

(digital scope mainframe) with Agilent 86122A (20GHz scope module). Data input jitter pk to pk = 22 picoseconds; Clock input jitter = 24

picoseconds; t

DJ

measured 100 picoseconds, t

RJ

measured 60 picoseconds.

(8) f

MAX

test: Generator (HP8133A or equivalent), Input duty cycle = 50%. Output criteria: VOD ≥ 200mV, Duty Cycle better than 45/55%.

This specification is specified by design and characterization. A minimum is specified, which means that the device will operate to

specified conditions from DC to the minimum specified AC frequency. The typical value is always greater than the minimum

specification.

4 Submit Documentation Feedback Copyright © 2002–2013, Texas Instruments Incorporated

Product Folder Links: DS92001

剩余18页未读,继续阅读

资源评论

m0_745259962023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

m0_745259962023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 CSDN_1872023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

CSDN_1872023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 2301_763960562023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

2301_763960562023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

不觉明了

- 粉丝: 3175

- 资源: 5443

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功