没有合适的资源?快使用搜索试试~ 我知道了~

TI-ADS8686S.pdf

需积分: 5 0 下载量 67 浏览量

2022-11-27

00:07:04

上传

评论 4

收藏 1.72MB PDF 举报

温馨提示

试读

102页

TI-ADS8686S.pdf

资源推荐

资源详情

资源评论

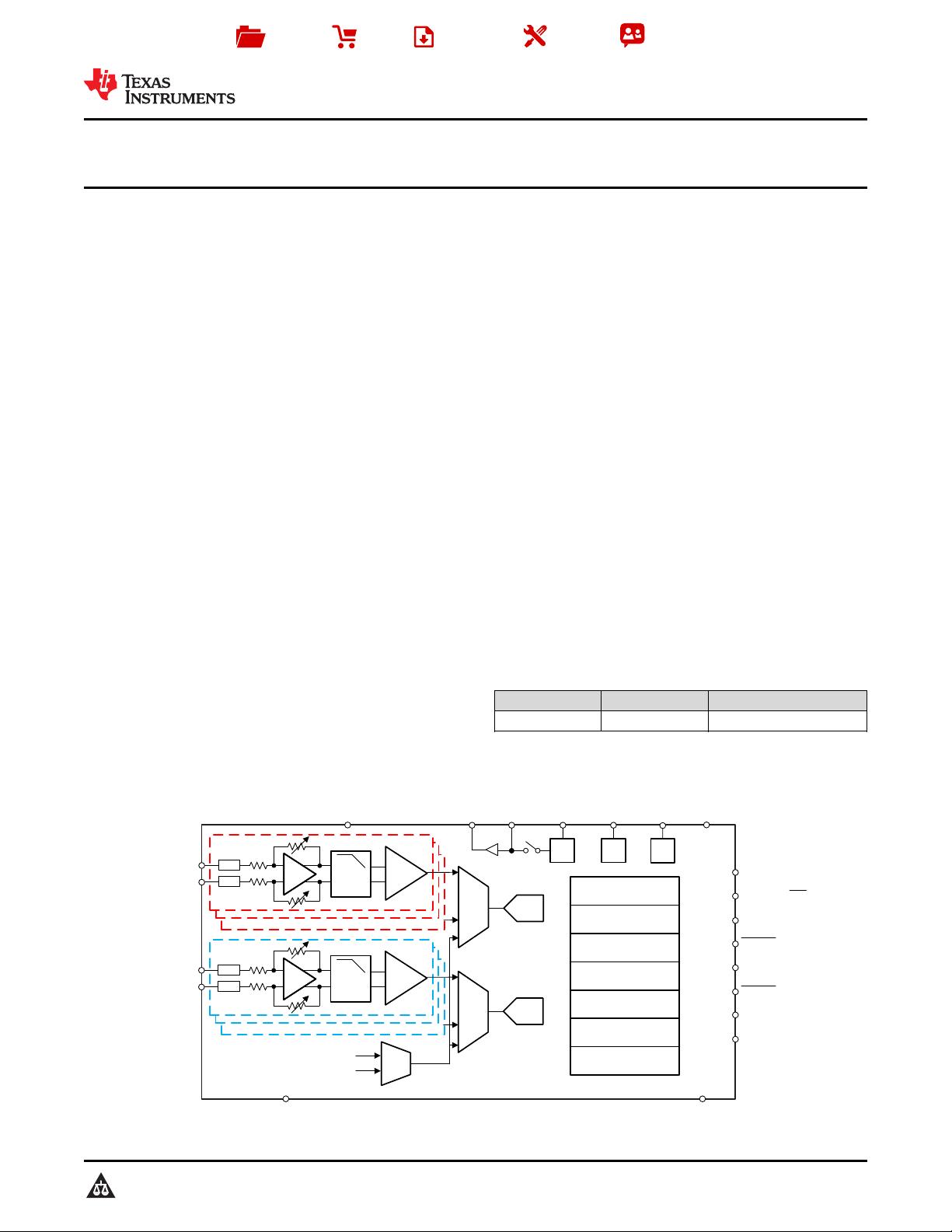

DGNDAGND

DVDD

AVDD

ADC

Driver

Serial - Parallel -

Byte Interface

1 M

Clamp

2

nd

Order

PROG

LPF

Clamp

PGA

AIN_nA

AIN_nAGND

1 M

9:1

MUX

2:1

MUX

AVDD

ALDO

ADS8686S

16-BIT

SAR

REFIO REFSEL REGCAP

ALDO

2.5 V

REF

REGCAPD

DLDO

REFCAP

CH0A

CH7A

ADC

Driver

1 M

Clamp

2

nd

Order

PROG

LPF

Clamp

PGA

AIN_nB

AIN_nBGND

1 M

9:1

MUX

CH0B

CH7B

16-BIT

SAR

Digital OSR Filter

Channel Sequencer

Burst Capture

CRC

Self Diagnosys

Dual Simultaneous

Sampling

DB[15:0]

SER/BYTE/PAR

SDOx/SDI

SER1W

OSR

RESET

CONVST

BUSY

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

ADS8686S

SBAS905C –NOVEMBER 2019–REVISED JULY 2020

ADS8686S 16-Channel, 16-Bit, 1-MSPS, Dual, Simultaneous Sampling ADC with Integrated

Analog Front-End

1

1 Features

1

• 16-channel, 16-bit ADC with integrated analog

front-end

• Dual simultaneous sampling: 8x2 channels

• Supply:

– Analog: 5 V

– Digital: 1.8 V to 5 V

• Constant 1-MΩ input impedance front-end

• Independently programmable input ranges with

20% overrange

• Programmable low-pass filter:

– 15 kHz, 39 kHz, 376 kHz

• Excellent DC and AC performance

• On-chip reference and reference buffer

• Excellent over temperature performance

• Overvoltage input clamp with 8-kV ESD

• Optional cyclic redundancy check (CRC) error

checking

• On-chip self diagnostic function

• Temperature range: –40°C to +125°C

2 Applications

• Multifunction relays

• Servo drive position sensors

• Analog input modules

• Data acquisition (DAQ)

3 Description

The ADS8686S is a 16-channel data acquisition

(DAQ) system based on a dual simultaneous-

sampling, 16-bit successive approximation register

(SAR) analog-to-digital converter (ADC). The

ADS8686S features a complete analog front-end for

each channel with an input clamp, 1-MΩ input

impedance, independently programmable gain

amplifier (PGA), programmable low-pass filter, and an

ADC input driver. The device also features a low-drift,

precision reference with a buffer to drive the ADCs. A

flexible digital interface supporting serial, parallel, and

byte communication enables the device to be used

with a variety of host controllers.

The ADS8686S can be configured to accept ±10-V,

±5-V, or ±2.5-V bipolar inputs with a 20% overrange

option using a single 5-V supply. The high input

impedance allows direct connection with sensors and

transformers, thus eliminating the need for external

driver circuits. The ADS8686S has a highly

configurable channel sequencer to reduce the

sequencing overhead on the backend controller or

processor. The high performance and accuracy,

along with zero-latency conversions offered by this

device make the ADS8686S a great choice for

multiple industrial applications.

Device Information

(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

ADS8686S LQFP (80) 14.00 mm x 14.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Device Block Diagram

2

ADS8686S

SBAS905C –NOVEMBER 2019–REVISED JULY 2020

www.ti.com

Product Folder Links: ADS8686S

Submit Documentation Feedback Copyright © 2019–2020, Texas Instruments Incorporated

Table of Contents

1 Features.................................................................. 1

2 Applications ........................................................... 1

3 Description ............................................................. 1

4 Revision History..................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 6

6.1 Absolute Maximum Ratings ...................................... 6

6.2 ESD Ratings.............................................................. 6

6.3 Recommended Operating Conditions....................... 7

6.4 Thermal Information.................................................. 7

6.5 Electrical Characteristics........................................... 7

6.6 Timing Requirements.............................................. 14

6.7 Switching Characteristics........................................ 15

6.8 Timing Specifications: Universal ............................ 17

6.9 Timing Requirements: Parallel Data Read.............. 19

6.10 Timing Requirements: Serial Data Read .............. 20

6.11 Typical Characteristics.......................................... 21

7 Detailed Description............................................ 28

7.1 Overview ................................................................. 28

7.2 Functional Block Diagram ....................................... 28

7.3 Feature Description................................................. 29

7.4 Device Functional Modes........................................ 37

7.5 Programming........................................................... 56

7.6 Register Maps......................................................... 62

8 Application and Implementation ........................ 90

8.1 Application Information............................................ 90

8.2 Typical Applications ................................................ 90

9 Power Supply Recommendations...................... 94

9.1 Power Supplies ....................................................... 94

10 Layout................................................................... 95

10.1 Layout Guidelines ................................................. 95

10.2 Layout Examples................................................... 95

11 Device and Documentation Support ................. 96

11.1 Device Support...................................................... 96

11.2 Documentation Support ....................................... 96

11.3 Receiving Notification of Documentation Updates 96

11.4 Support Resources ............................................... 96

11.5 Trademarks........................................................... 96

11.6 Electrostatic Discharge Caution............................ 96

11.7 Glossary................................................................ 96

12 Mechanical, Packaging, and Orderable

Information ........................................................... 96

4 Revision History

Changes from Revision B (May 2020) to Revision C Page

• Changed AC performance parameters................................................................................................................................. 11

Changes from Revision A (March 2020) to Revision B Page

• Changed device status from advance information to production data .................................................................................. 1

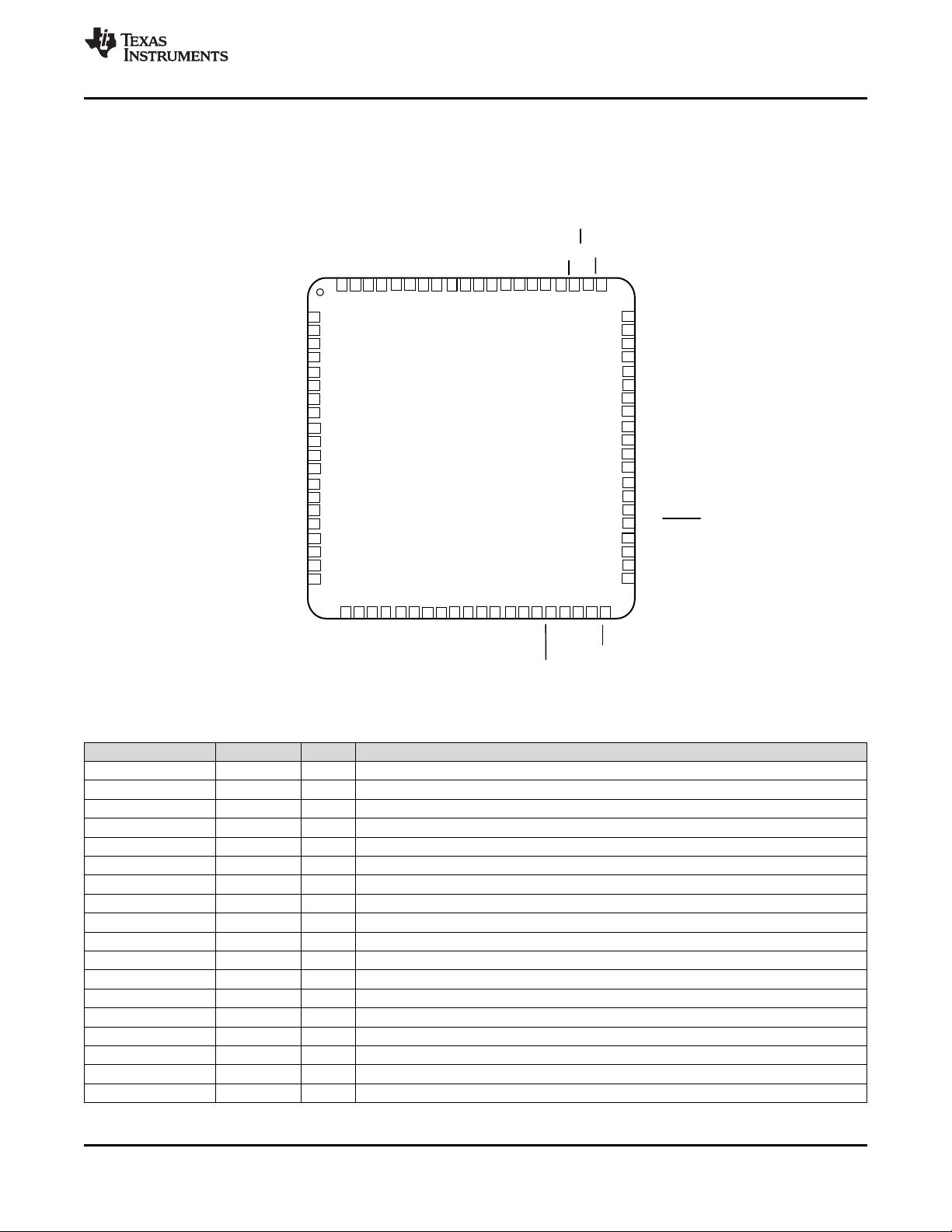

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

61

62

6364

AIN

_3BGND

AIN

_3B

AIN

_2BGND

AIN

_2

B

65

6667

68

AIN

_1

BGND

AIN

_1B

AIN

_0BGND

AIN

_0B

697071

72

AGND

AVDD

REGCAP

REGGND

73

747576

CONVST

BUSY

CHSEL

2

CHSEL

1

77787980

CHSEL

0

CS

SCLK

/RD

WR

/BURST

4039

38

37363534

33

32

3130

29282726

2524232221

DB15/0S2

DB14/0S1

DB13/0S0

DB12/SDOA

DB11/SDOB

DB10/SDI

DB9/BYTESEL

DB8

REGCAPD

REGGNDD

DGND

DVDD

DB7

DB6

DB5/CRCEN

DB4/SER1W

DB3

DB2

DB1

DB0

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

(Not to Scale)

ADS8686S

TOP VIEW

AIN

_3AGND

AIN

_3A

AIN

_2AGND

AIN

_2A

AIN

_1AGND

AIN

_1A

AIN

_0AGND

AIN

_

0A

AGND

AVDD

REFCAP

REFGND

REFIO

REFIO

_GND

REFSEL

RESET

SEQEN

HW

_RNGSEL

1

SER

/BYTE

/PAR

HW

_RNGSEL0

AIN

_4BGND

AIN

_4B

AIN

_5

BGND

AIN

_5

B

AGND

AVDD

AIN

_6B

AIN

_6BGND

AIN

_7

B

AIN

_7BGND

AIN

_7AGND

AIN

_7A

AIN

_6AGND

AIN

_6A

AVDD

AGND

AIN

_5A

AIN

_5AGND

AIN

_4A

AIN

_4AGND

3

ADS8686S

www.ti.com

SBAS905C –NOVEMBER 2019–REVISED JULY 2020

Product Folder Links: ADS8686S

Submit Documentation FeedbackCopyright © 2019–2020, Texas Instruments Incorporated

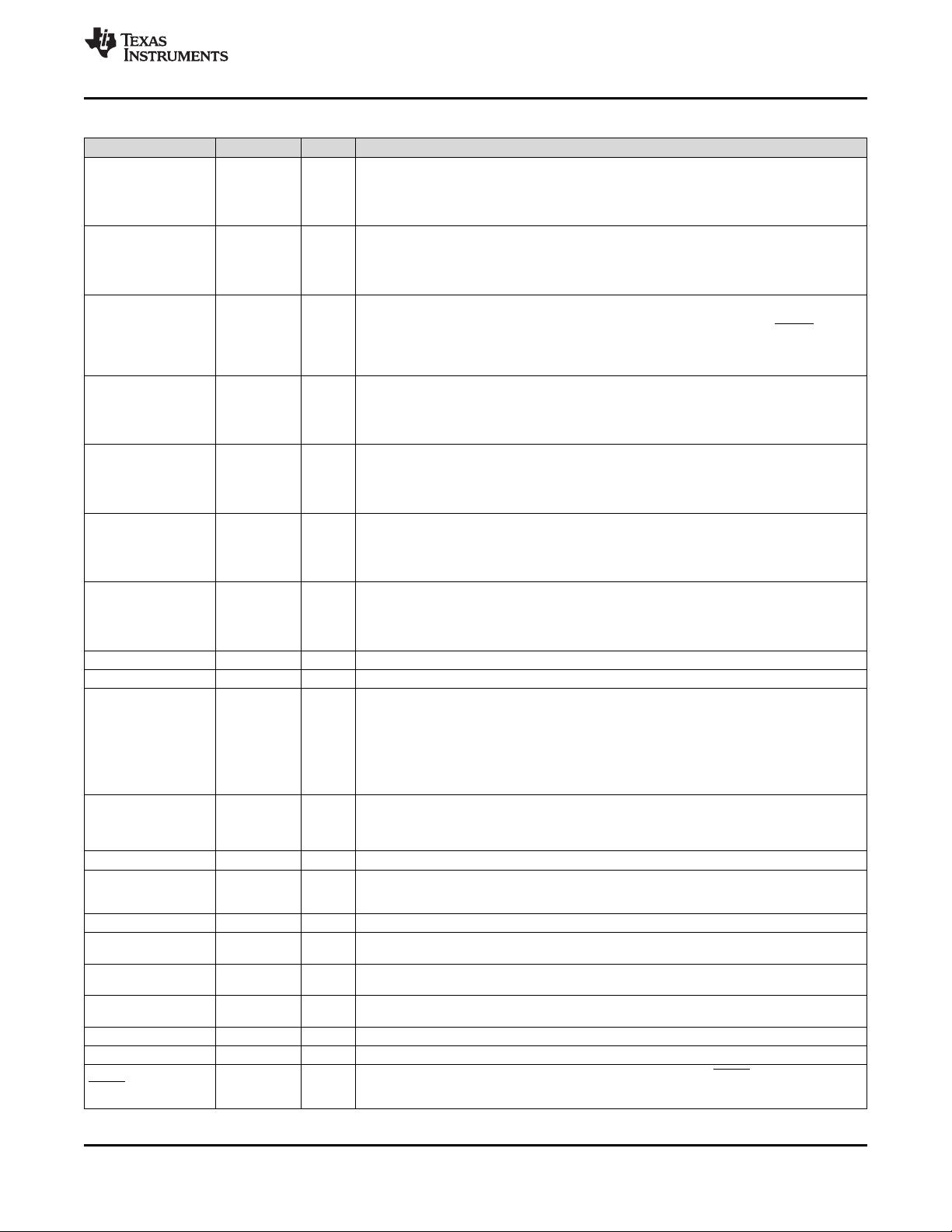

(1) AI = analog input, AO = analog output, AIO = analog input/output, DI = digital input, DO = digital output, DIO = digital input/output,

P = power supply.

5 Pin Configuration and Functions

PM Package: PZA

80-Pin LQFP

Top View

Pin Functions

NAME NO. TYPE

(1)

DESCRIPTION

AGND 5, 16, 29, 72 P Analog supply ground pins

AIN_0AGND 27 AI Analog input channel 0A: negative input

AIN_0A 28 AI Analog input channel 0A: positive input

AIN_0BGND 74 AI Analog input channel 0B: negative input

AIN_0B 73 AI Analog input channel 0B: positive input

AIN_1AGND 25 AI Analog input channel 1A: negative input

AIN_1A 26 AI Analog input channel 1A: positive input

AIN_1BGND 76 AI Analog input channel 1B: negative input

AIN_1B 75 AI Analog input channel 1B: positive input

AIN_2AGND 23 AI Analog input channel 2A: negative input

AIN_2A 24 AI Analog input channel 2A: positive input

AIN_2BGND 78 AI Analog input channel 2B: negative input

AIN_2B 77 AI Analog input channel 2B: positive input

AIN_3AGND 21 AI Analog input channel 3A: negative input

AIN_3A 22 AI Analog input channel 3A: positive input

AIN_3BGND 80 AI Analog input channel 3B: negative input

AIN_3B 79 AI Analog input channel 3B: positive input

AIN_4AGND 20 AI Analog input channel 4A: negative input

4

ADS8686S

SBAS905C –NOVEMBER 2019–REVISED JULY 2020

www.ti.com

Product Folder Links: ADS8686S

Submit Documentation Feedback Copyright © 2019–2020, Texas Instruments Incorporated

Pin Functions (continued)

NAME NO. TYPE

(1)

DESCRIPTION

AIN_4A 19 AI Analog input channel 4A: positive input

AIN_4BGND 1 AI Analog input channel 4B: negative input

AIN_4B 2 AI Analog input channel 4B: positive input

AIN_5AGND 18 AI Analog input channel 5A: negative input

AIN_5A 17 AI Analog input channel 5A: positive input

AIN_5BGND 3 AI Analog input channel 5B: negative input

AIN_5B 4 AI Analog input channel 5B: positive input

AIN_6AGND 13 AI Analog input channel 6A: negative input

AIN_6A 14 AI Analog input channel 6A: positive input

AIN_6BGND 8 AI Analog input channel 6B: negative input

AIN_6B 7 AI Analog input channel 6B: positive input

AIN_7AGND 11 AI Analog input channel 7A: negative input

AIN_7A 12 AI Analog input channel 7A: positive input

AIN_7BGND 10 AI Analog input channel 7B: negative input

AIN_7B 9 AI Analog input channel 7B: positive input

AVDD 6, 15, 30, 71 P

Analog supply pins. Decouple these pins to the closest AGND pins.

See the Power Supply Recommendations section.

BUSY 67 DO Logic output indicating an ongoing conversion; see the BUSY (Output) section.

CHSEL0 64 DI

Logic input pin to select the channel or program the hardware mode sequencer; see the CHSEL[2:0]

(Input) section.

CHSEL1 65 DI

Logic input pin to select the channel or program the hardware mode sequencer; see the CHSEL[2:0]

(Input) section.

CHSEL2 66 DI

Logic input pin to select the channel or program the hardware mode sequencer; see the CHSEL[2:0]

(Input) section.

CONVST 68 DI

Logic input to control the conversion start input for channel group A and channel group B; see the

CONVST (Input) section.

CS 63 DI Active low logic input chip select; see the CS (Input) section.

DB0 41 DIO

This pin is the data input/output DB0 (LSB) in parallel and parallel byte interface modes.

In serial mode, this pin must be connected to DGND.

See the DB[3:0] (Input/Output) section.

DB1 42 DIO

This pin is the data input/output DB1 in parallel and parallel byte interface modes.

In serial mode, this pin must be connected to DGND.

See the DB[3:0] (Input/Output) section.

DB2 43 DIO

This pin is the data input/output DB2 in parallel and parallel byte interface modes.

In serial mode, this pin must be connected to DGND.

See the DB[3:0] (Input/Output) section.

DB3 44 DIO

This pin is the data input/output DB3 in parallel and parallel byte interface modes.

In serial mode, this pin must be connected to DGND.

See the DB[3:0] (Input/Output) section.

DB4/SER1W 45 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB4 in parallel and parallel byte interface modes.

This pin is the logic input pin in serial mode to configure data capture using both SDOA and SDOB or

just SDOA. The signal state is latched on the release of a full RESET, and requires an additional full

RESET to be reconfigured.

See the DB4/SER1W (Input/Output) section.

DB5/CRCEN 46 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB5 in parallel and parallel byte interface modes.

This pin is the logic input pin in hardware serial mode to enable the cyclic redundancy check (CRC)

word. The signal is latched on the release of a full reset, and requires an additional full RESET to be

reconfigured.

In software mode, this pin must be connected to DGND.

See the DB5/CRCEN (Input/Output) section.

DB6 47 DIO

This pin is the data input/output DB6 in parallel and parallel byte interface modes.

See the DB[7:6] (Input/Output) section.

DB7 48 DIO

This pin is the data input/output DB7 in parallel and parallel byte interface modes.

See the DB[7:6] (Input/Output) section.

DB8 53 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB8 in parallel interface mode.

In serial mode, this pin must be connected to DGND.

See the DB8 (Input/Output) section.

5

ADS8686S

www.ti.com

SBAS905C –NOVEMBER 2019–REVISED JULY 2020

Product Folder Links: ADS8686S

Submit Documentation FeedbackCopyright © 2019–2020, Texas Instruments Incorporated

Pin Functions (continued)

NAME NO. TYPE

(1)

DESCRIPTION

DB9/BYTESEL 54 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB9 in parallel interface mode.

This pin is the logic input pin that enables the parallel byte interface. The signal is latched on the

release of a full RESET, and requires an additional full RESET to be reconfigured.

See the DB9/BYTESEL (Input/Output) section.

DB10/SDI 55 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB10 in parallel interface mode.

This pin is the serial data input that programs the device in software serial mode.

Tie this pin to DGND for parallel byte interface mode.

See the DB10/SDI (Input/Output) section.

DB11/SDOB 56 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB11 in parallel interface mode.

This pin is the serial data output port B in serial interface mode if enabled by the DB4/SER1W pin at full

RESET.

Tie this pin to DGND when in parallel byte interface mode.

See the DB11/SDOB (Input/Output) section.

DB12/SDOA 57 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB12 in parallel interface mode.

This pin is the serial data output port A in serial interface mode.

Tie this pin to DGND when in parallel byte interface mode.

See the DB12/SDOA (Input/Output) section.

DB13/OS0 58 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB13 in parallel interface mode.

This pin is the logic input pin for the oversampling rate (OSR) setting. The signal is latched on the

release of a full RESET, and requires an additional full RESET to be reconfigured.

See the DB13/OS0 (Input/Output) section.

DB14/OS1 59 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB14 in parallel interface mode.

This pin is the logic input pin for the OSR setting. The signal is latched on the release of a full RESET,

and requires an additional full RESET to be reconfigured.

See the DB14/OS1 (Input/Output) section.

DB15/OS2 60 DIO

This pin is a multifunctional logic input/output pin.

This pin is the data input/output DB15 in parallel interface mode.

This pin is the logic input pin for the OSR setting. The signal is latched on the release of a full RESET,

and requires an additional full RESET to be reconfigured.

See the DB15/OS2 (Input/Output) section.

DGND 50 P Digital ground

DVDD 49 P Digital supply pin. Decouple with DGND on pin 50 with a minimum 0.1-µF capacitor.

HW_RNGSEL1,

HW_RNGSEL0

38, 39 DI

Hardware and software mode selection inputs. Hardware and software mode selection is latched at full

reset. In hardware mode, these pins select the input range and are not latched. In software mode,

these pins are latched and ignored until the next RESET event.

HW_RNGSELx = 00: software mode; the ADS8686S is configured via the software registers.

HW_RNGSELx = 01: hardware mode; the analog input range is ±2.5 V.

HW_RNGSELx = 10: hardware mode; the analog input range is ±5 V.

HW_RNGSELx = 11: hardware mode; the analog input range is ±10 V.

See the HW_RANGESEL[1:0] (Input) section.

REFCAP 31 AO

Reference amplifier output pin. This pin must be decoupled to REFGND using a low equivalent series

resistance (ESR), 10-µF ceramic capacitor. Place this capacitor as close to the REFCAP pin as

possible.

Do not drive any external load from this pin.

REFGND 32 P Reference GND. Connect this pin to the AGND plane with the shortest trace possible.

REFIO 33 AIO

This pin acts as an internal reference output when REFSEL is high.

This pin functions as an input pin for the external reference when REFSEL is low.

Decouple this pin with REFIO_GND on pin 34 using a 0.1-µF capacitor.

REFIO_GND 34 P REFIO ground. Connect this pin to the AGND plane with the shortest trace possible.

REFSEL 35 DI

Active high logic input to enable the internal reference.

See the REFSEL (Input) section.

REGCAP 70 P

Voltage output from the internal analog regulator. Decouple this output pin separately to REGGND

using a 10-µF capacitor. Place the capacitor close to the REGCAP pin.

REGCAPD 52 P

Voltage output from the internal digital regulator. Decouple this output pin separately to REGGNDD

using a 10-µF capacitor. Place the capacitor close to the REGCAPD pin.

REGGND 69 P Internal analog regulator GND. Connect this pin to the AGND plane with the shortest trace possible.

REGGNDD 51 P Internal digital regulator GND. Connect this pin to the DGND plane with the shortest trace possible.

RESET 36 DI

Active low logic input to reset the device digital logic. The duration of the RESET pulse decides the

partial or full RESET of the device.

See the RESET (Input) section.

剩余101页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3117

- 资源: 5348

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功