TLK111

www.ti.com

SLLSEF8C –AUGUST 2013–REVISED NOVEMBER 2014

Table of Contents

1 Introduction ............................................... 1 5.4 Auto Negotiation..................................... 33

1.1 Features .............................................. 1 5.5 Link Down Functionality............................. 35

1.2 Applications........................................... 1 5.6 IEEE 1588 Precision Timing Protocol Support...... 36

1.3 Description............................................ 1 6 Reset and Power Down Operation.................. 37

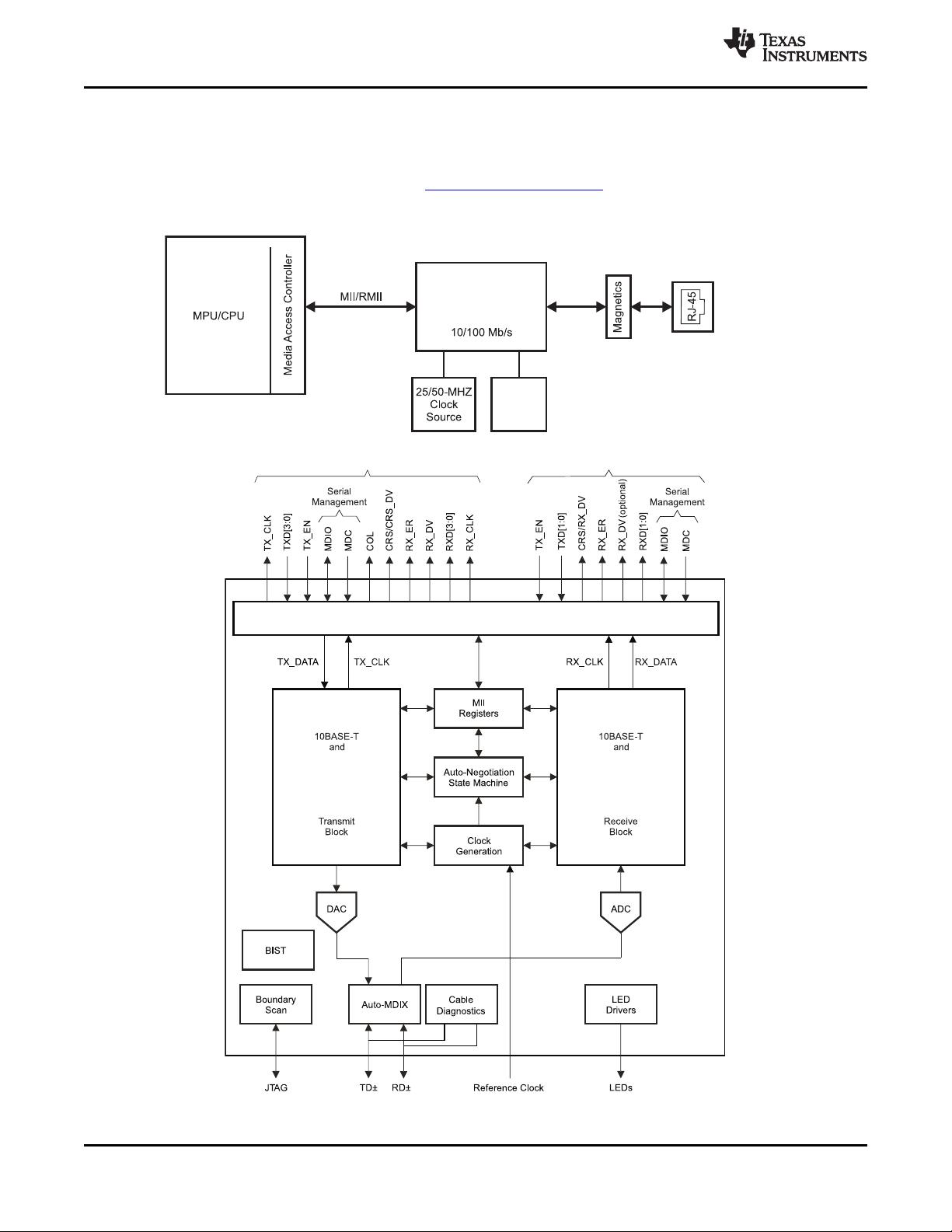

1.4 Functional Block Diagrams ........................... 2 6.1 Hardware Reset..................................... 37

2 Pin Descriptions ......................................... 4 6.2 Software Reset...................................... 37

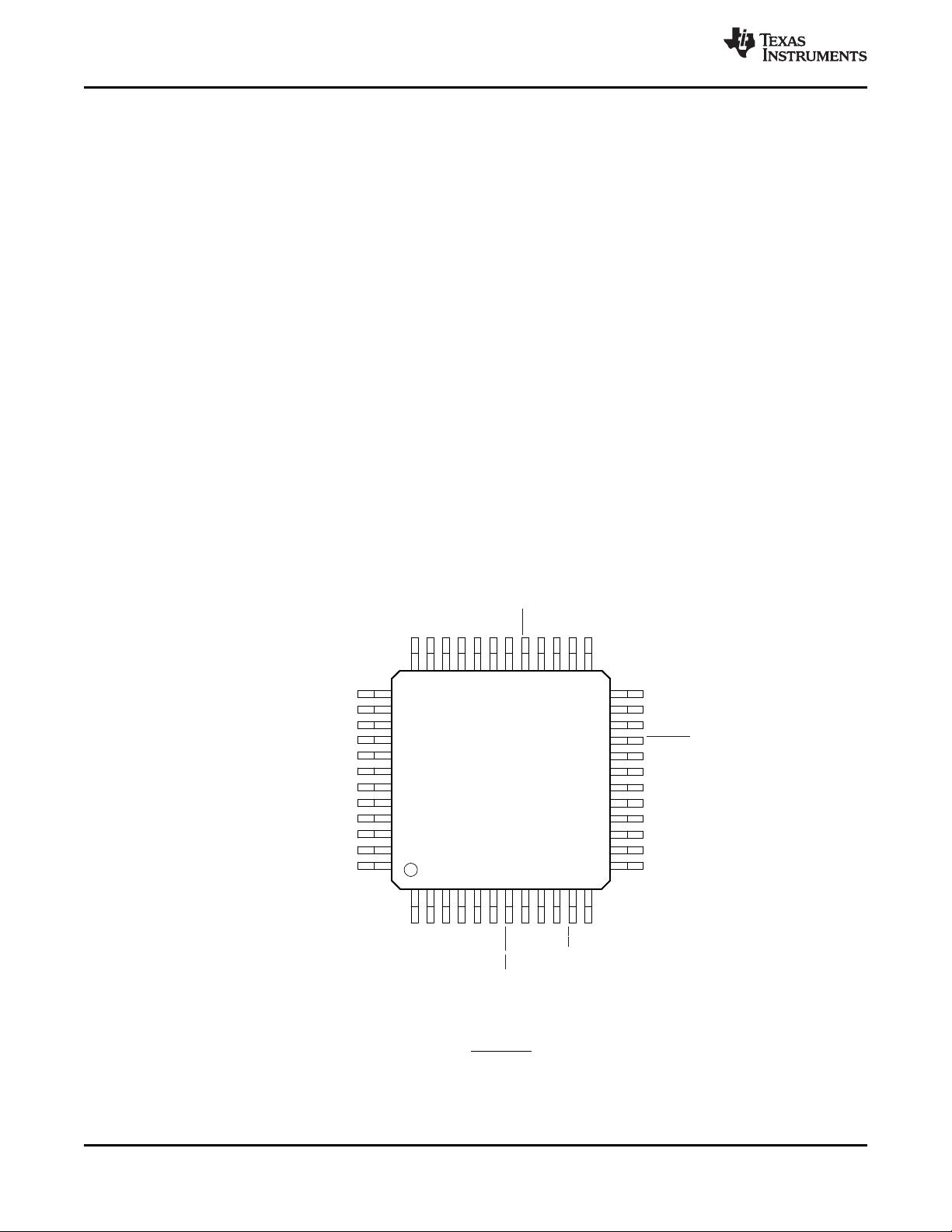

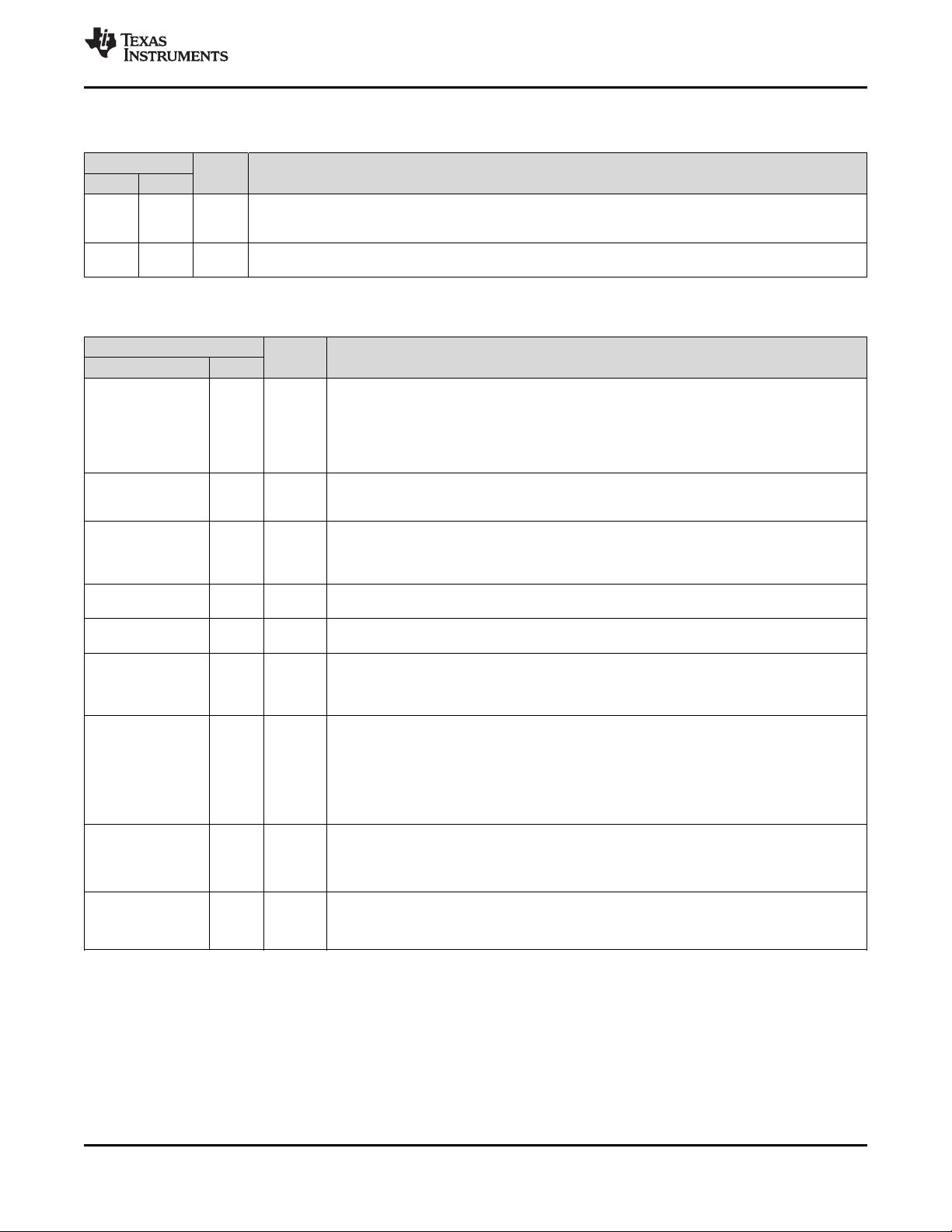

2.1 Pin Layout ............................................ 4 6.3 Power Down/Interrupt ............................... 37

2.2 Serial Management Interface (SMI) .................. 5 6.4 Power Save Modes ................................. 38

2.3 MAC Data Interface .................................. 5 7 Design Guidelines...................................... 39

2.4 10Mbs and 100Mbs PMD Interface .................. 6 7.1 TPI Network Circuit ................................. 39

2.5 Clock Interface ....................................... 6 7.2 Clock In (XI) Requirements ......................... 39

2.6 LED Interface......................................... 6 7.3 Thermal Vias Recommendation .................... 41

2.7 JTAG Interface ....................................... 6 8 Register Block .......................................... 42

2.8 Reset and Power Down .............................. 7 8.1 Register Definition................................... 47

2.9 Power and Bias Connections......................... 7 8.2 Cable Diagnostic Control Register (CDCR)......... 71

3 Hardware Configuration................................ 7 8.3 PHY Reset Control Register (PHYRCR)............ 72

3.1 Bootstrap Configuration .............................. 8 8.4 Multi LED Control register (MLEDCR) .............. 72

3.2 Power Supply Configuration .......................... 9 8.5 IEEE1588 Precision Timing Pin Select (PTPPSEL) 72

8.6 IEEE1588 Precision Timing Configuration

3.3 IO Pins Hi-Z State During Reset .................... 11

(PTPCFG) ........................................... 73

3.4 Auto-Negotiation .................................... 11

8.7 TX_CLK Phase Shift Register (TXCPSR) .......... 73

3.5 Auto-MDIX........................................... 12

8.8 Power Back Off Control Register (PWRBOCR) .... 73

3.6 PHY Address........................................ 12

8.9 Voltage Regulator Control Register (VRCR)........ 74

3.7 MII Isolate Mode .................................... 13

8.10 Cable Diagnostic Configuration/Result Registers ... 74

3.8 Software Strapping Mode ........................... 13

9 Electrical Specifications .............................. 80

3.9 LED Interface ....................................... 15

9.1 Absolute Maximum Ratings ........................ 80

3.10 Multi-Configurable LED (MLED) .................... 16

9.2 Handling Ratings .................................... 80

3.11 Loopback Functionality.............................. 16

9.3 Recommended Operating Conditions .............. 80

3.12 BIST ................................................. 18

9.4 48-Pin Industrial Device Thermal Characteristics... 81

3.13 Cable Diagnostics ................................... 19

9.5 48-Pin Extended Temperature (125°C) Device

4 Interfaces ................................................ 20

Thermal Characteristics............................. 81

4.1 Media Independent Interface (MII) .................. 20

9.6 DC Characteristics, VDD_IO ....................... 81

4.2 Reduced Media Independent Interface (RMII)...... 20

9.7 DC Characteristics ................................. 81

4.3 Serial Management Interface ....................... 23

9.8 Power Supply Characteristics ....................... 82

5 Architecture ............................................. 27

9.9 AC Specifications.................................... 83

5.1 100Base-TX Transmit Path ......................... 27

10 Revision History, Revision A ........................ 98

5.2 100Base-TX Receive Path ......................... 30

11 Revision History, Revision B ........................ 98

5.3 10Base-T Receive Path ............................. 32

12 Revision History, Revision C ........................ 98

Copyright © 2013–2014, Texas Instruments Incorporated Table of Contents 3

Submit Documentation Feedback

Product Folder Links: TLK111

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功