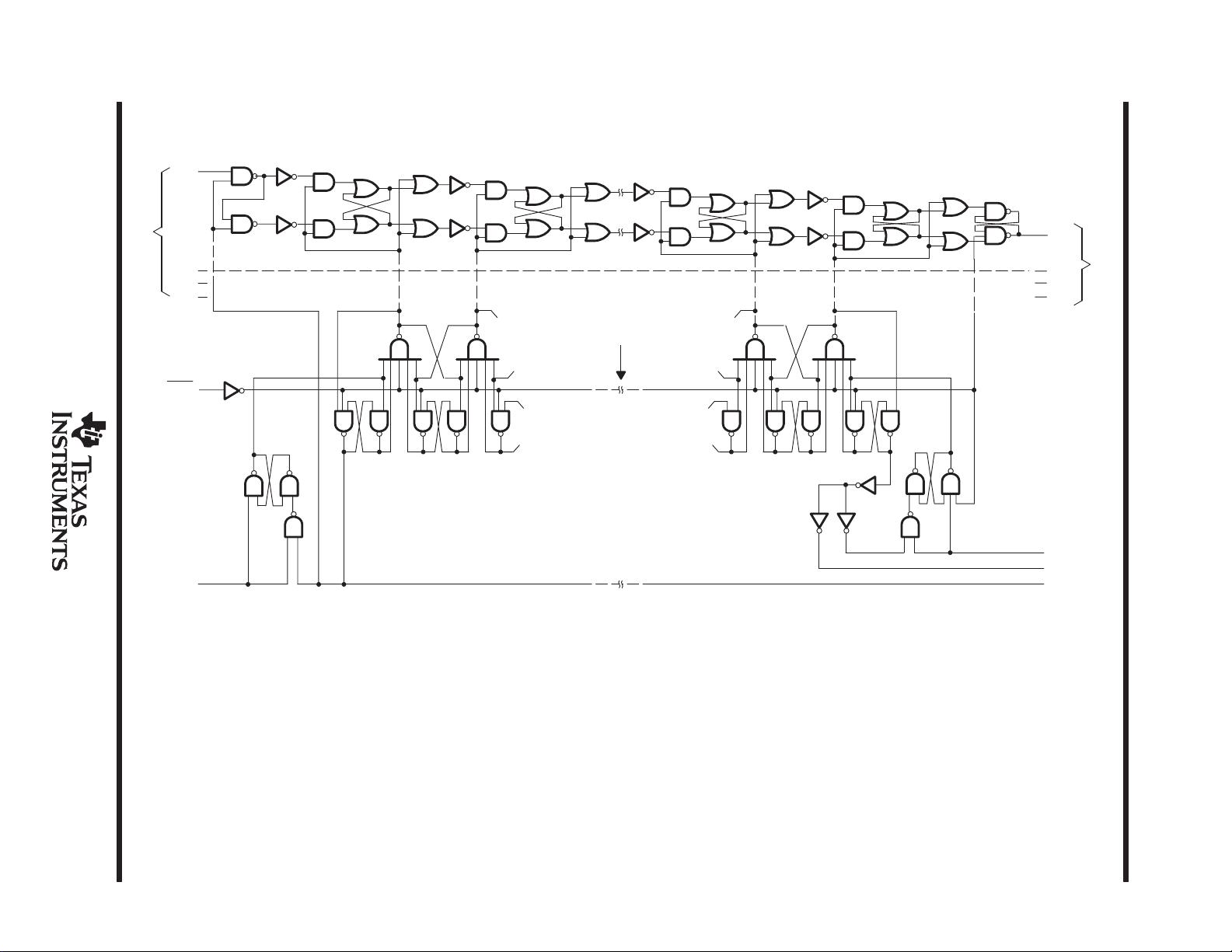

【TI-SN74ALS236.pdf】文档所描述的是TI公司的一款名为SN74ALS236的异步先进低功耗肖特基(IMPACT)技术的64位×4位首先进出(FIFO)存储器。这款芯片具有高速度和快速下降时间的特点,特别适用于需要高速数据处理的系统。 SN74ALS236的核心功能是其FIFO内存结构,这种存储设备允许数据以独立的写入和读取速率进入和离开数组。FIFO内存的工作原理是先进入的数据先被读出。数据通过上升沿触发的移位输入(SI)写入内存,当SI信号变为低电平时,第一个数据字会依次从输出端口输出(如图1所示)。随着FIFO逐渐填满,数据字按照写入的顺序堆积。当FIFO满载时,额外的移位输入脉冲不再影响内存。数据则在移位输出(SO)输入的下降沿被逐位移出内存(如图2所示)。当FIFO为空时,额外的移位输出脉冲无效,最后一个数据字将保留在输出端,直到新的数据移入或复位(RST)信号变为低电平。 SN74ALS236的运行状态可以通过两个标志位来监控:输出准备好(OR)和输入准备好(IR)。当OR为高电平时,表示输出端有有效数据;当SO为高且FIFO为空时,OR保持低电平。IR为高表示输入端准备接收更多数据;当SI为高且FIFO满载时,IR保持低电平。 在FIFO空载的情况下,如果SI变为低电平,输入数据会自动移动到输出端。如果在此期间保持SO为高,OR标志会短暂变为高电平,表明输出端有有效数据(如图3所示)。当FIFO满载时,通过保持SI高电平并使SO变为低电平,数据会被自动移入内存。而此时,若RST信号变为低电平,会清空整个FIFO内存。 此外,SN74ALS236提供了3态输出,这意味着输出可以在高阻态、高电平和低电平之间切换,以适应不同系统的需要。它还提供了多种封装选项,包括塑料小型轮廓封装(DW)、塑料J引脚芯片载体(FN)以及标准的300密尔双列直插封装(N),以满足不同应用场景的需求。 这款芯片设计用于处理最高达30MHz的数据速率,使其在需要高速数据传输的系统中表现出色,比如计算机接口、通信设备和数字信号处理等应用。其低功耗特性使得SN74ALS236在保持高性能的同时,降低了系统整体的能耗。通过有效的数据管理和状态监控,SN74ALS236能够在各种实时数据处理任务中提供高效可靠的存储解决方案。

剩余10页未读,继续阅读

- 粉丝: 7135

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 魔术公式轮胎建模的MATLAB GUI.zip

- 曲面边界的格子玻尔兹曼方法的MATLAB实现.zip

- 谱狮子SPM是一个MATLAB代码,它使用谱数值方法求解所谓的锂离子电池单粒子模型SPM.zip

- 脑机接口BCI的MATLAB工具箱.zip

- 三车道交通流元胞自动机matlab实现.zip

- 上海交通大学MTALAB代码中数据融合过程的求解.zip

- 全景图像拼接的MATLAB代码.zip

- 深度高斯过程的matlab.zip

- 机械臂GUI工具箱基于matlab robotics toolbox.zip

- 基本遗传算法MATLAB程序.zip

- 基本光度立体算法的MATLAB实现.zip

- Unity 导出terrian Nav信息供服务使用,或者自己开发需要

- 基于cnn的机翼损失人脸地标定位的Matlab实现.zip

- 基于MATLAB R2016a的二维和三维环境下无人机路径规划问题.zip

- 基于gpuArray的轻量级MATLAB深度学习工具箱.zip

- 基于delaunay的非结构化网格生成器JIGSAW的MATLAB绑定.zip

信息提交成功

信息提交成功