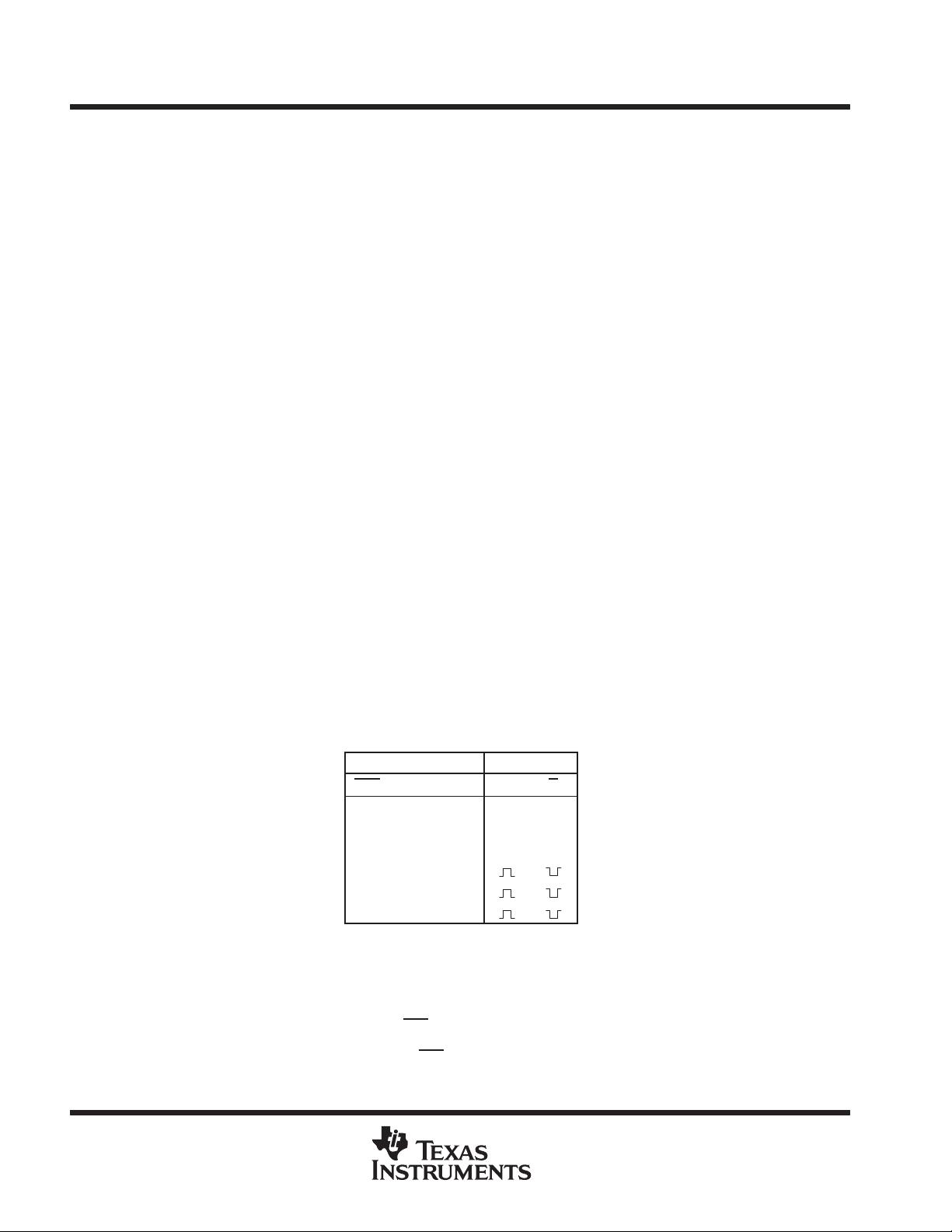

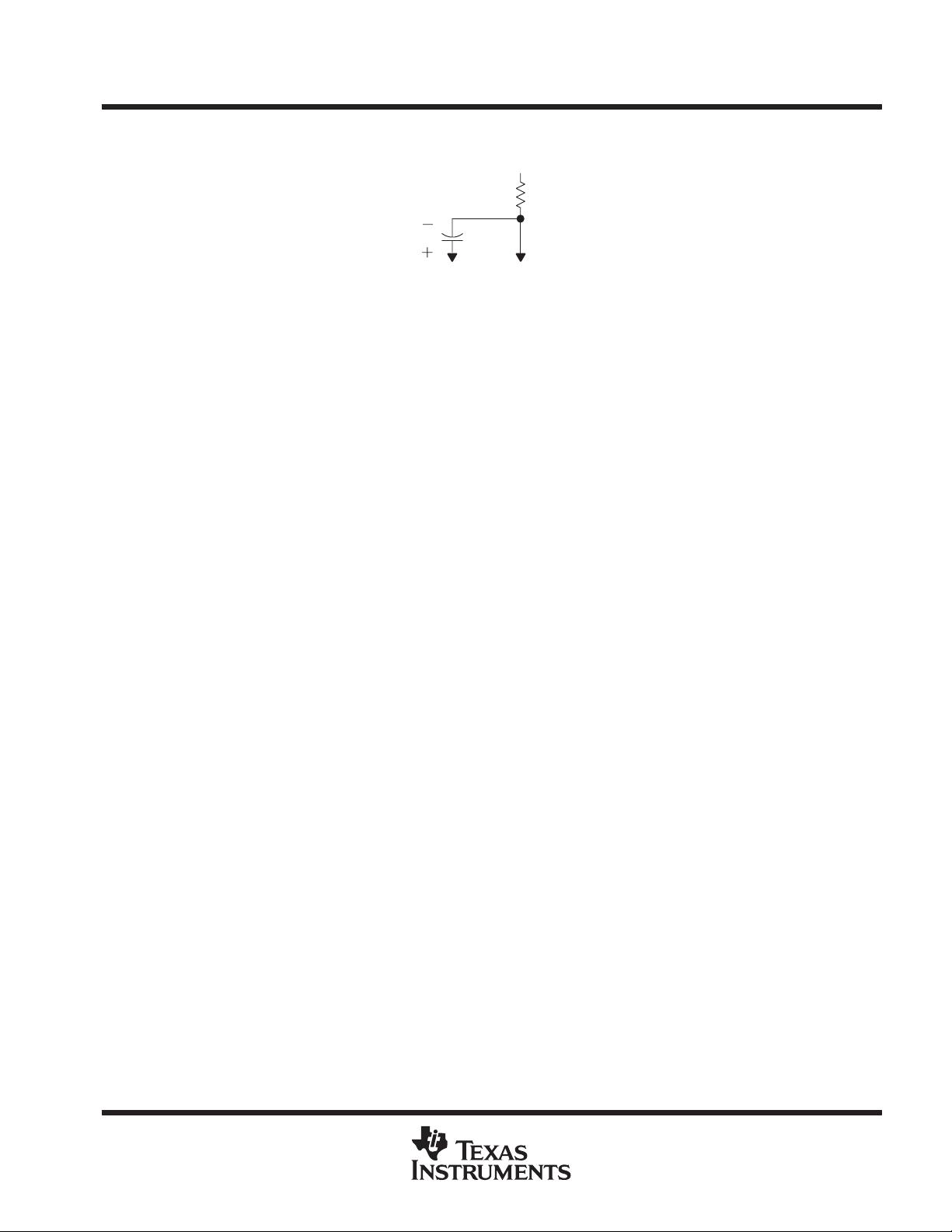

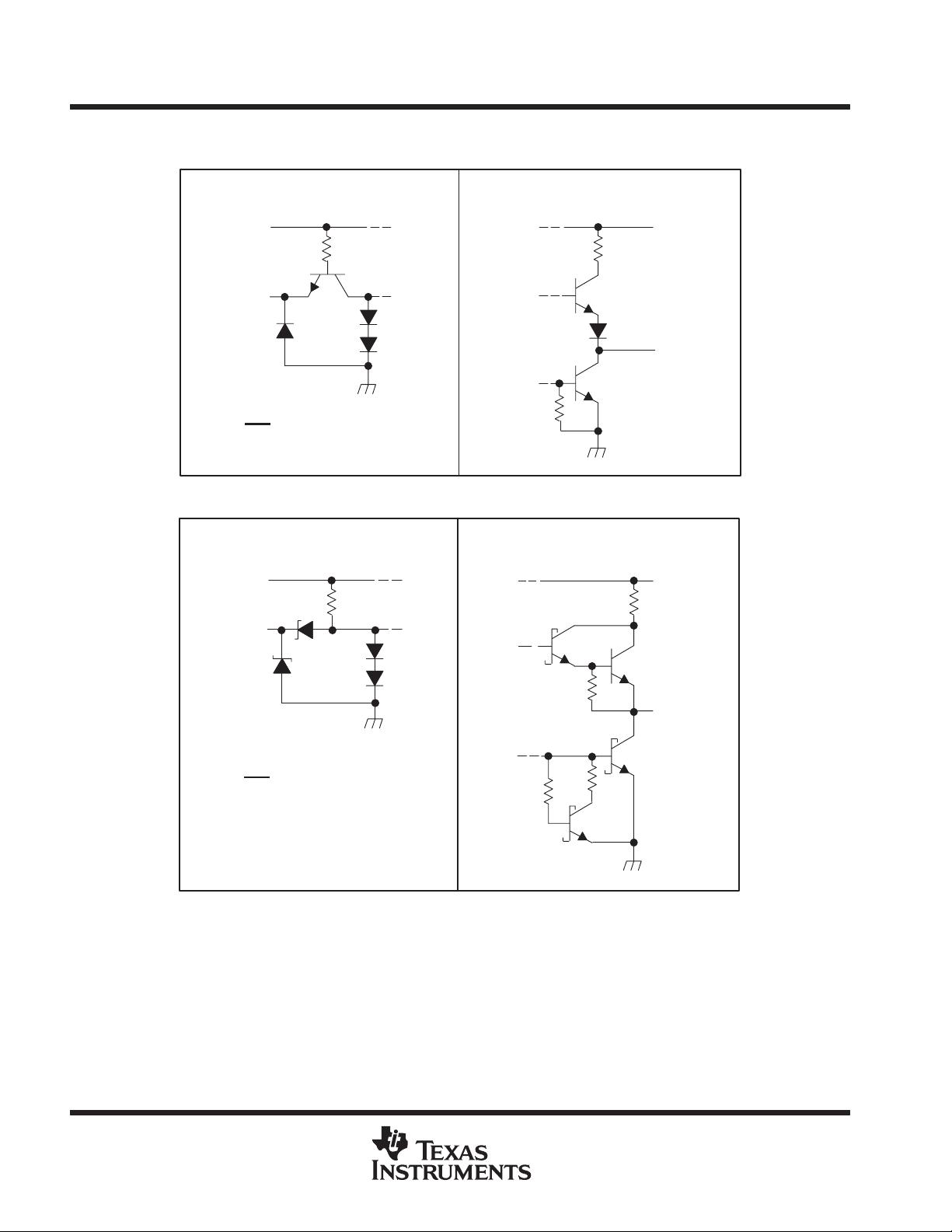

TI-SN74LS221是一款由德州仪器(TI)生产的双稳态多谐振荡器集成电路。这款芯片的设计特点在于其性能几乎与SN54121和SN74121单稳态触发器一致,同时具有相同的引脚配置,与SN54123、SN74123、SN54LS123和SN74LS123的引脚布局相同,便于在设计电路时进行替换。 该芯片提供了两种版本:SN54221和SN74221。这两个版本的电气特性和开关特性几乎完全相同,都具备负边沿触发输入和正边沿触发输入,且任一输入可作为抑制输入。这意味着它们可以在相同的触发条件下产生稳定的脉冲输出。 SN54221和SN74221的最大输出脉冲长度不同,SN54221的最长输出脉冲为21秒,而SN74221的最长输出脉冲为28秒。对于SN54LS221和SN74LS221,其最大输出脉冲长度分别是49秒和70秒。这种差异主要源于不同系列在工作电压、功耗以及温度范围上的微小差别。 在封装方面,TI-SN74LS221提供多种选择,包括PDIP(塑料双列直插式封装)、SOIC(小外形集成电路封装)、SOP(小外形封装)以及SSOP(薄型小外形封装)。此外,还有适用于极端温度范围的J封装和FK封装。每种封装都有对应的订单型号,例如PDIP封装的N系列芯片标记为SN74LS221N,而DIP封装的J系列芯片则标记为SNJ54LS221J。 在应用中,SN74LS221常用于需要精确控制时序信号的场合,例如定时器、脉冲发生器或信号整形电路。每个独立的多谐振荡器单元(Q1和Q2)都可以单独控制,通过外部电容Cext和电阻Rext/Cext可以设置脉冲宽度。同时,通过CLR输入可以强制终止输出脉冲,实现对输出的即时复位。 总体来说,TI-SN74LS221是一款高度稳定、灵活且兼容性强的双稳态多谐振荡器,适用于各种需要精确时序控制的电子系统设计。其详细的技术参数、封装信息、电气特性以及PCB设计指南等资料可在德州仪器的官方网站上找到。

剩余26页未读,继续阅读

- 粉丝: 7270

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 西门子S7-200PLC程序和MCGS3层电梯三层电梯带组态仿真组态设计PLC设计

- 二维谷光子晶体拓扑激光器

- Matlab Simulink变压器饱和模型 励磁涌流模型 变压器具备饱和特性和磁滞特性,可以仿真剩磁,饱和磁通等特性 励磁涌流结果见图2 磁滞特性见图3 剩磁见图4 图6为自己封装的变压器参数转模块

- VCU控制软件simulink模型 控制模块包括:挡位管理、上下电、能量管理、扭矩管理等功能 可用于学习开发控制策略学习 模型附有详细的说明文档 模型有三处变量未赋值的报错但整体逻辑没有错误,可以自己

- 四旋翼飞行器编队避险飞行matlab仿真 附带参考文件

- Simulink直升机非线性动力学模型,直升机动力学仿真,MATLAB Simulink版本,黑鹰单旋翼直升机气动模型,包含源码 有两篇说明文献和使用说明

- STATCOM 级联H桥 5电平 simulink仿真

- FPGA SDI 视频解码PCIE传输 FPGA实现SDI视频解码PCIE传输 提供工程源码和QT上位机源码加 开发板FPGA型号:Xilinx–xc7k325tffg900-2; 开发环境:Viva

- 构网型逆变器控制,同步发电机VSG仿真simulink matlab模型一次调频 一次调频、阻抗、无功电压补偿等

- 增强型地热开采EGS 地热开采 基于COMSOL热流固耦合的地热开采、回灌模型,考虑天然裂缝引起的窜流,可分析不同注采条件下的压力及温度分布

- comsol 电流 电场 磁场 固体传热 流体传热 热流固耦合 地热抽取 裂隙流 传热传质 多孔介质 两项流

- PMSM电机的转速控制Simulink模型 PMSM电机的全状态参数观测 主要包括内容: 1)基于PID的PMSM电机转速控制模型; 2)基于滑模控制器(SMC)的PMSM电机转速控制模型; 3)PM

- 电池控制模型 充放电策略 BMS SOC 傅里叶分析 附赠详细注释和运行说明 BMS管理模型 包含SOC控制策略 电池充放电控制策略 电池参数状态电流峰值电压及SOC监控 含运行界面可以对仿真参数进行

- 两级式单相光伏并网仿真(注意版本matlab 2021a) 前级采用DC-DC变电路,通过MPPT控制DC-DC电路的pwm波来实现最大功率跟踪,mppt采用扰动观察法,后级采用桥式逆变,用spwm波

- 三相桥式(两电平)闭环并网仿真 拓扑:两电平逆变器 DC:800V AC:380V 控制:电流内环PI与前馈解耦 滤波器:LCL滤波器 调制:SPWM 功率等级:100kW THD<1% 结果: 电压

- 风储联合系统 直驱风机加储能系统

信息提交成功

信息提交成功