没有合适的资源?快使用搜索试试~ 我知道了~

TI-TLV5580.pdf

需积分: 10 0 下载量 93 浏览量

2022-11-27

16:19:29

上传

评论 4

收藏 536KB PDF 举报

温馨提示

试读

38页

TI-TLV5580.pdf

资源推荐

资源详情

资源评论

SLAS205B − DECEMBER 1998 − REVISED OCTOBER 2003

www.ti.com

D 8-Bit Resolution 80 MSPS Sampling

Analog-to-Digital Converter (ADC)

D Low Power Consumption: 165 mW Typ

Using External references

D Wide Analog Input Bandwidth: 700 MHz Typ

D 3.3 V Single-Supply Operation

D 3.3 V TTL/CMOS-Compatible Digital I/O

D Internal Bottom and Top Reference Voltages

D Adjustable Reference Input Range

D Power Down (Standby) Mode

D Separate Power Down for Internal Voltage

References

D Three-State Outputs

D 28-Pin Small Outline IC (SOIC) and Thin

Shrink SOP (TSSOP) Packages

D Applications

− Digital Communications

− Flat Panel Displays

− High-Speed DSP Front-End

(TMS320C6000)

− Medical Imaging

− Graphics Processing (Scan Rate/Format

Conversion)

− DVD Read Channel Digitization

DESCRIPTION

The TLV5580 is an 8-bit 80 MSPS high-speed A/D

converter. It converts the analog input signal into

8-bit binary-coded digital words up to a sampling

rate of 80 MHz. All digital inputs and outputs are

3.3 V TTL/CMOS-compatible.

The device consumes very little power due to the

3.3 V supply and an innovative single-pipeline

architecture implemented in a CMOS process.

The user obtains maximum flexibility by setting

both bottom and top voltage references from

user-supplied voltages. If no external references

are available, on-chip references are available for

internal and external use. The full-scale range is

1 Vpp up to 1.6 Vpp, depending on the analog

supply voltage. If external references are

available, the internal references can be disabled

independently from the rest of the chip, resulting

in an even greater power saving.

While usable in a wide variety of applications, the

device is specifically suited for the digitizing of

high-speed graphics and for interfacing to LCD

panels or LCD/DMD projection modules . Other

applications include DVD read channel

digitization, medical imaging and

communications. This device is suitable for IF

sampling of communication systems using

sub-Nyquist sampling methods because of its

high analog input bandwidth.

! "#$ ! %#&'" ($) (#"!

" !%$""! %$ *$ $! $+! !#$! !(( ,-)

(#" %"$!!. ($! $"$!!'- "'#($ $!. '' %$$!)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

1

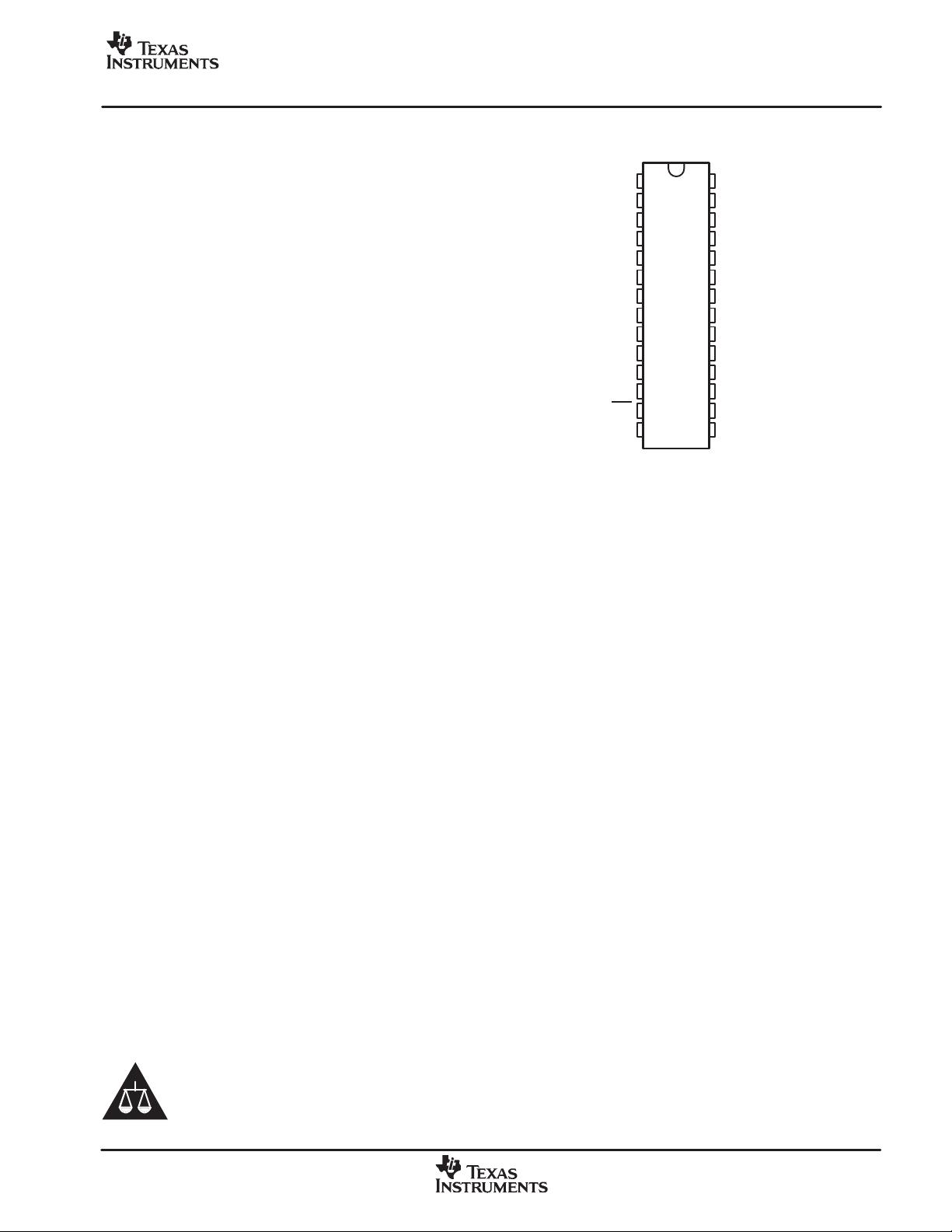

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

DRV

DD

D0

D1

D2

D3

D4

D5

D6

D7

DRV

SS

DV

SS

CLK

OE

DV

DD

AV

SS

AV

DD

AIN

CML

PWDN_REF

AV

SS

REFBO

REFBI

REFTI

REFTO

AV

SS

BG

AV

DD

STBY

DW OR PW PACKAGE

(TOP VIEW)

Copyright 1999−2003, Texas Instruments Incorporated

www.ti.com

SLAS205B − DECEMBER 1998 − REVISED OCTOBER 2003

www.ti.com

2

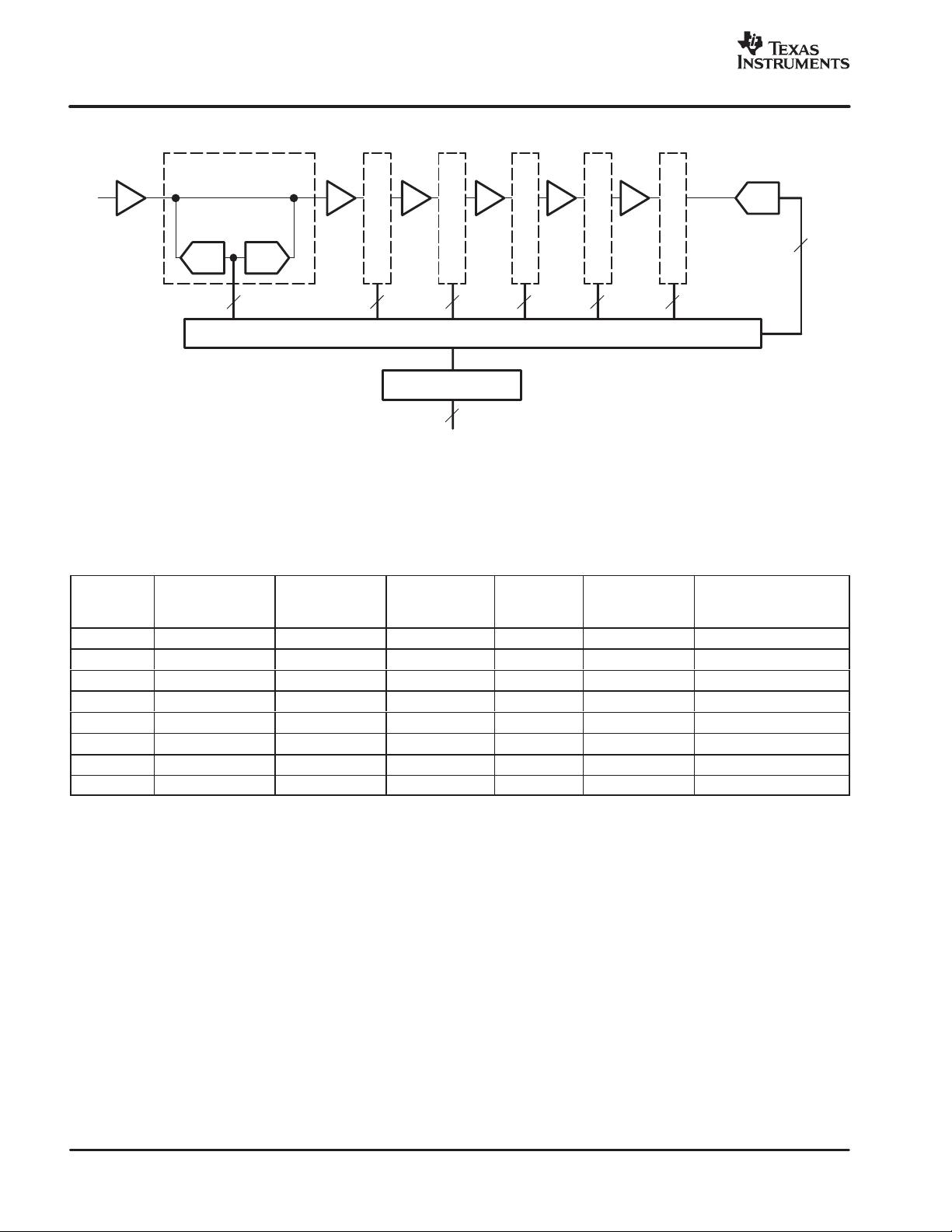

FUNCTIONAL BLOCK DIAGRAM

SHA

DACADC

+

−

ADC

Correction Logic

Output Buffers

2222 2

D0(LSB)−D7(MSB)

2

2

SHA SHA SHA SHA SHA

The single-pipeline architecture uses 6 ADC/DAC stages and one final flash ADC. Each stage produces a

resolution of 2 bits. The correction logic generates its result using the 2-bit result from the first stage, 1 bit from

each of the 5 succeeding stages, and 1 bit from the final stage in order to arrive at an 8-bit result. The correction

logic ensures no missing codes over the full operating temperature range.

PACKAGE/ORDERING INFORMATION

PRODUCT PACKAGE−LEAD

PACKAGE

DESIGNATOR

(1)

SPECIFIED

TEMPERATURE

RANGE

PACKAGE

MARKING

ORDERING

NUMBER

TRANSPORT MEDIA,

QUANTITY

TLV5580 SOIC, 28 DW 0°C to +70°C TLV5580C TLV5580CDW Rails, 20

″ ″ ″ ″ ″ TLV5580CDWR Tape and Reel, 1000

TLV5580 TSSOP. 28 PW 0°C to +70°C TV5580 TLV5580CPW Rails, 20

″ ″ ″ ″ ″ TLV5580CPWR Tape and Reel, 2000

TLV5580 SOIC, 28 DW −40°C to +85°C TLV5580I TLV5580IDW Rails, 50

″ ″ ″ ″ ″ TLV5580IDWR Tape and Reel, 1000

TLV5580 TSSOP, 28 PW −40°C to +85°C TY5580 TLV5580IPW Rails, 50

″ ″ ″ ″ ″ TLV5580IPWR Tape and Reel, 2000

(1)

For the most current specifications and package information, refer to our web site at www.ti.com.

SLAS205B − DECEMBER 1998 − REVISED OCTOBER 2003

www.ti.com

3

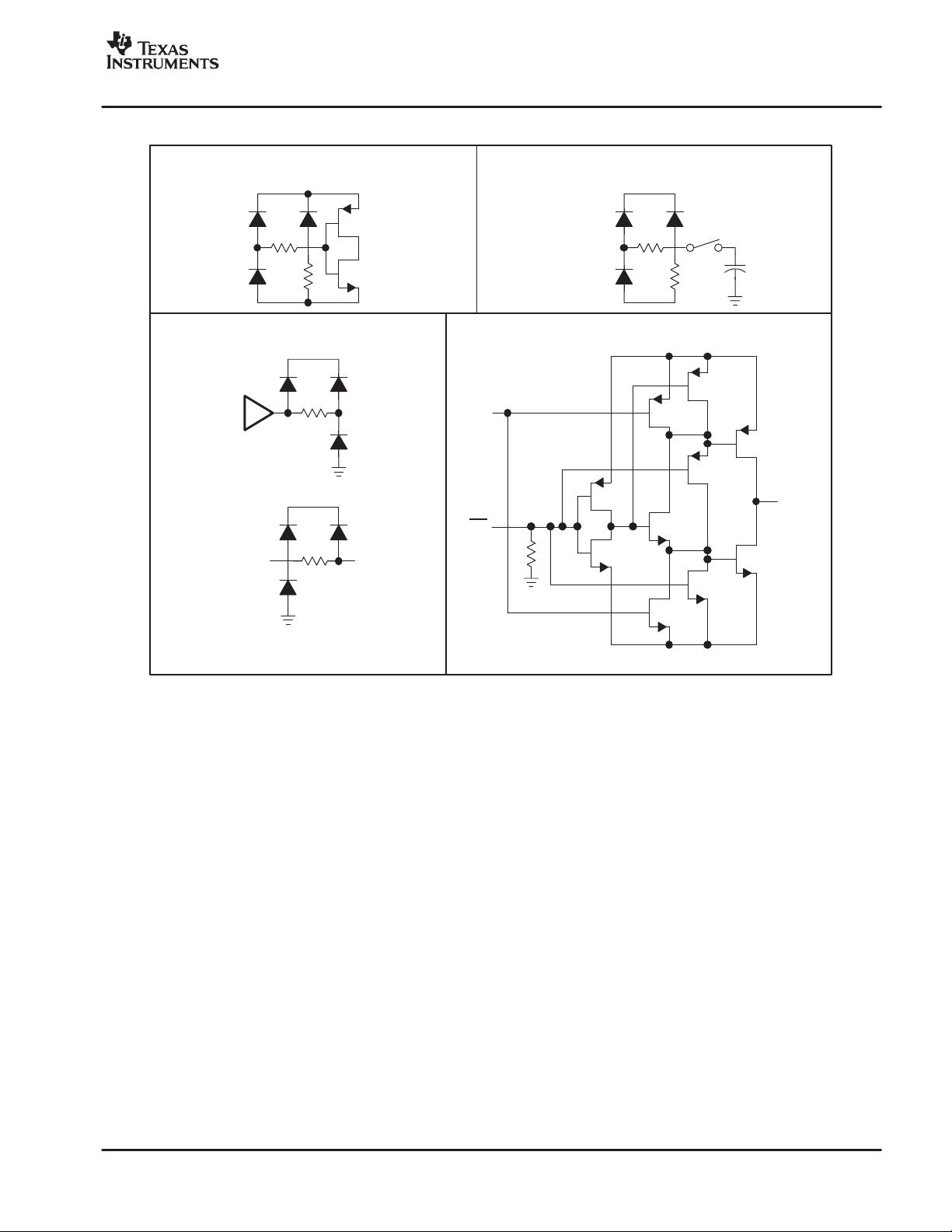

CIRCUIT DIAGRAMS OF INPUTS AND OUTPUTS

DV

DD

AV

DD

AV

DD

0.5 pF

Internal

Reference

Generator

REFTO

or

REFBO

AV

DD

REFBI

or

REFTI

OE

ALL DIGITAL INPUT CIRCUITS AIN INPUT CIRCUIT

REFERENCE INPUT CIRCUIT D0−D7 OUTPUT CIRCUIT

DRV

DD

DRV

SS

D_Out

D

SLAS205B − DECEMBER 1998 − REVISED OCTOBER 2003

www.ti.com

4

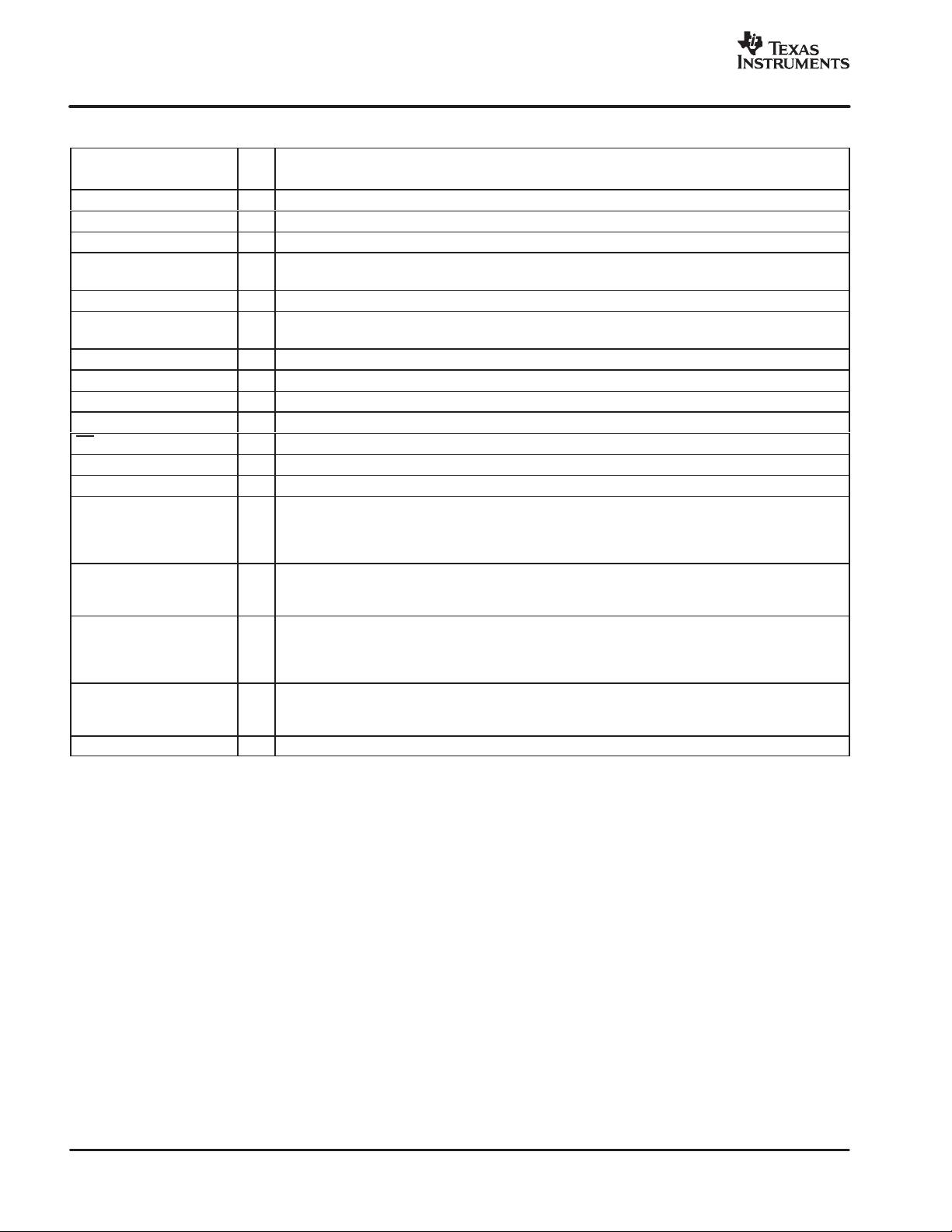

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME NO.

I/O

DESCRIPTION

AIN 26 I Analog input

AV

DD

16, 27 I Analog supply voltage

AV

SS

18, 23, 28 I Analog ground

BG 17 O Band gap reference voltage. A 1 µF capacitor (with an optional 0.1 µF capacitor in parallel) should be

connected between this terminal and AV

SS

for external filtering.

CLK 12 I Clock input. The input is sampled on each rising edge of CLK.

CML 25 O Common mode level. This voltage is equal to (AV

DD

− AV

SS

) ÷ 2. An external 0.1 µF capacitor should be

connected between this terminal and AV

SS

.

D0 − D7 2 − 9 O Data outputs. D7 is the MSB

DRV

DD

1 I Supply voltage for digital output drivers

DRV

SS

10 I Ground for digital output drivers

DV

DD

14 I Digital supply voltage

OE 13 I Output enable. When high the D0 − D7 outputs go in high-impedance mode.

DV

SS

11 I Digital ground

PWDN_REF 24 I Power down for internal reference voltages. A high on this terminal will disable the internal reference circuit.

REFBI 21 I Reference voltage bottom input. The voltage at this terminal defines the bottom reference voltage for the

ADC. It can be connected to REFBO or to an externally generated reference level. Sufficient filtering should

be applied to this input. The use a 0.1 µF capacitor connected between REFBI and AV

SS

is recommended.

Additionally, a 0.1 µF capacitor can be connected between REFTI and REFBI.

REFBO 22 O Reference voltage bottom output. An internally generated reference is available at this terminal. It can be

connected to REFBI or left unconnected. A 1 µF capacitor between REFBO and AV

SS

will provide sufficient

decoupling required for this output.

REFTI 20 I Reference voltage top input. The voltage at this terminal defines the top reference voltage for the ADC. It

can be connected to REFTO or to an externally generated reference level. Sufficient filtering should be

applied to this input. The use of a 0.1 µF capacitor between REFTI and AV

SS

is recommended. Additionally,

a 0.1 µF capacitor can be connected between REFTI and REFBI.

REFTO 19 O Reference voltage top output. An internally generated reference is available at this terminal. It can be

connected to REFTI or left unconnected. A 1 µF capacitor between REFTO and AV

SS

will provide sufficient

decoupling required for this output.

STBY 15 I Standby input. A high level on this input enables a power-down mode.

SLAS205B − DECEMBER 1998 − REVISED OCTOBER 2003

www.ti.com

5

ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE-AIR TEMPERATURE (unless

otherwise noted)

†

Supply voltage: AV

DD

to AGND, DV

DD

to DGND −0.5 V to 4.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply voltage: AV

DD

to DV

DD

, AGND to DGND −0.5 V to 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital input voltage range to DGND −0.5 V to DV

DD

+ 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Analog input voltage range to AGND −0.5 V to AV

DD

+ 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital output voltage applied from external source to DGND −0.5 V to DV

DD

+ 0.5 V. . . . . . . . . . . . . . . . . . .

Reference voltage input range to AGND: V

(REFTI)

, V

(REFTO)

, V

(REFBI)

, V

(REFBO)

−0.5 V to AV

DD

+ 0.5 V

Operating free-air temperature range, T

A

: TLV5580C 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TLV5580I −40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

−55°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(1) †

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

RECOMMENDED OPERATING CONDITIONS OVER OPERATING FREE-TEMPERATURE RANGE

POWER SUPPLY

MIN NOM MAX UNIT

AV

DD

Supply voltage DV

DD

3 3.

3

3.

6

V

Supply voltage

DRV

DD

3

3.3

3.6

V

ANALOG AND REFERENCE INPUTS

MIN NOM MAX UNIT

Reference input voltage (top), V

(REFTI)

(NOM) − 0.2 2 + (AV

DD

− 3) (NOM) + 0.2 V

Reference input voltage (bottom), V

(REFBI)

0.8 1 1.2 V

Reference voltage differential, V

(REFTI)

− V

(REFBI)

1 + (AV

DD

− 3) V

Analog input voltage, V

(AIN)

V

(REFBI)

V

(REFTI)

V

DIGITAL INPUTS

MIN NOM MAX UNIT

High-level input voltage, V

IH

2.0 DV

DD

V

Low-level input voltage, V

IL

DGND 0.2xDV

DD

V

Clock period, t

c

12.5 ns

Pulse duration, clock high, t

w(CLKH)

5.25 ns

Pulse duration, clock low, t

w(CLKL)

5.25 ns

剩余37页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3117

- 资源: 5348

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功