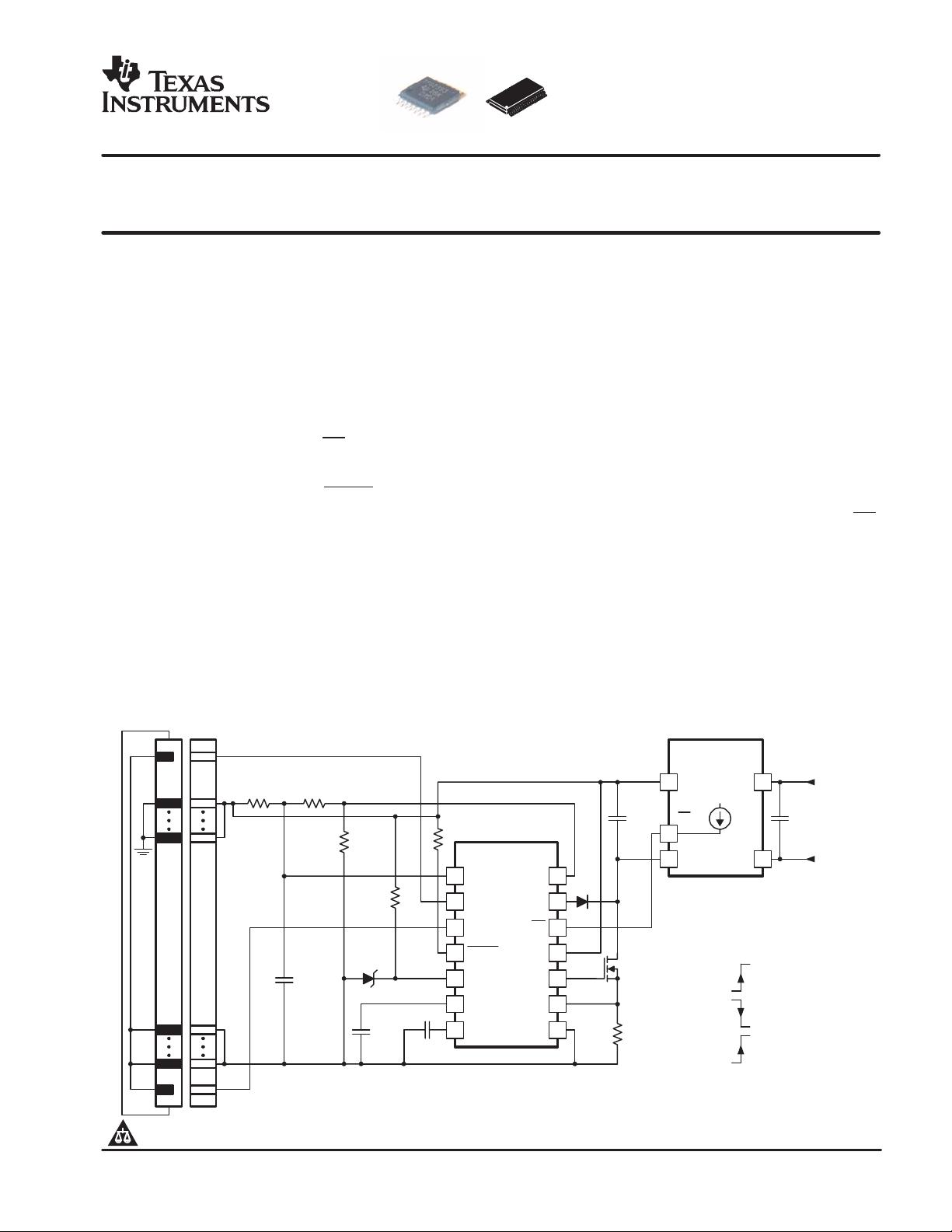

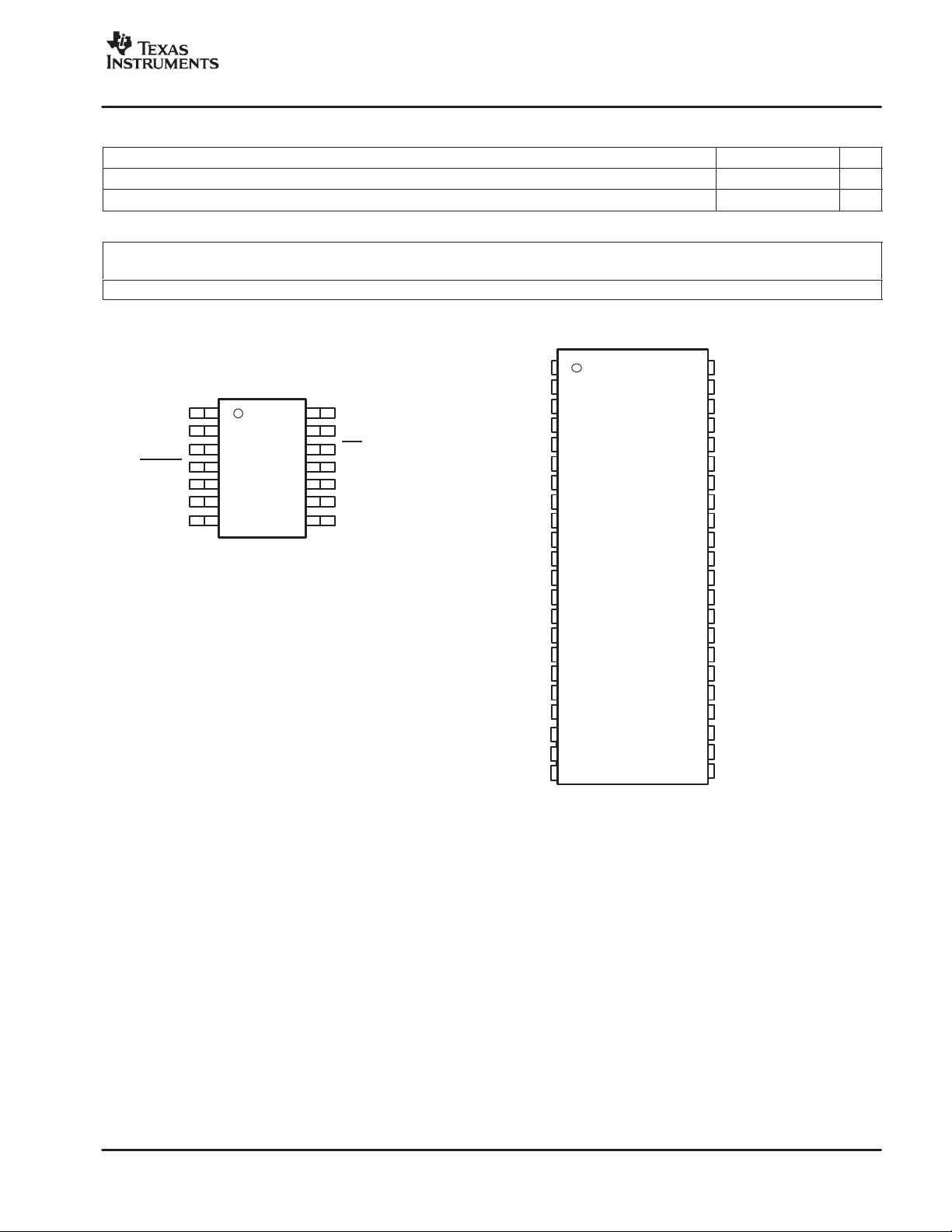

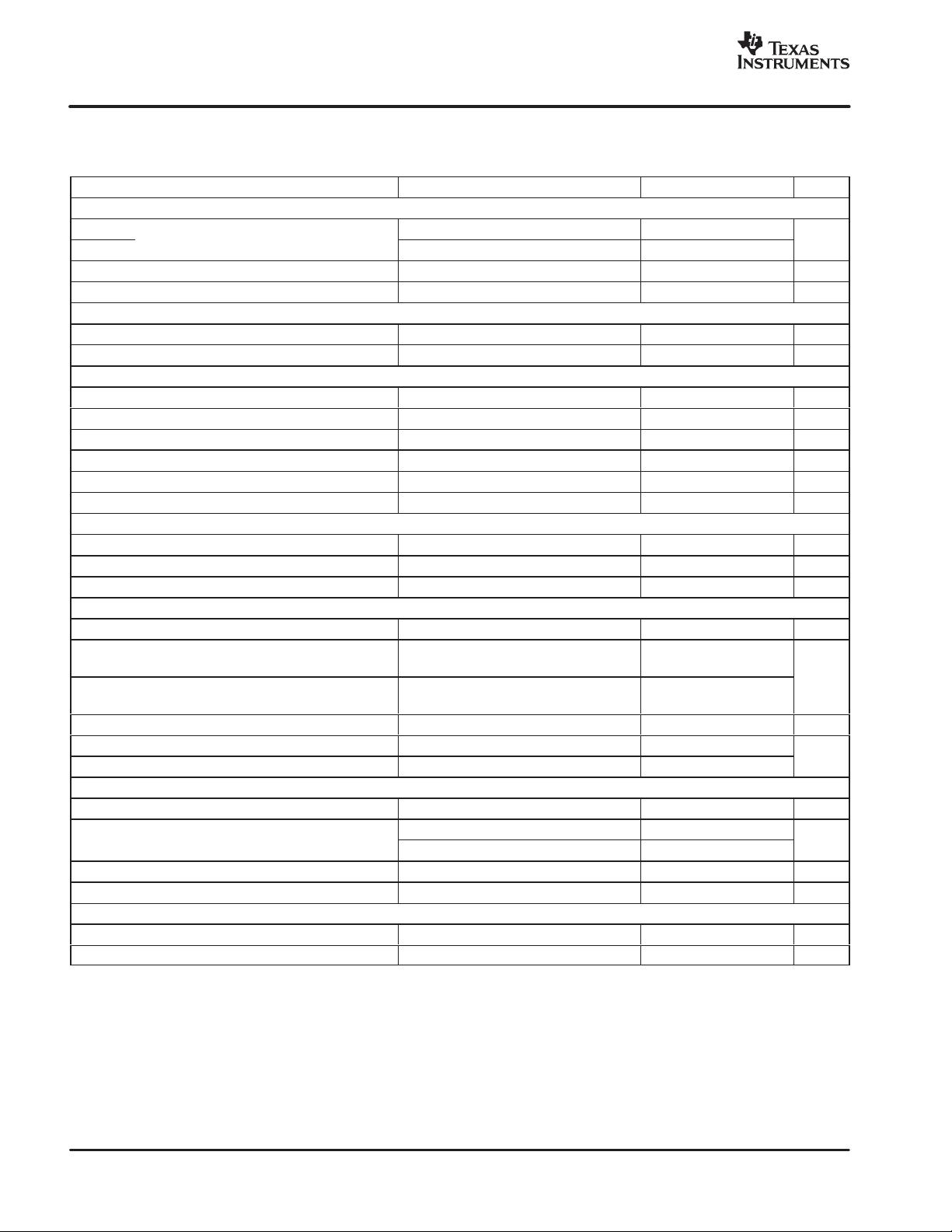

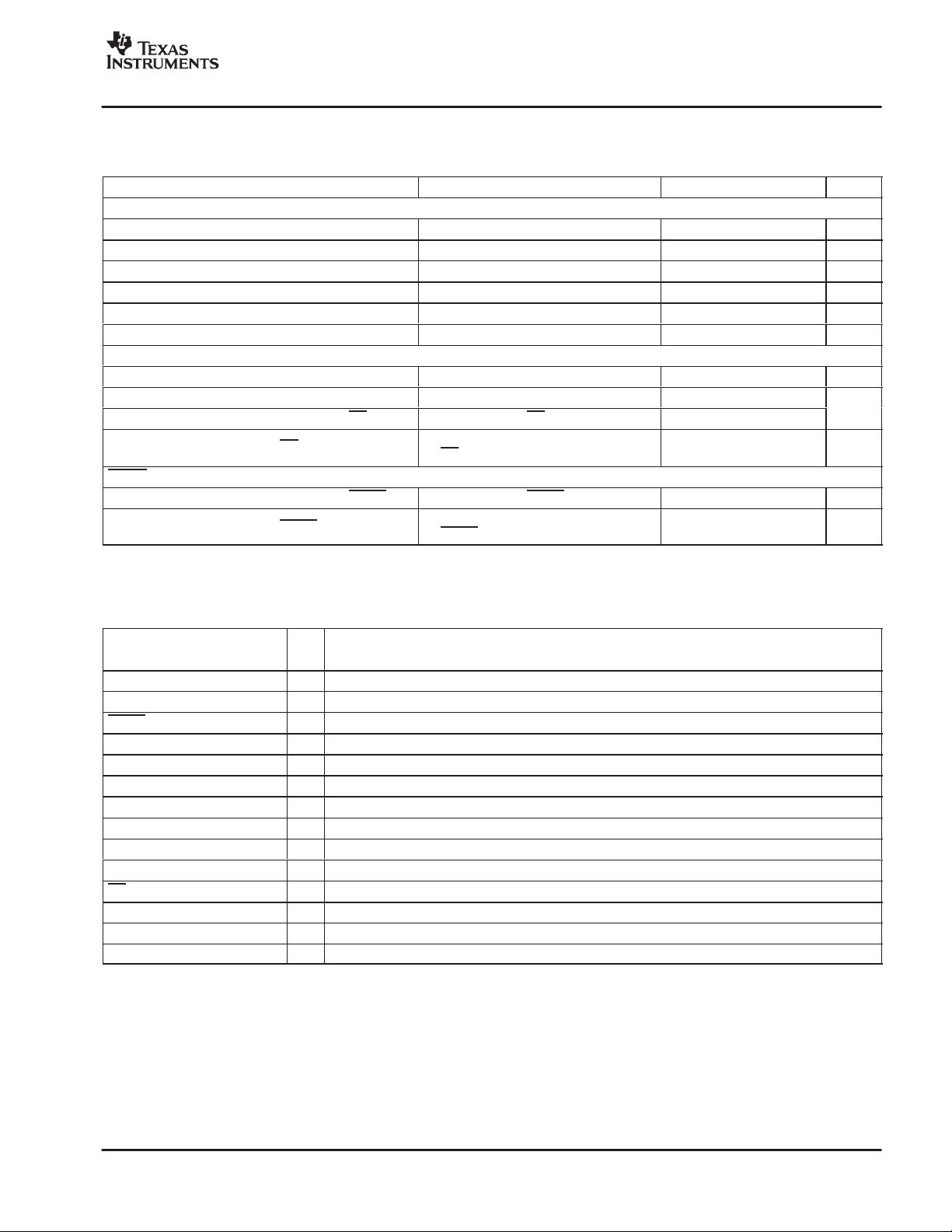

随着现代通信技术的迅速发展,电信中央交换机和无线基站等关键基础设施对于电源系统的可靠性、稳定性和安全性提出了更高的要求。为了满足这些需求,美国德州仪器(Texas Instruments,简称TI)推出了TPS2392热插拔电源管理集成电路,为这些应用提供了专业的解决方案。 TPS2392是一款专为-48伏分布式电源系统设计的集成电路,能够处理-20伏至-80伏的宽输入电源范围,并且具备承受-100伏瞬态电压的能力。这款芯片的设计初衷是为了在电信设备的安装和维护过程中,能够实现安全的热插拔操作。这意味着在系统带电运行的情况下,可以随时插入或移除电源卡或模块,而不会对整体系统造成损害。 TPS2392的功能非常丰富,它具备可编程电流限制、可编程电流上升速率控制以及可编程的欠压/过压阈值和滞后等特性。这些功能使得用户可以根据实际应用需求,对电路的行为进行精细调控,确保在各种异常情况下电路均能保持在安全工作状态。 为了实现热插拔功能,TPS2392通过外部的N沟道场效应晶体管(FET)和感应电阻协同工作,确保在已供电系统中安全地插入插卡或模块。这种设计有效防止了因不当操作导致的短路、过流或欠压等问题。 用户可以通过一个由三个电阻组成的分压网络来设定欠压和过压关断阈值,这样的设计既简单又灵活,极大地提高了系统的适应性。此外,TPS2392还提供了两个活动低电平、去抖动的插入检测输入,用于实时监控插卡插入的状态,确保系统能够在第一时间响应插入事件,并采取相应的保护措施。 电源良好(PG)输出信号是TPS2392中的另一个关键特性,它允许下游转换器在安全条件下工作,提供了对下游设备的使能控制。这一功能确保了系统在电源模块插入或移除过程中不会对下游设备造成影响,保障了整个系统的稳定性。 TPS2392的故障定时器功能也是其一大亮点,它通过防止不必要的过流保护动作,避免了系统的误操作,从而提高了系统的可靠性和稳定性。开漏故障输出(FAULT)以及使能输入(EN)则提供了故障检测和报告机制,使得系统管理员能够及时获知系统状态并采取相应的维护措施。 TPS2392提供了两种封装类型,分别是14引脚TSSOP封装和44引脚TSSOP封装。前者适合常规应用,而后者则特别考虑了电信设备中对爬电距离和间隙的要求,以确保在高电压环境下能够提供足够的安全裕度。 在电路图中,电容C1、电阻R1、R2、R3和R4等组件发挥着关键作用。例如,R1、R2和R3组成的分压网络用于设置UVLO和OVP阈值,而C4则提供滤波功能,以稳定系统电压,进一步确保系统在瞬态变化中的可靠性。 总而言之,TPS2392和其伴侣产品TPS2393为高电压环境下的热插拔操作提供了一套全面的保护解决方案。它们集电流限制、电压保护、故障检测和报告等多种功能于一体,确保了在插入和移除电源模块时,整个系统的安全性和稳定性。这两款集成电路在电信基础设施和其他需要高可靠电源管理的领域中,无疑成为了理想的组件选择。

剩余34页未读,继续阅读

- 粉丝: 6386

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【创新无忧】基于豪猪优化算法CPO优化相关向量机RVM实现数据多输入单输出回归预测附matlab代码.rar

- 【创新无忧】基于黑翅鸢算法BKA优化广义神经网络GRNN实现电机故障诊断附matlab代码.rar

- 【创新无忧】基于黑翅鸢算法BKA优化极限学习机ELM实现乳腺肿瘤诊断附matlab代码.rar

- 【创新无忧】基于黑猩猩优化算法Chimp优化广义神经网络GRNN实现电机故障诊断附matlab代码.rar

- 【创新无忧】基于黑猩猩优化算法Chimp优化广义神经网络GRNN实现光伏预测附matlab代码.rar

- 【创新无忧】基于黑翅鸢算法BKA优化极限学习机KELM实现故障诊断附matlab代码.rar

- 【创新无忧】基于黑猩猩优化算法Chimp优化广义神经网络GRNN实现数据回归预测附matlab代码.rar

- 【创新无忧】基于黑猩猩优化算法Chimp优化极限学习机ELM实现乳腺肿瘤诊断附matlab代码.rar

- 【创新无忧】基于黑猩猩优化算法Chimp优化极限学习机KELM实现故障诊断附matlab代码.rar

- 【创新无忧】基于花朵授粉优化算法FPA优化广义神经网络GRNN实现电机故障诊断附matlab代码.rar

- 【创新无忧】基于黑猩猩优化算法Chimp优化相关向量机RVM实现北半球光伏数据预测附matlab代码.rar

- 【创新无忧】基于黑猩猩优化算法Chimp优化相关向量机RVM实现数据多输入单输出回归预测附matlab代码.rar

- 【创新无忧】基于花朵授粉优化算法FPA优化广义神经网络GRNN实现数据回归预测附matlab代码.rar

- 【创新无忧】基于花朵授粉优化算法FPA优化广义神经网络GRNN实现光伏预测附matlab代码.rar

- 【创新无忧】基于花朵授粉优化算法FPA优化极限学习机ELM实现乳腺肿瘤诊断附matlab代码.rar

- 【创新无忧】基于花朵授粉优化算法FPA优化相关向量机RVM实现数据多输入单输出回归预测附matlab代码.rar

信息提交成功

信息提交成功