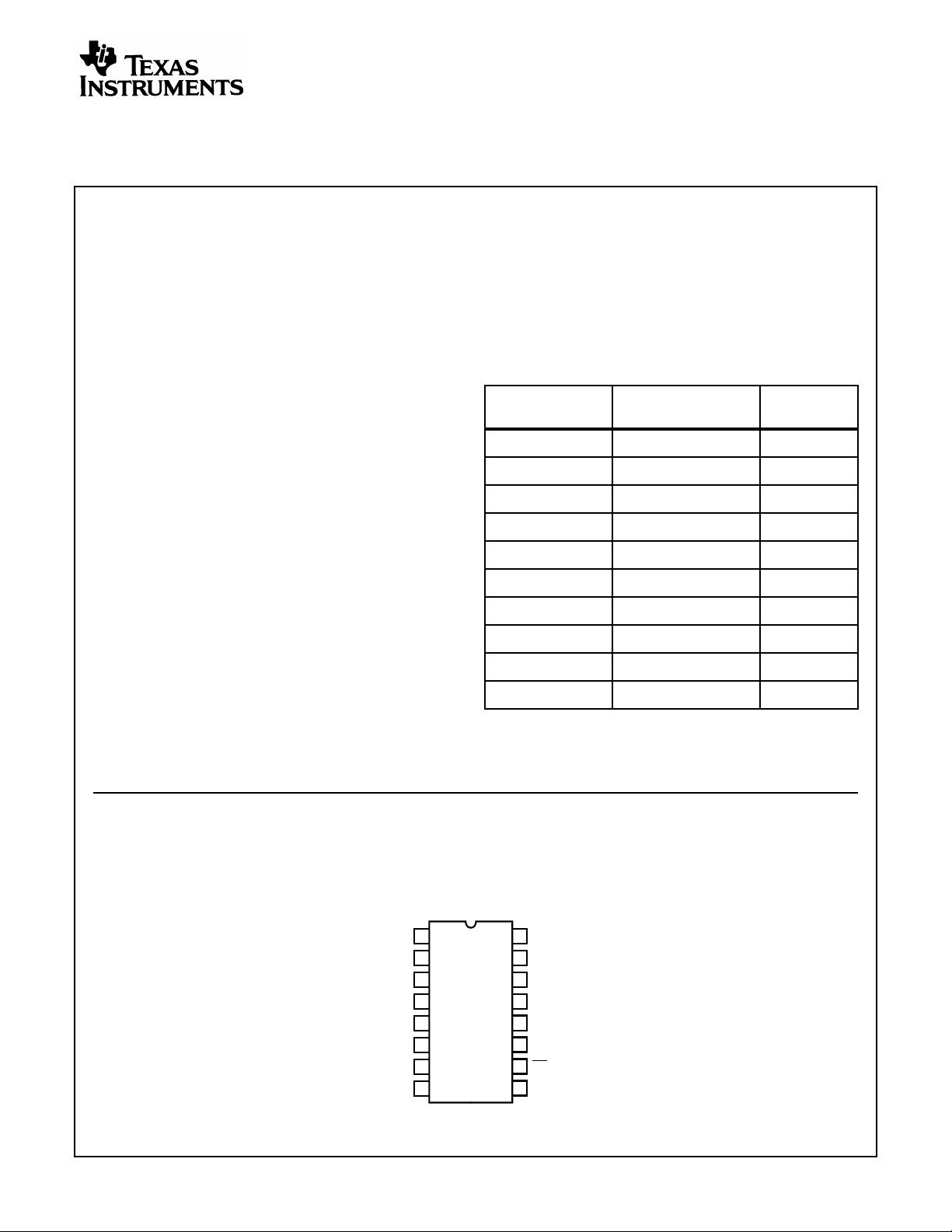

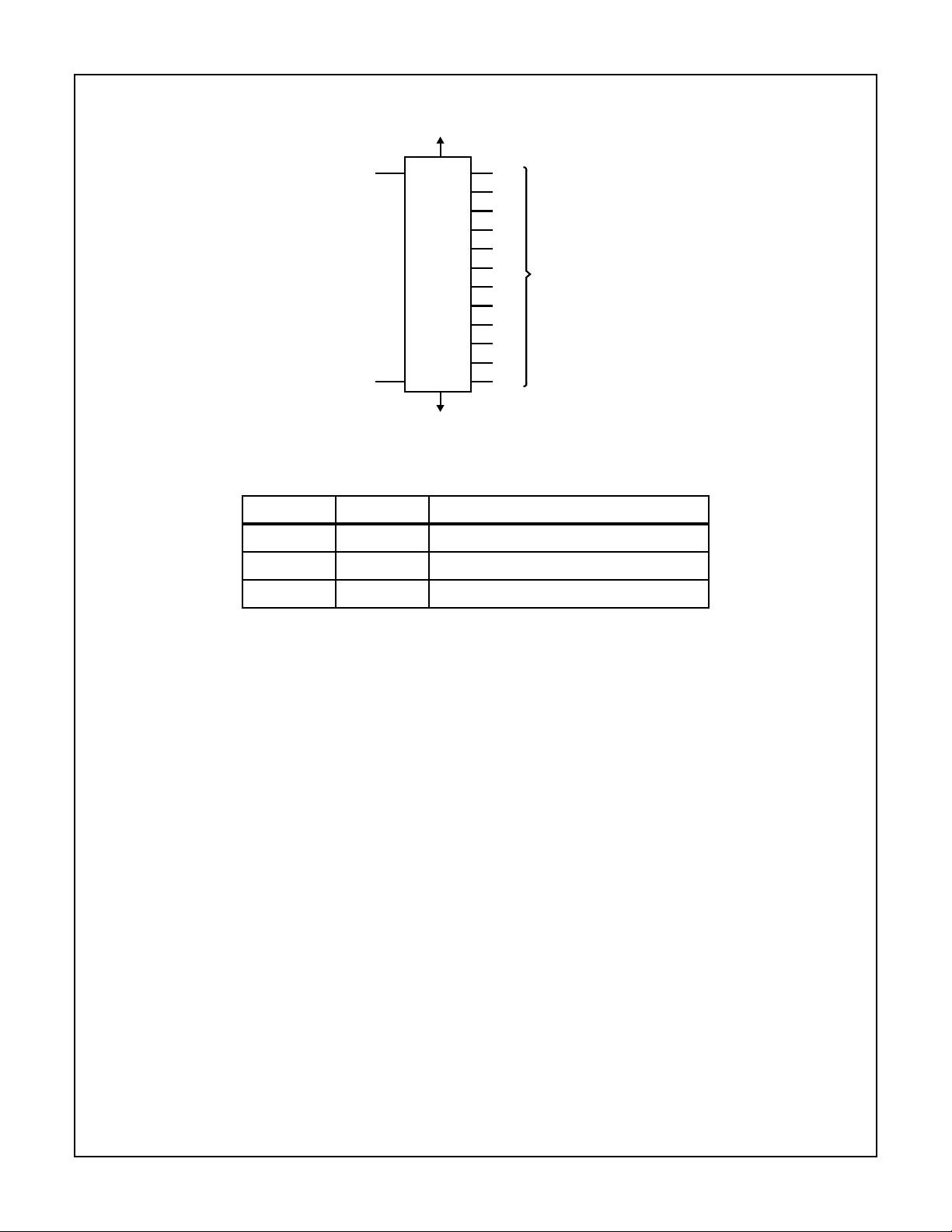

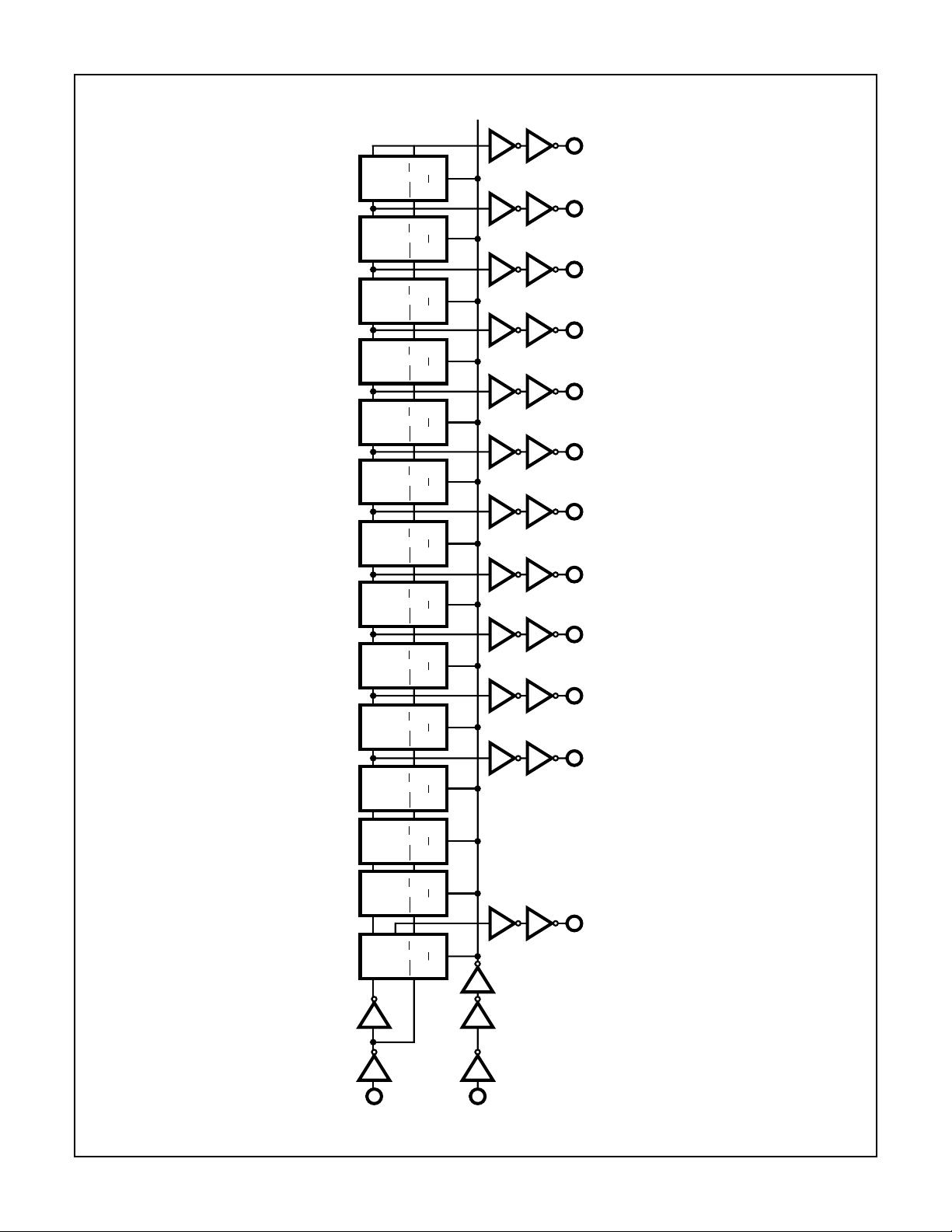

【TI-CD74HCT4020.pdf】文档主要介绍了TI公司生产的CD74HC4020和CD74HCT4020系列14级 Ripple-Carry 二进制计数器集成电路。以下是该芯片的主要特点、功能、操作特性以及封装和订购信息的详细解释: 1. **特点**: - 全静态操作:意味着即使没有时钟信号,电路也能保持其状态,不会因为时钟停止而丢失数据。 - 缓冲输入:每个输入都有缓冲器,以增强信号强度,减少外部信号对内部电路的影响。 - 共享复位(Common Reset):通过MR引脚实现全局复位,将所有计数器重置为零状态。 - 负边沿触发:时钟脉冲的下降沿触发计数器状态更新。 - 宽工作温度范围:-55°C至125°C,确保在极端环境下稳定工作。 - 平衡的传播延迟和转换时间:确保电路各个部分的工作同步性。 - 相比于LSTTL逻辑IC,显著降低功耗。 - HC类型:在2V到6V电压下工作,具有高噪声免疫力。 - HCT类型:在4.5V到5.5V电压下工作,兼容LSTTL输入逻辑,同时具有CMOS输入兼容性。 2. **功能**: - CD74HC4020和CD74HCT4020都是由14个主从触发器组成的二进制计数器,每个阶段在负时钟边沿到来时前进一位。 - 复位线(MR)处于高电平时,所有计数器都会被重置为零状态。 - 所有输入和输出都经过缓冲,提高了驱动能力和抗干扰能力。 3. **封装与订购信息**: - 提供多种封装选项,包括16引脚双列直插式(PDIP)、16引脚小外形集成电路(SOIC)和16引脚陶瓷双列直插式(CERDIP)等。 - 96后缀表示采用带状包装,适合大规模生产环境;T后缀表示小批量的250片卷盘包装。 4. **电气特性**: - 标准输出的扇出能力在全温度范围内为10个LSTTL负载,对于总线驱动器输出则为15个LSTTL负载。 - HC类型在VCC=5V时,噪声免疫级别为NIL = 30%,NIH = 30%的VCC。 - HCT类型兼容LSTTL输入逻辑,VIL最大为0.8V,VIH最小为2V,并且在VOL和VOH状态下,Il电流不超过1μA。 5. **应用领域**: - 该计数器适用于需要进行二进制计数的电子系统,如定时器、频率分频器、脉冲发生器和计数器模块等。 - 在工业控制、自动化设备、通信系统和数字电路设计等领域有广泛应用。 TI的CD74HC4020和CD74HCT4020是高性能CMOS逻辑器件,提供高效能和宽泛的操作条件,适用于需要高精度计数和稳定性的电子系统设计。其兼容性和低功耗特性使得它成为许多数字电路设计的首选组件。

剩余15页未读,继续阅读

- 粉丝: 8265

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Java、HTML、Vue、JavaScript、CSS的达内智慧车辆指挥系统设计源码

- 基于Vue和掌静脉技术的快速预约挂号系统设计源码

- 基于Kotlin语言的安卓全屏时钟设计源码

- 基于Vue、TypeScript、CSS、HTML的甜品驿站甜品驿站设计源码

- 基于Vue框架的移动端学分银行系统设计源码

- 基于JavaScript的Extjs前端框架学习与开发设计源码

- 基于Vue的H5广告设计源码,JavaScript、CSS、HTML全栈教程

- 基于Java语言的荣发代驾公司分布式系统设计源码

- 基于Vue和TypeScript的精选产品前端设计源码

- 基于Vue框架的小程序创建与设计源码教程

- 基于Java语言的云南道家文化应用设计源码

- 基于Java技术的Java苍穹外卖后端设计源码

- 基于若依框架的Vue故宫博物馆小程序设计源码

- 基于Vue框架的实训项目设计源码

- 基于C++与C语言的消消乐游戏设计源码分享

- 基于Java、CSS和JavaScript的第一次考核过程仓库代码设计源码

信息提交成功

信息提交成功