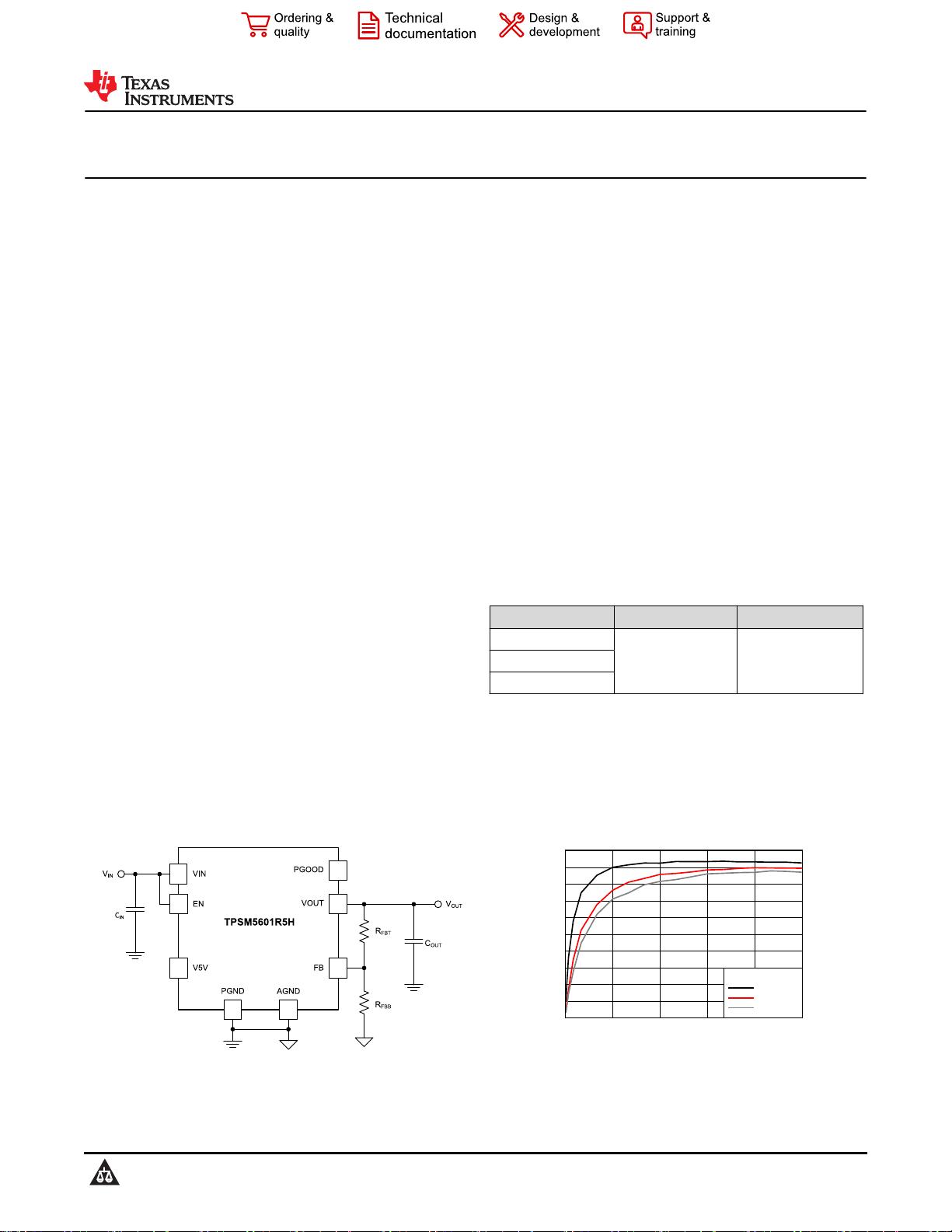

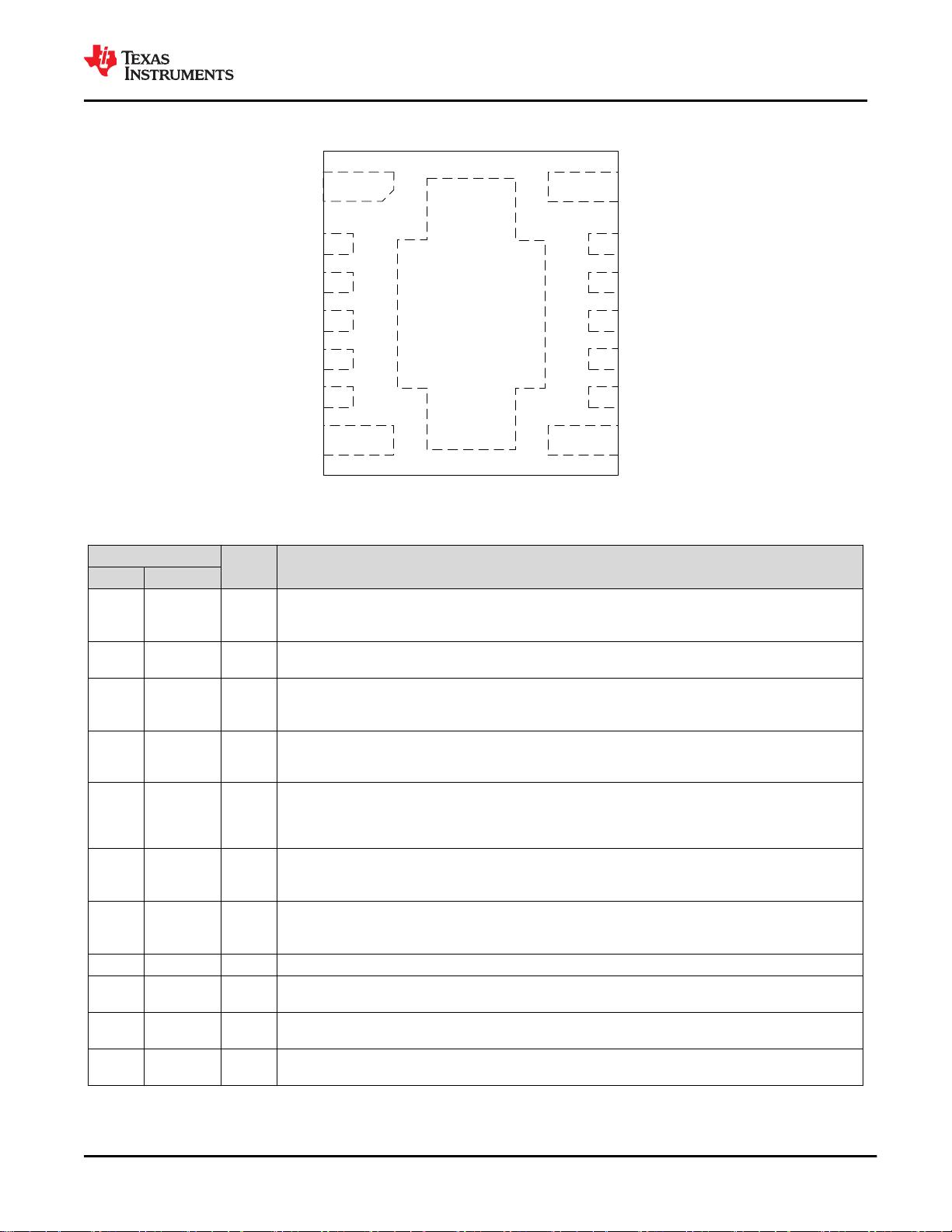

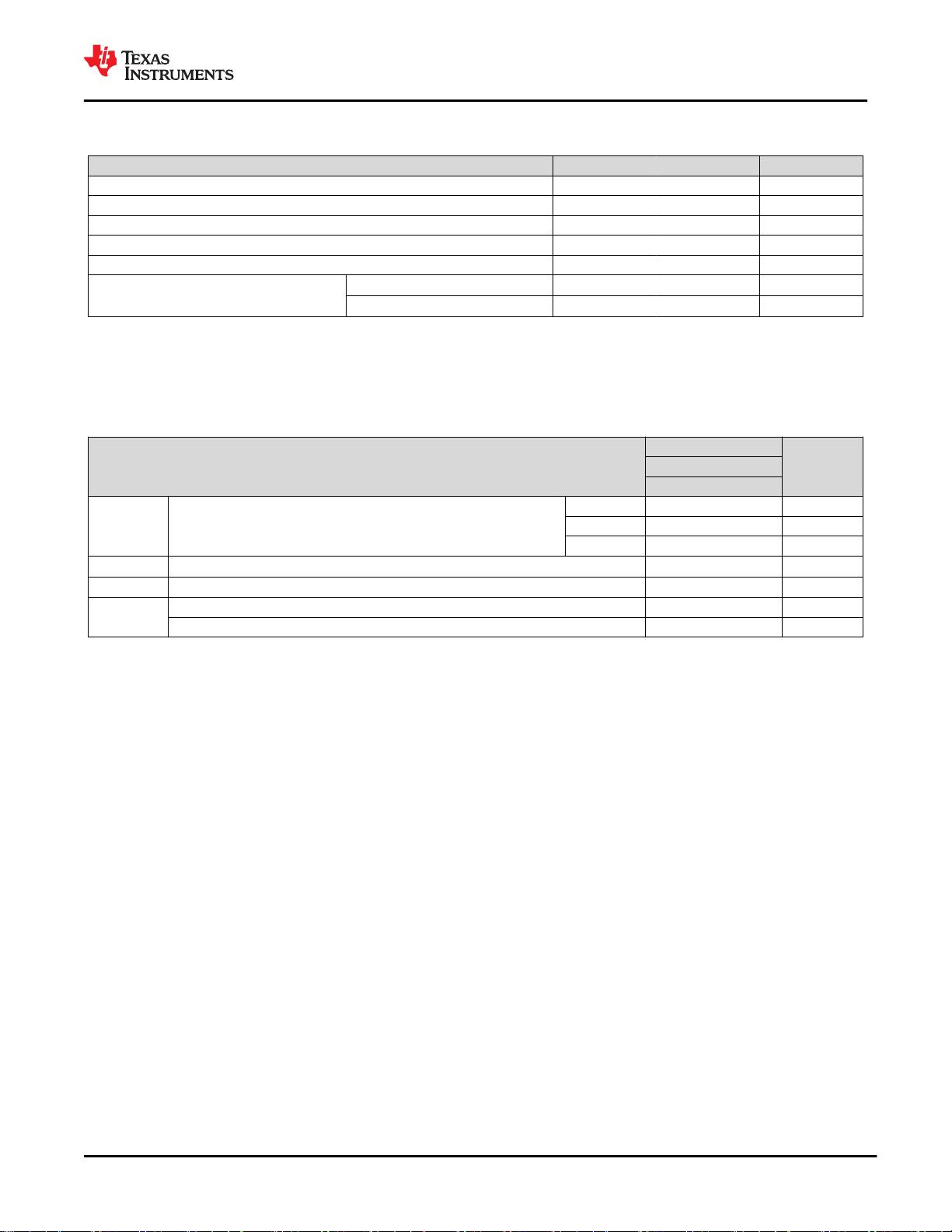

**TI TPSM5601R5HE电源模块详解** TI TPSM5601R5HE是一款高效、高集成度的电源模块,适用于需要60V输入电压、1V至16V输出电压及1.5A电流的应用。这款模块采用增强型Hotrod QFN封装,尺寸仅为5mm x 5.5mm x 4mm,具有出色的热性能,能够在85°C无气流条件下提供高达18W的输出功率。 **特性** 1. **封装设计**:该模块采用增强型Hotrod QFN封装,所有引脚分布在外围,配备大型散热焊盘,确保了良好的散热能力与小型化设计。 2. **宽输入电压范围**:支持4.2V至60V的输入电压,同时能够承受高达66V的输入电压瞬态保护,适合多种工作环境。 3. **工作温度范围**:标准型号的工作结温范围是-40°C至+125°C,EXT后缀的型号则扩展到-55°C至+125°C,增加了应用的适应性。 4. **开关频率**:固定1MHz的开关频率,简化了设计过程。 5. **EMI优化**:集成屏蔽式电感器和高频旁路电容器,符合EN55011 EMI标准,还有扩频选项以降低发射,降低了对外部电磁干扰的影响。 6. **低静态电流**:非开关静态电流仅为26µA,提高了能效。 7. **控制与保护**:具备单调启动、预偏置启动功能,以及具有迟滞的精密使能和输入UVLO,还具有过流和过热保护,增强了系统的稳定性和可靠性。 **应用** 1. **现场发送器和传感器**:适用于需要高效、稳定电源的远程监控设备。 2. **PLC模块**:在工业自动化系统中提供可靠的电源解决方案。 3. **恒温器、视频监控、HVAC系统**:满足智能家居和楼宇自动化设备的电源需求。 4. **交流和伺服驱动器、旋转编码器**:为工业自动化和运动控制设备供电。 5. **工业运输、资产跟踪**:适用于需要小巧、高效电源的移动设备。 6. **负输出应用**:支持负电压输出,扩大了应用范围。 **技术规格** TPSM5601R5HE电源模块提供了1.0V至16V的可调节宽输出电压范围,解决方案仅需4个外部组件,减少了设计复杂性。模块的典型效率图表显示了在不同输入电压下(24V, 48V, 60V)对12V输出时的效率,展示了其在各种负载条件下的高效表现。 **总结** TI TPSM5601R5HE电源模块因其小巧的封装、宽输入电压范围、高效率和内置保护功能,成为空间受限和需要高可靠性的工业应用的理想选择。设计人员可以利用WEBENCH Power Designer创建定制的稳压器设计方案,进一步优化其在特定应用中的性能。此外,不同的封装选项(如EXT和S后缀型号)为在极端温度和EMI要求下工作的系统提供了额外的灵活性。

剩余30页未读,继续阅读

- 粉丝: 6510

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Fluent激光电弧复合焊模拟 UDF包括高斯旋转体热源、双椭球热源(未使用)、VOF梯度计算、反冲压力、磁场力、表面张力,以及熔滴过渡所需的熔滴速度场、熔滴温度场和熔滴VOF

- 智能桌面宠物完整资料.zip

- 基于springboot的实习管理系统源码(java毕业设计完整源码+LW).zip

- Python期末大作业-奶牛疾病预测项目源码+报告(高分项目).zip

- 混合动力汽车simulink模型 P2插电式混合动力系统simulink模型 基于逻辑门限值控制策略 (模型可完美运行 ) ①(工况可自行添加)已有WLTC、UDDS、EUDC、NEDC工况; ②仿真

- 单相PWM整流器两种控制策略实现(交流220V-直流350V整流)仿真,分别采用直接电流控制(PR控制器)与dq控制(PI控制器)实现,两个仿真动稳态性能良好,附带仿真介绍文档,详细讲述仿真搭建过程

- EhLib VCL 10.2 Build 10.2.042 source

- matlab:基于遗传算法的多无人机协同任务分配 - 基于遗传算法的多无人机协同任务分配 - 种群中的每一个个体代表一次完整的任务分配方案,模型目标是找到代价函数的最小值,当作任务分配的最终方案 -

- top250电影资源翻页抓取python代码

- 机械设计走心机自动化step项目全套技术资料.zip

- SpringBoot的体育场馆预约小程序v12.0.1

- 机械设计左右循环倍数链线sw21可编辑项目全套技术资料.zip

- 2024雇佣关系趋势报告:新质职场重构增长路径-智联招聘-2024-24页.pdf

- 2024电商消费趋势年度报告-Flywheel-2024-90页.pdf

- 2024虎啸年度洞察报告—汽车行业-虎啸-2024-86页.pdf

- 2024年12月中国数据库行业分析报告-数据智能,融合创新-墨天轮-2024.12.13-48页.pdf

信息提交成功

信息提交成功

评论0