安森美半导体ESD保护器件PACVGA105-D 数据手册.pdf

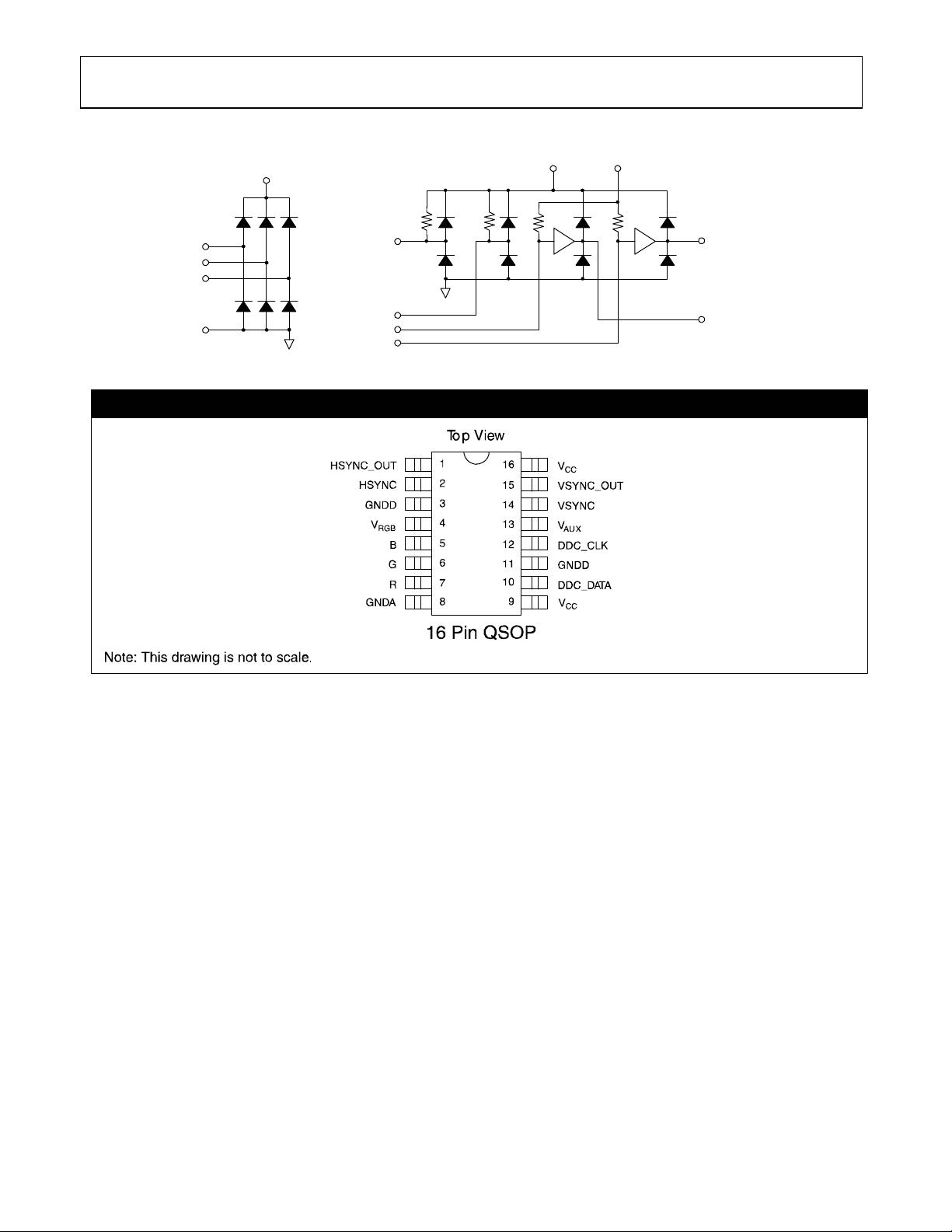

安森美半导体推出的PACVGA105-D是一种专为视频端口接口设计的七通道ESD(静电放电)保护器件,旨在满足IEC-1000-4-2第四级静电放电要求,提供±8kV接触放电保护。该器件具备多个特点和应用场景,以下将详细解析PACVGA105-D的产品特性及技术要点。 1. 多通道ESD保护:PACVGA105-D包含七条信号线的ESD保护通道,这些信号线常见于个人电脑的VGA端口。它通过电流引导二极管来实现保护功能,这些二极管能够安全处理与IEC-1000-4-2第四级ESD保护标准相关的高峰值浪涌电流。 2. 低负载电容:该器件的ESD保护二极管在典型状态下具有非常低的负载电容,小于5pF。低负载电容意味着对高速信号线的影响小,适合在高速数据传输环境中使用。 3. TTL至CMOS电平转换缓冲器:PACVGA105-D包括用于HSYNC(水平同步)和VSYNC(垂直同步)信号的TTL至CMOS电平转换缓冲器。这些缓冲器接受TTL输入电平,并将其转换为在地(GND)和VCC之间摆动的CMOS输出电平。 4. 独立的供电引脚:器件拥有三个独立的供电引脚,分别是VCC、VRGB和VAUX,以方便与亚微米级图形控制器ICs(集成电路)的操作。VRGB供电引脚与R(红色)、G(绿色)和B(蓝色)通道的ESD保护二极管的上部相连,而剩余的通道则连接到主要的5V供电轨(VCC)。 5. 高阻抗上拉电阻:为了减少由于公共地阻抗导致的串扰,R、G和B通道的ESD保护二极管下部还连接到一个专用的地引脚(GNDA)。此外,HSYNC和VSYNC输入还具备高阻抗上拉电阻至VAUX引脚,其标称值为50kΩ。DDC_CLK和DDC_DATA信号线上则有1.8kΩ标称值的上拉电阻至VCC引脚。 6. 紧凑型封装:PACVGA105-D采用16引脚的QSOP(四边扁平封装)封装,具有较高的集成度和较小的占用空间。 7. 无铅版本:该器件提供无铅版本,以符合现代电子制造工艺对环保材料的需求。 8. 应用范围:PACVGA105-D适用于多种应用,包括视频端口接口、台式电脑、笔记本电脑和LCD显示器。它特别适用于对ESD保护和VGA端口的终端电阻器的场合。 PACVGA105-D是为视频端口接口设计的高效能保护器件,针对工业级的静电放电保护需求提供了可靠且高效能的解决方案。其设计考虑了多种实际应用场景,提供了良好的保护功能、简洁的接口和高兼容性,为VGA端口相关的设备提供有力的静电保护。

剩余8页未读,继续阅读

- 粉丝: 698

- 资源: 4万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 数据结构上机实验大作业-线性表选题.zip

- 字幕网页文字检测20-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- 雪毅云划算试客系统v2.9.7标准版 含购物返利+免费试用+9.9包邮+品牌折扣+推广中心等

- 冒泡排序算法详解及Java与Python实现

- 实时 零代码、全功能、强安全 ORM 库 后端接口和文档零代码,前端(客户端) 定制返回 JSON 的数据和结构

- 混合有源滤波器(HAPF) MATLAB-Simulink仿真 仿真模拟的HAPF补偿前后,系统所含的谐波对比如下图所示

- csi-driver-nfs

- 认识小动物-教案反思.docx

- pdfjs2.5.207和4.9.155

- 2023-04-06-项目笔记 - 第三百五十五阶段 - 4.4.2.353全局变量的作用域-353 -2025.12.22

- OPCClient-UA源码OPC客户端源码(c#开发) 另外有opcserver,opcclient的da,ua版本的见其他链接 本项目为VS2019开发,可用VS其他版本的编辑器打开项目 已应

- 2023-04-06-项目笔记 - 第三百五十五阶段 - 4.4.2.353全局变量的作用域-353 -2025.12.22

- PHP快速排序算法实现与优化

- deploy.yaml

- 家庭用具检测15-YOLO(v8至v11)数据集合集.rar

- RuoYi-Cloud-Plus 微服务通用权限管理系统

信息提交成功

信息提交成功