安森美半导体ESD保护器件CM1234-D 数据手册.pdf

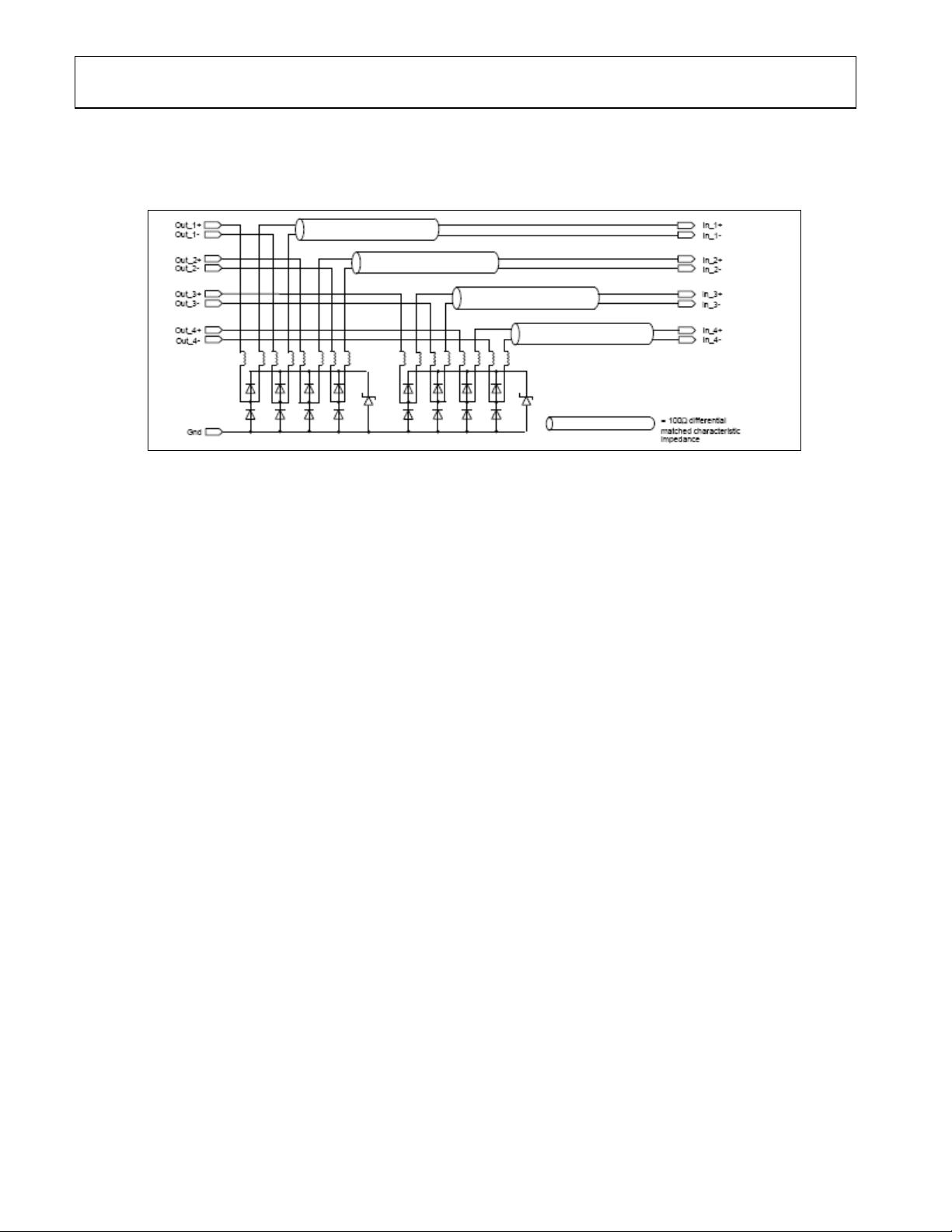

根据提供的文件内容,以下是对安森美半导体ESD保护器件CM1234-D数据手册的知识点的详细说明: 标题解读: - CM1234-D是安森美半导体公司推出的ESD(静电放电)保护器件型号。 - 数据手册提供了该器件的技术参数、性能特点和应用场景等详细信息。 描述解读: - 数据手册详细介绍了CM1234-D的特性、封装信息以及如何使用在高速数据线上进行静电保护。 标签解读: - 综合资料表明,该手册中包含的信息是多方面的,包括技术规格、应用指导等,旨在为读者提供全面的产品参考。 部分内容解读: 1. CM1234-D具有以下特点: - 为四对差分高速数据线提供ESD保护。 - 符合IEC61000-4-2等级4的ESD保护标准,能够承受±15kV接触放电和±20kV空气放电。 - 通过了1000次以上的ESD冲击测试(±8kV接触放电,1000脉冲)。 - 提供匹配阻抗为100欧姆的通过式钳位,适合高速信号的完整性。 - 设计采用了流经式布线架构,以最小化温度和电压变化对线路电容的影响。 - 符合RoHS标准的无铅TDFN-16封装,具有小型化的足迹。 2. 应用领域包括: - 笔记本电脑、机顶盒、数字电视、LCD显示等的DVI和HDMI端口。 - 需要极低负载电容和ESD保护的高速数据线保护通用应用。 3. CM1234-D产品特点: - PicoGuardXS®系列ESD保护钳位阵列为下一代深亚微米高速数据线提供保护。 - 特别适合于数据和时钟速率高的系统,或者对信号偏差控制要求严格的电路。 - 设计为具备优异的通道间匹配(最大偏差2%),低负载电容和ESD保护。 - 适合用于DVI、HDMI等高速端口,以及其他需要低负载电容ESD保护的应用场合。 4. PicoGuardXS ESD保护架构概念: - 在ESD冲击放电到被保护的ASIC(应用特定集成电路)时,ESD保护器件将执行以下动作: a) 当ESD电位施加到待测系统(接触或空气放电)时,基尔霍夫电流定律(KCL)表明,电路中将产生超出正常工作范围的电流。 b) ESD保护器件将处理这些过电流,从而保护ASIC不受损害。 5. 实际测试条件与器件承受能力: - 标准测试条件是IEC61000-4-2等级4测试电路,每个引脚承受±8kV接触放电1000次脉冲。 - 放电间隔1秒,连续进行1000次放电测试。 - 测试后,器件需经过标准生产测试以验证所有测试参数在1000次放电后仍在规范范围内。 以上是对安森美半导体CM1234-D型ESD保护器件数据手册的内容解读和知识点总结。这份手册详细描述了器件的特性、使用场景和重要参数,为设计者提供必要的信息,以确保在高速数据传输系统中能够有效防止ESD对敏感电路的潜在损害。

剩余12页未读,继续阅读

- 粉丝: 698

- 资源: 4万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (33269446)全国省市县经纬度xml数据(全)

- ip地址查询城市php代码

- jieba分词自定义分词词表

- (6340824)C语言学生信息管理系统

- 床、自行车、瓶子、碗、公交车、食堂、小型车检测12-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- (6351410)c++经典程序200例

- (7276248)c语言图书管理系统

- (9368016)C++ STL使用

- (10377004)C语言下实现的学生管理系统

- (15341010)经典C程序一百例

- (174549194)ANSYS Fluent Tutorial Guide

- (175909636)全国293个地级市的经纬度信息

- 尚硅谷宋红康C语言精讲.zip

- 视图库级联抓包,支持GA/T1400-2018版,包括Register, keepalive, subscribe, subscribeNotification等

- ip地址查询区域代码包括php c++ python golang java rust代码使用例子

- C语言结构体精讲,结构体在内存中的访问

信息提交成功

信息提交成功