编译环境:Xilinx ISE 10.1

仿真环境:Xilinx ISE 10.1 与 Modelsim PE Student Edition 联合仿真

开发语言:Verilog HDL

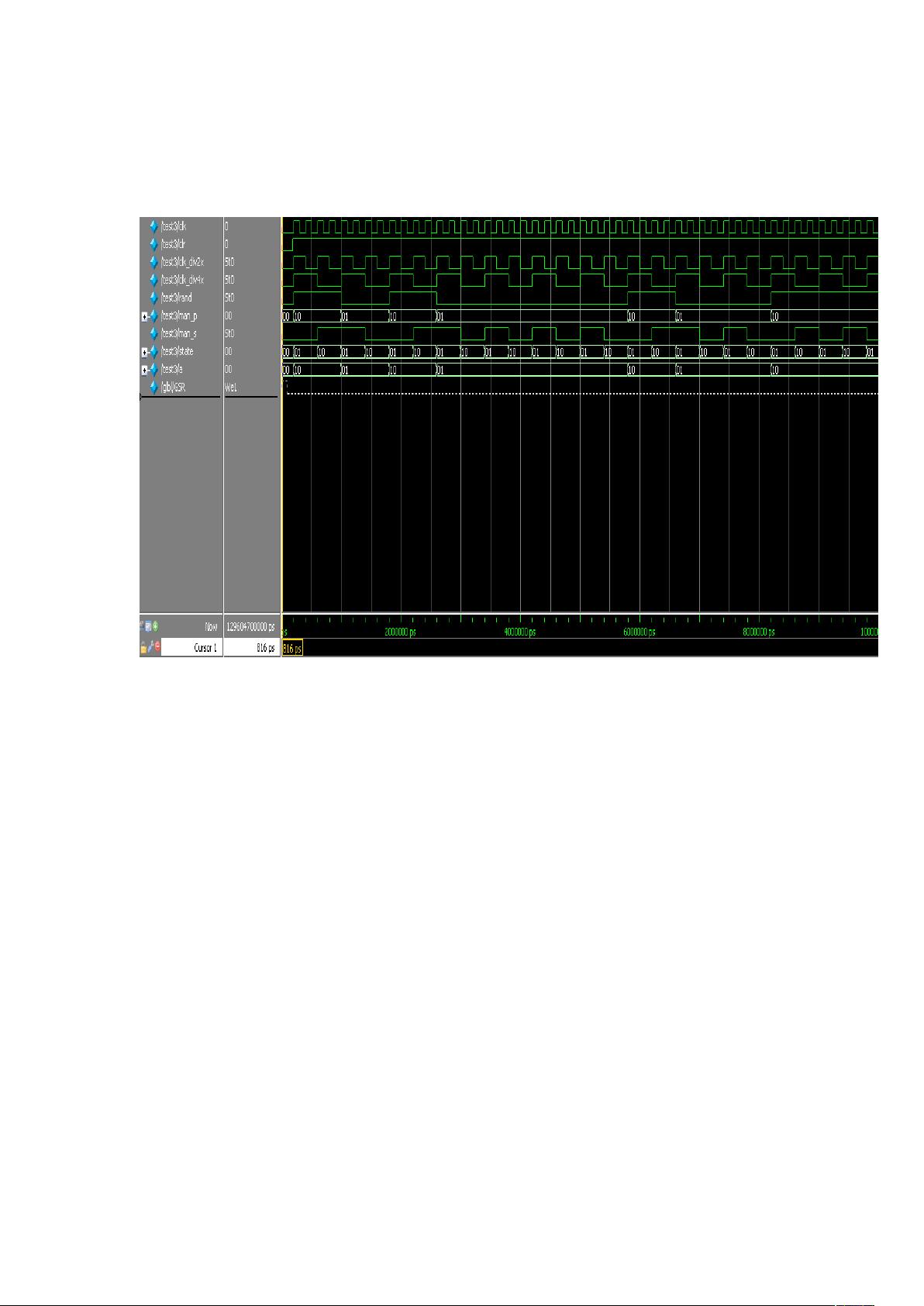

部分仿真结果:

信号说明:

clk:内部时钟信号,50MHz;

clr:复位信号,低电平有效;

clk_div2x:时钟信号 2 分频,25MHz,用以驱动有限状态机及缓存的输出;

clk_div4x:时钟信号 4 分频,12.5MHz,用以驱动线性反馈移位寄存器;

rand:伪随机序列;

man_p:曼彻斯特编码的并行输出;

man_s:曼彻斯特编码的串行输出;

state:状态信号;

a:缓存。