### 伪随机序列的产生——C语言与Verilog实现

#### 实验背景及目标

伪随机序列在通信、密码学以及模拟系统等领域有着广泛的应用。这类序列具备良好的统计特性和可预测性,使得它们能够在不引入真正随机性的前提下模拟随机行为。本文将通过具体的例子介绍如何使用C语言和Verilog两种不同的编程方式来实现伪随机序列的产生,并对其实现过程中的关键概念和技术细节进行详细的解析。

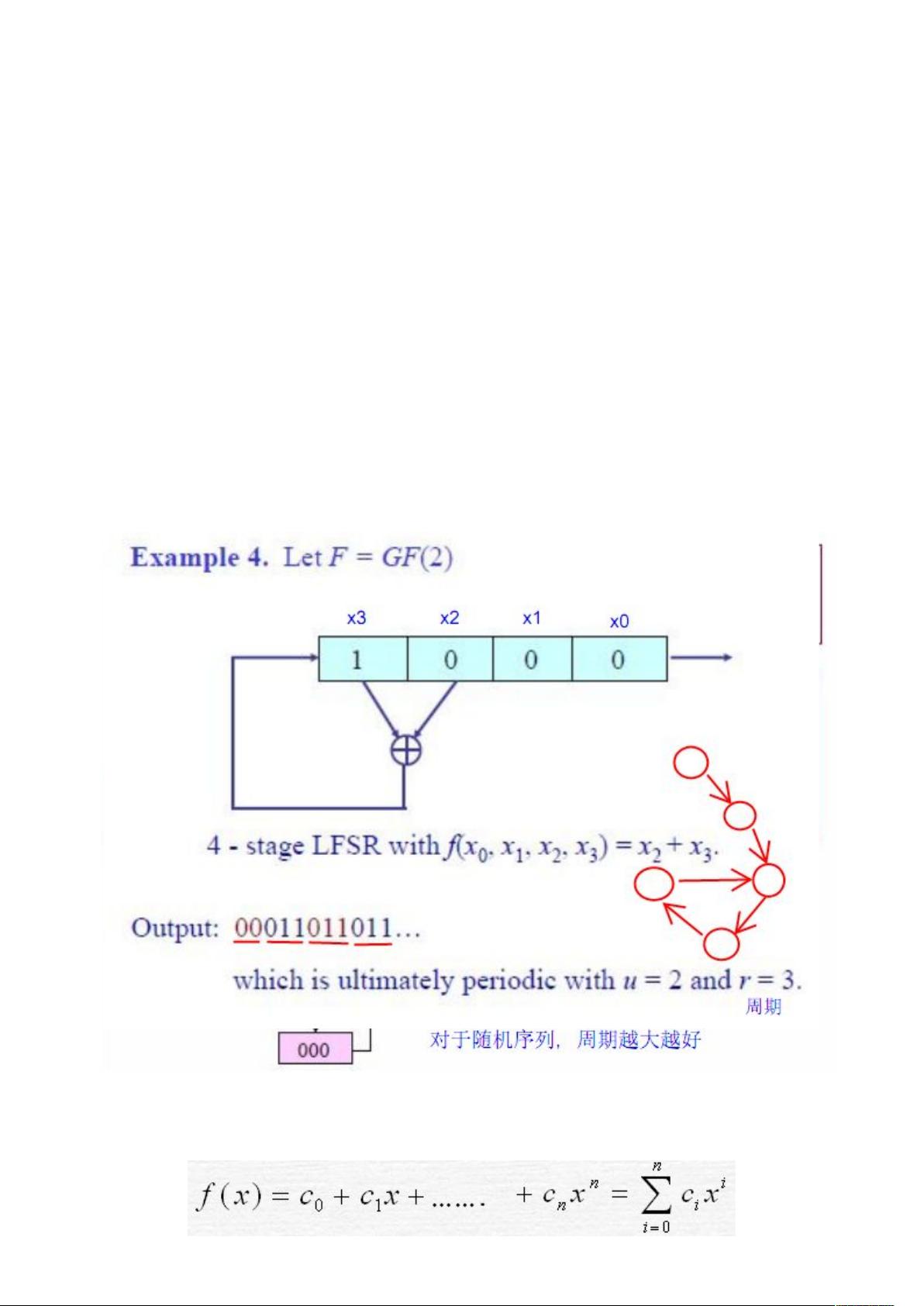

#### LFSR(线性反馈移位寄存器)

线性反馈移位寄存器(Linear Feedback Shift Register, LFSR)是一种可以生成伪随机序列的数字电路结构。它由一系列寄存器和异或门组成,能够根据特定的反馈逻辑产生序列。LFSR的序列周期取决于寄存器的长度和反馈逻辑的设置,当采用特定的本原多项式时,可以产生最大长度的序列,即m序列。

#### 实验要求

本次实验要求实现一个10级的LFSR,并使用给定的特征多项式 \( f(x) = x^{10} + x^3 + 1 \) 来产生伪随机序列。具体来说,需要完成以下任务:

1. **C语言建模**:使用C语言编写程序实现LFSR的逻辑,并产生指定长度的伪随机序列。

2. **Verilog实现**:利用Verilog硬件描述语言编写相应的代码,生成非零伪随机序列,并分析其周期和自相关性。

3. **综合工具应用**:使用Synplify Pro和XST等工具进行代码综合,验证设计的正确性。

#### 实验原理

- **线性反馈移位寄存器的特征多项式**:通过多项式 \( f(x) \) 描述LFSR的反馈连接状态,其中 \( C_0 = C_n = 1 \),多项式的次数 \( n \) 表示移位寄存器的级数,系数 \( C_i \) 的取值 (1 或 0) 确定反馈线的连接状态。

- **m序列**:最长线性反馈移位寄存器序列的简称。要构成m序列发生器,必须确保特征多项式为本原多项式。对于10级的LFSR,若采用 \( f(x) = x^{10} + x^3 + 1 \),则可以生成m序列。

- **伪随机序列的性质**:

- **均衡特性(平衡性)**:在每个周期内,1与0出现的次数基本相等,且1的个数比0多1个。

- **游程分布**:游程是指序列中连续相同的值。m序列的游程分布表现出随机性。

- **自相关特性**:m序列具有良好的自相关性,即序列与其自身的延迟版本之间的相关性。

#### 实验源码

##### C语言建模实现

```c

#include <stdio.h>

int main(void) {

int i, j, msb;

int polynomial[10] = {0};

int seq[2046];

printf("Please input the initial state of LFSR:\n");

for (i = 0; i < 10; i++) {

scanf("%d", &polynomial[i]);

}

for (i = 0; i < 2046; i++) {

seq[i] = polynomial[0];

msb = polynomial[0] ^ polynomial[3];

for (j = 0; j < 9; j++) {

polynomial[j] = polynomial[j + 1];

}

polynomial[9] = msb;

}

for (i = 0; i < 2046; i++) {

if (i == 1023) {

printf("\n");

printf("The current LFSR is:\n");

for (j = 0; j < 10; j++) {

printf("%d", polynomial[j]);

}

printf("\n");

}

printf("%d", seq[i]);

}

printf("\n");

return 0;

}

```

##### Verilog源码实现

```verilog

module lfsr(din, dout, load, clk);

input [9:0] din;

input load;

input clk;

output dout;

reg [9:0] data;

wire feedback;

assign feedback = data[3] ^ data[0];

assign dout = data[0];

always @(posedge clk) begin

if (load) begin

data <= din;

end else begin

data <= {feedback, data} >> 1;

end

end

endmodule

```

##### 测试LFSR伪随机序列发生器的TestBench源码

```verilog

module test_lfsr;

reg [9:0] din;

reg load;

reg clk;

wire dout;

wire feedback;

reg [9:0] data;

integer counter;

always #5 clk = ~clk;

initial begin

din = 10'b0000000000;

load = 1'b1;

clk = 1'b0;

counter = 0;

#5 din = 10'b0110101111;

#20 load = 1'b0;

#10240 $stop;

end

assign feedback = data[3] ^ data[0];

assign dout = data[0];

always @(posedge clk) begin

if (load) begin

data <= din;

end else begin

data <= {feedback, data} >> 1;

$write("%d", dout);

counter = counter + 1;

if (counter == 2046) $finish;

end

end

endmodule

```

以上代码实现了基于C语言和Verilog的伪随机序列生成器。通过这些实现,我们可以进一步分析和理解伪随机序列的特性和应用场景,同时也可以根据实际需求调整特征多项式或其他参数以满足不同的技术要求。

- 1

- 2

- 3

前往页