EDA基础实验

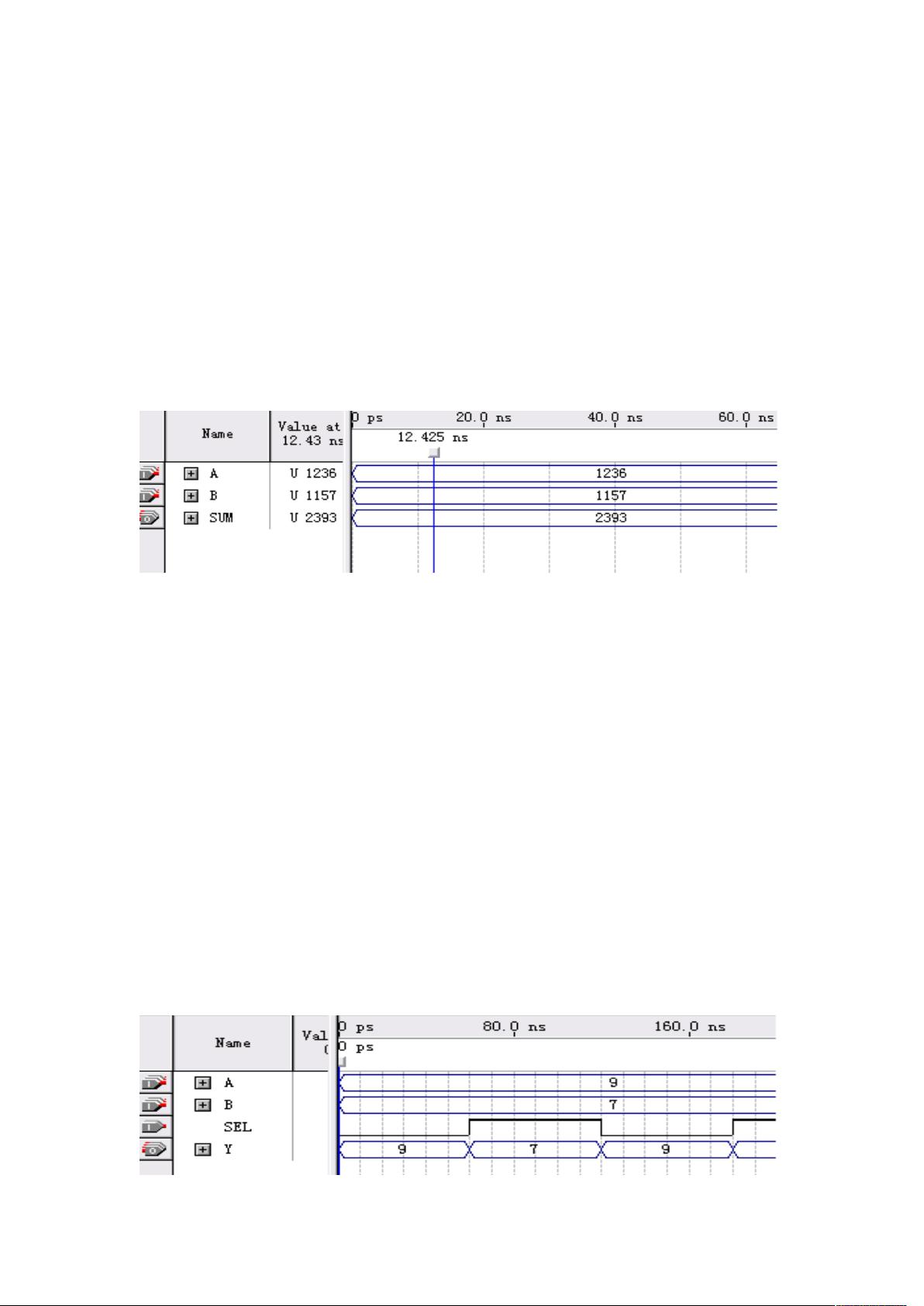

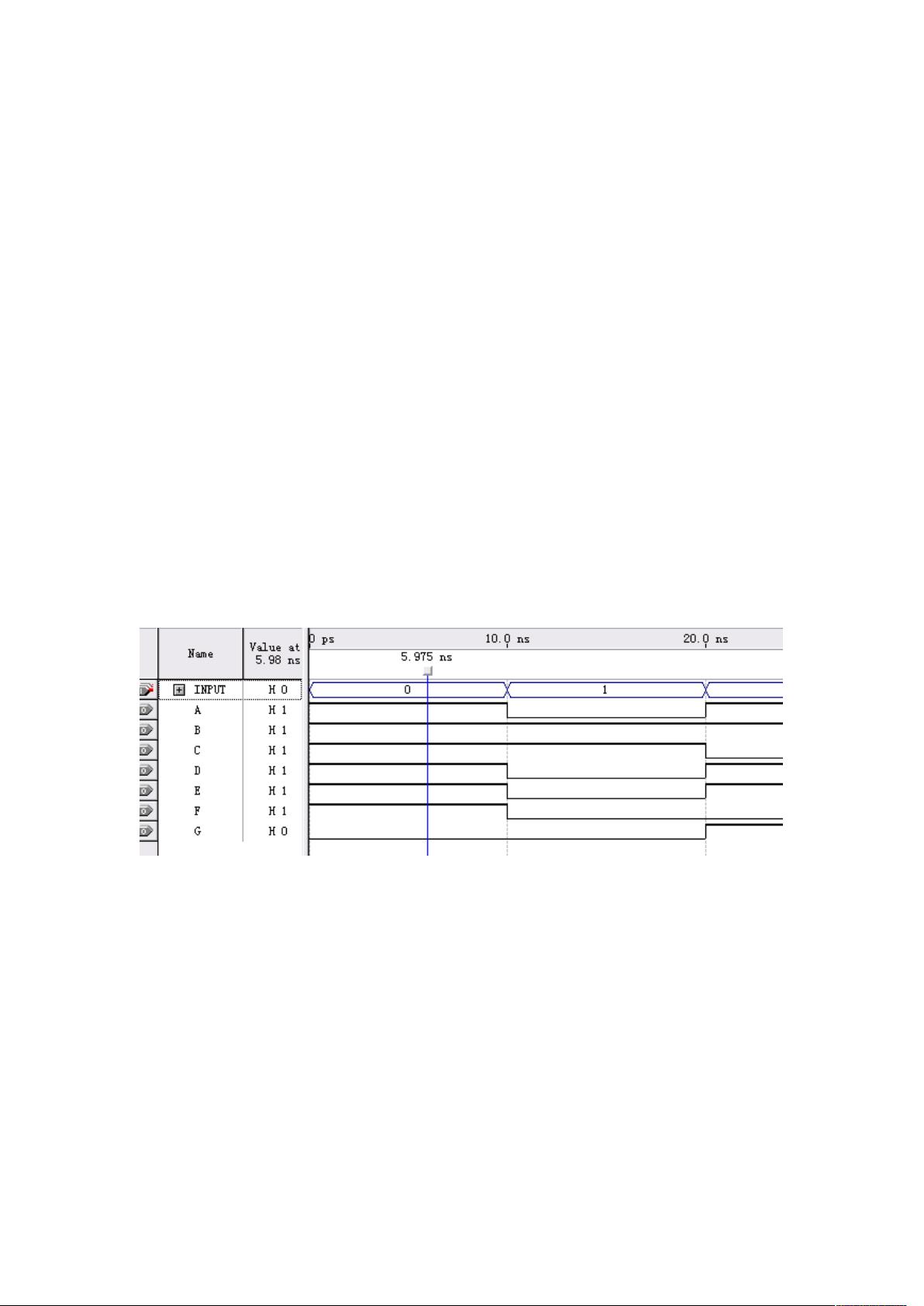

### EDA基础实验知识点概述 #### 1. 十六位加法器 在数字电路设计领域,加法器是一种非常基本且重要的算术逻辑单元(ALU),用于执行两个二进制数的加法运算。加法器分为半加器和全加器两种类型,而复杂的加法操作可以通过串联多个全加器来实现。本实验中提到的十六位加法器即为一种串联了十六个全加器的设计。 **VHDL代码解析:** ```vhdl ENTITY ADDER IS PORT( A, B : IN STD_LOGIC_VECTOR(15 DOWNTO 0); SUM : OUT STD_LOGIC_VECTOR(15 DOWNTO 0) ); END ADDER; ARCHITECTURE behav OF ADDER IS BEGIN SUM <= A + B; END behav; ``` - **实体定义**:这里定义了一个名为`ADDER`的实体,该实体有两个输入端口`A`和`B`,均为16位的标准逻辑向量类型,以及一个输出端口`SUM`,同样是16位的标准逻辑向量。 - **结构体定义**:通过简单的加法操作`SUM <= A + B;`实现了加法器的功能。 #### 2. 四位的二选一多路选择器 多路选择器(Multiplexer)是一种组合逻辑电路,它可以根据控制信号的选择,将多个数据输入中的某一个传输到单个输出。在这个实验中,我们关注的是一个四位的二选一多路选择器。 **VHDL代码解析:** ```vhdl ENTITY MUX4 IS PORT( A, B : IN STD_LOGIC_VECTOR(3 DOWNTO 0); SEL : IN INTEGER RANGE 0 TO 1; Y : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END MUX4; ARCHITECTURE behav OF MUX4 IS BEGIN PROCESS(SEL) BEGIN IF SEL = 0 THEN Y <= A; ELSE Y <= B; END IF; END PROCESS; END behav; ``` - **实体定义**:定义了一个名为`MUX4`的实体,包含两个四位的数据输入端口`A`和`B`、一个选择控制端口`SEL`(取值范围为0或1)、一个四位的数据输出端口`Y`。 - **结构体定义**:根据`SEL`的值来决定将哪一个输入端口的数据输出。 #### 3. 七段数码管译码器 七段数码管是一种常见的显示器件,它由七个发光二极管组成,可以显示数字0至9以及部分字母。为了驱动这些七段数码管,通常需要一个译码器将数字转换成相应的七段编码。 **VHDL代码解析:** ```vhdl ENTITY LED7 IS PORT( INPUT : IN STD_LOGIC_VECTOR(2 DOWNTO 0); A, B, C, D, E, F, G : OUT STD_LOGIC ); END LED7; ARCHITECTURE behav OF LED7 IS BEGIN PROCESS(INPUT) BEGIN CASE INPUT IS WHEN "000" => A <= '1'; B <= '1'; C <= '1'; D <= '1'; E <= '1'; F <= '1'; G <= '0'; WHEN "001" => A <= '0'; B <= '1'; C <= '1'; D <= '0'; E <= '0'; F <= '0'; G <= '0'; WHEN "010" => A <= '1'; B <= '1'; C <= '0'; D <= '1'; E <= '1'; F <= '0'; G <= '1'; WHEN "011" => A <= '1'; B <= '0'; C <= '0'; D <= '1'; E <= '1'; F <= '1'; G <= '1'; WHEN OTHERS => A <= '1'; B <= '0'; C <= '1'; D <= '0'; E <= '0'; F <= '1'; G <= '1'; END CASE; END PROCESS; END behav; ``` - **实体定义**:定义了一个名为`LED7`的实体,有一个三位的输入端口`INPUT`,以及七个输出端口`A`、`B`、`C`、`D`、`E`、`F`、`G`,分别对应七段数码管的七个段。 - **结构体定义**:通过一个`CASE`语句根据输入的不同,输出不同的七段编码,从而控制数码管显示不同的数字。 #### 4. 8位16位移位器 移位器是一种可以对二进制数进行左移或右移操作的电路。本实验中涉及的是一个8位的移位器,它可以将输入的8位数据左移或右移,并扩展成16位的数据输出。 **VHDL代码解析:** ```vhdl ENTITY shifter IS PORT( input : IN std_logic_vector(7 DOWNTO 0); cnt : IN std_logic_vector(1 DOWNTO 0); result : OUT std_logic_vector(15 DOWNTO 0) ); END shifter; ARCHITECTURE logic OF shifter IS BEGIN PROCESS(input, cnt) VARIABLE temp : std_logic_vector(15 DOWNTO 0); BEGIN temp(15 DOWNTO 8) := "00000000"; temp(7 DOWNTO 0) := input; IF cnt = "01" THEN FOR i IN 15 DOWNTO 4 LOOP temp(i) := temp(i - 4); END LOOP; temp(3 DOWNTO 0) := "0000"; ELSIF cnt = "10" THEN FOR ii IN 15 DOWNTO 8 LOOP temp(i) := temp(i - 8); END LOOP; temp(7 DOWNTO 0) := "00000000"; ELSE temp := temp; END IF; result <= temp; END PROCESS; END logic; ``` - **实体定义**:定义了一个名为`shifter`的实体,包括一个8位的输入端口`input`、一个2位的控制端口`cnt`(用于指定移位方向)和一个16位的输出端口`result`。 - **结构体定义**:通过`IF`语句根据`cnt`的值来进行不同的移位操作,利用`FOR`循环实现移位操作,并将结果保存在变量`temp`中,最终输出。 #### 5. A16位同步寄存器 同步寄存器是一种时序逻辑电路,可以在时钟信号的控制下存储并传递数据。本实验中的十六位同步寄存器能够在一个时钟周期内存储16位数据,并在下一个时钟周期将其输出。 **VHDL代码解析:** 由于给定的部分内容中没有完整的同步寄存器的VHDL代码,以下给出一个十六位同步寄存器的基本架构示例: ```vhdl ENTITY reg IS PORT( CLK : IN std_logic; CLKEN : IN std_logic; CLR : IN std_logic; IN_REG : IN std_logic_vector(15 DOWNTO 0); OUT_REG: OUT std_logic_vector(15 DOWNTO 0) ); END reg; ARCHITECTURE logic OF reg IS BEGIN PROCESS(CLK, CLR) BEGIN IF CLR = '1' THEN OUT_REG <= (OTHERS => '0'); ELSIF RISING_EDGE(CLK) AND CLKEN = '1' THEN OUT_REG <= IN_REG; END IF; END PROCESS; END logic; ``` - **实体定义**:定义了一个名为`reg`的实体,包括一个时钟信号输入端口`CLK`、使能信号端口`CLKEN`、复位信号端口`CLR`、16位数据输入端口`IN_REG`以及16位数据输出端口`OUT_REG`。 - **结构体定义**:通过一个时钟敏感过程`PROCESS`,根据`CLR`和`CLK`的值来决定是否复位寄存器或更新寄存器中的数据。当`CLR`为高电平时,寄存器清零;当检测到`CLK`的上升沿并且`CLKEN`为高电平时,将`IN_REG`中的数据赋值给`OUT_REG`。 以上五个部分详细介绍了EDA基础实验中涉及到的关键电路设计与实现,涵盖了从基本的加法器到复杂的同步寄存器等多个方面。这些实验不仅有助于加深对EDA工具的理解和应用,而且对于掌握数字系统设计的基本原理和技术具有重要意义。

剩余11页未读,继续阅读

limeng3432011-12-10这篇文档包含有十六位加法器,四位的二选一多路选择器,七段数码管,8位16位移位器,编程方面很基础,比较容易理解,希望多弄一些这样的文档。。。谢谢

limeng3432011-12-10这篇文档包含有十六位加法器,四位的二选一多路选择器,七段数码管,8位16位移位器,编程方面很基础,比较容易理解,希望多弄一些这样的文档。。。谢谢

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 六轴,scara机器人运动学分析,建模和运动控制 matlab,simulink,simscape.机器人工具箱,DH建模 Pd控制,滑模控制,模糊控制等等

- 车辆,汽车检测1-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- 美国旧金山28R粗糙跑道数据

- mp3转换器小程序-音频20241222115740.mp3

- 车辆船只检测8-YOLO(v5至v9)、COCO、CreateML、Darknet、Paligemma、TFRecord、VOC数据集合集.rar

- Questasim仿真脚本2

- Questasim仿真脚本

- Django开发中常见问题与解决方案的全面指南

- 西工大noj 116题及答案word版.doc

- 四足机器人步态控制算法的技术原理及Python实现

信息提交成功

信息提交成功