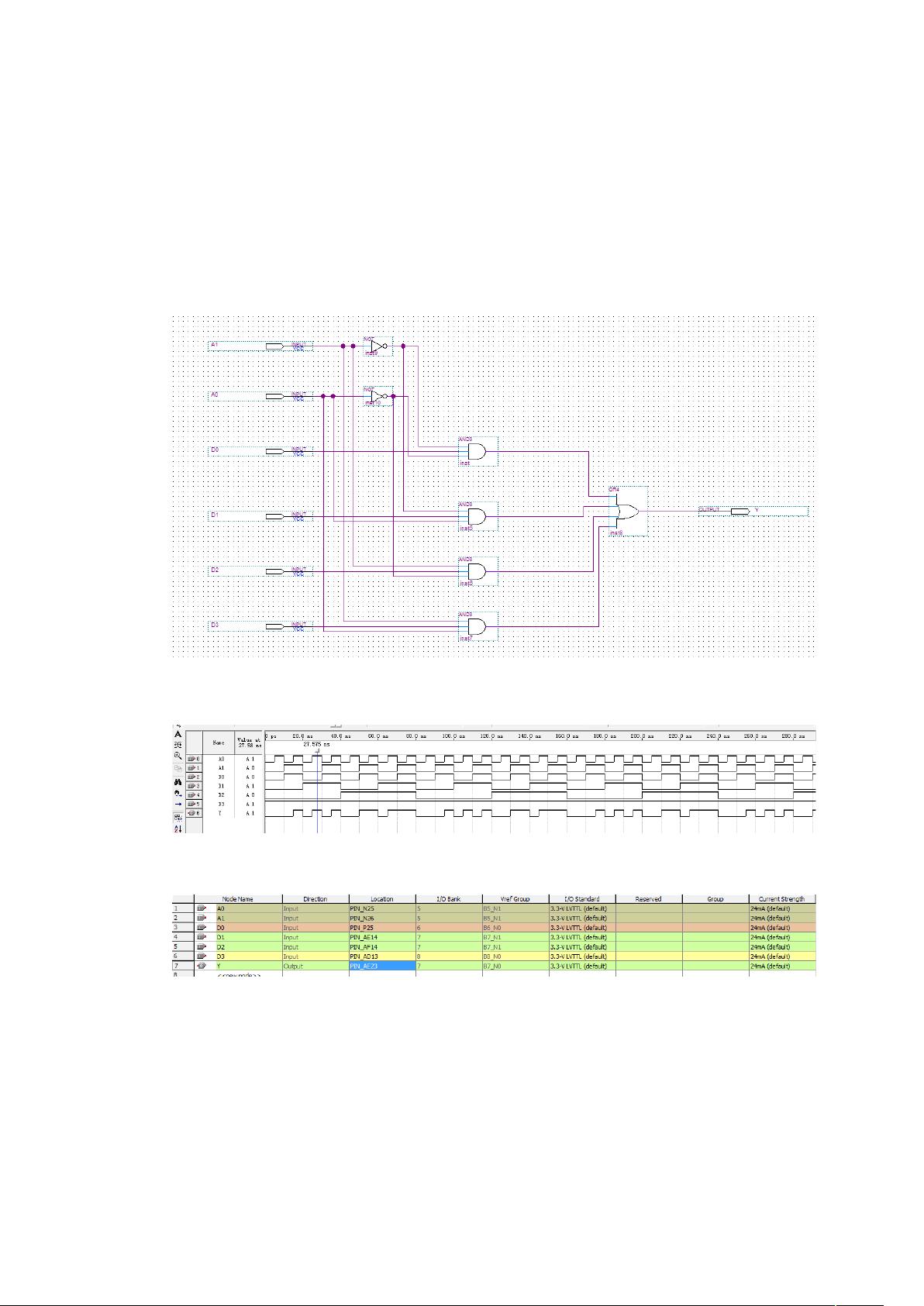

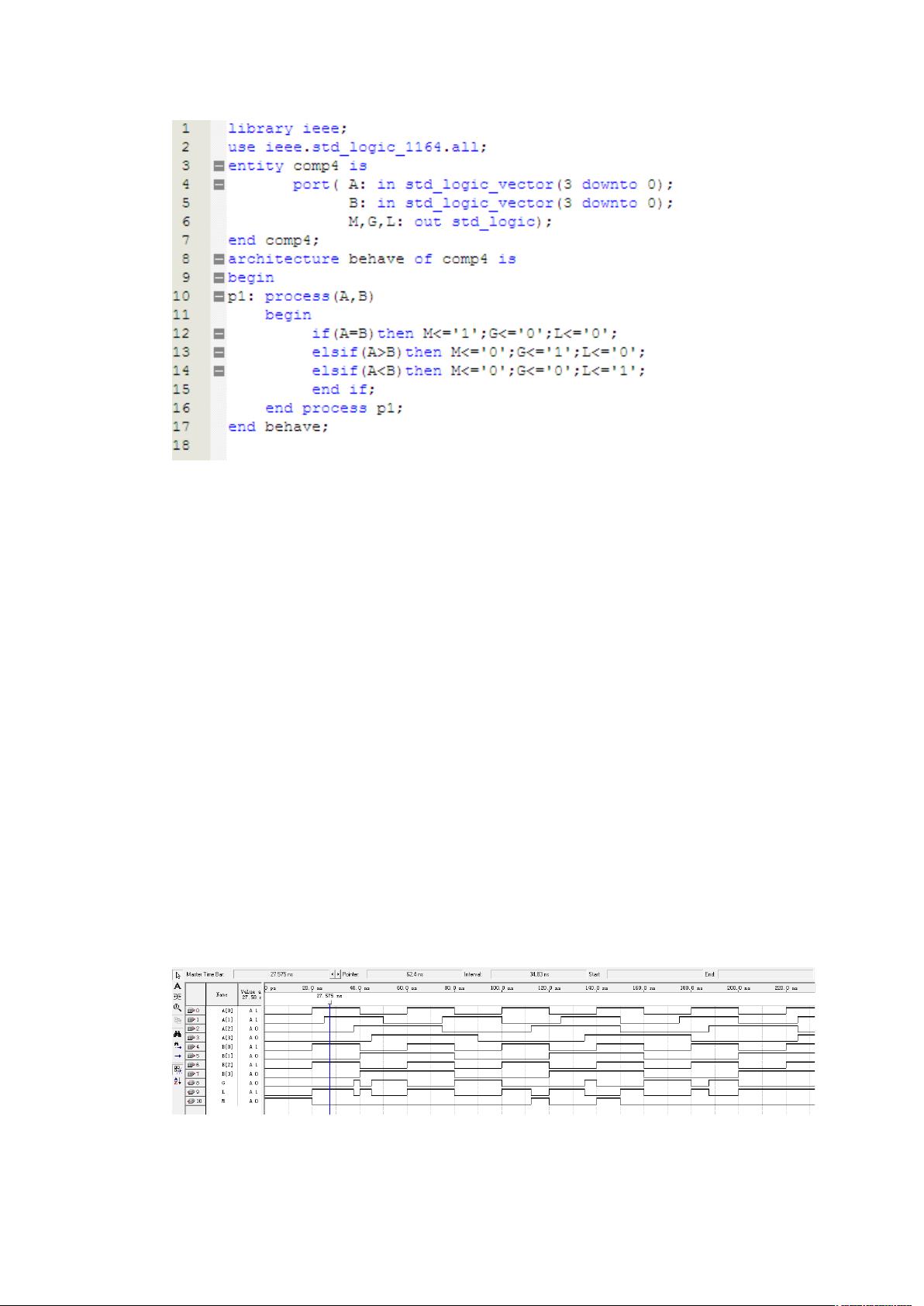

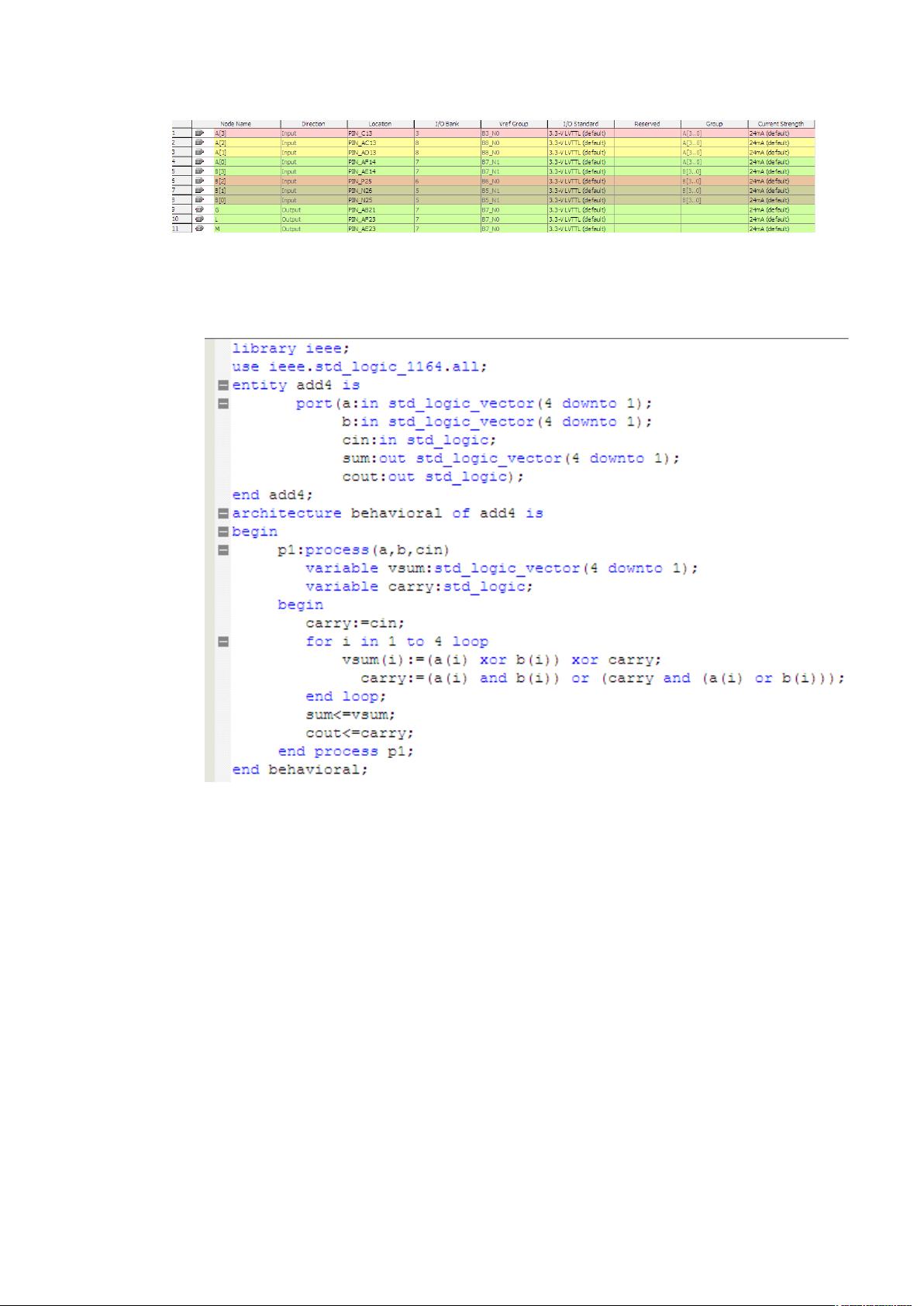

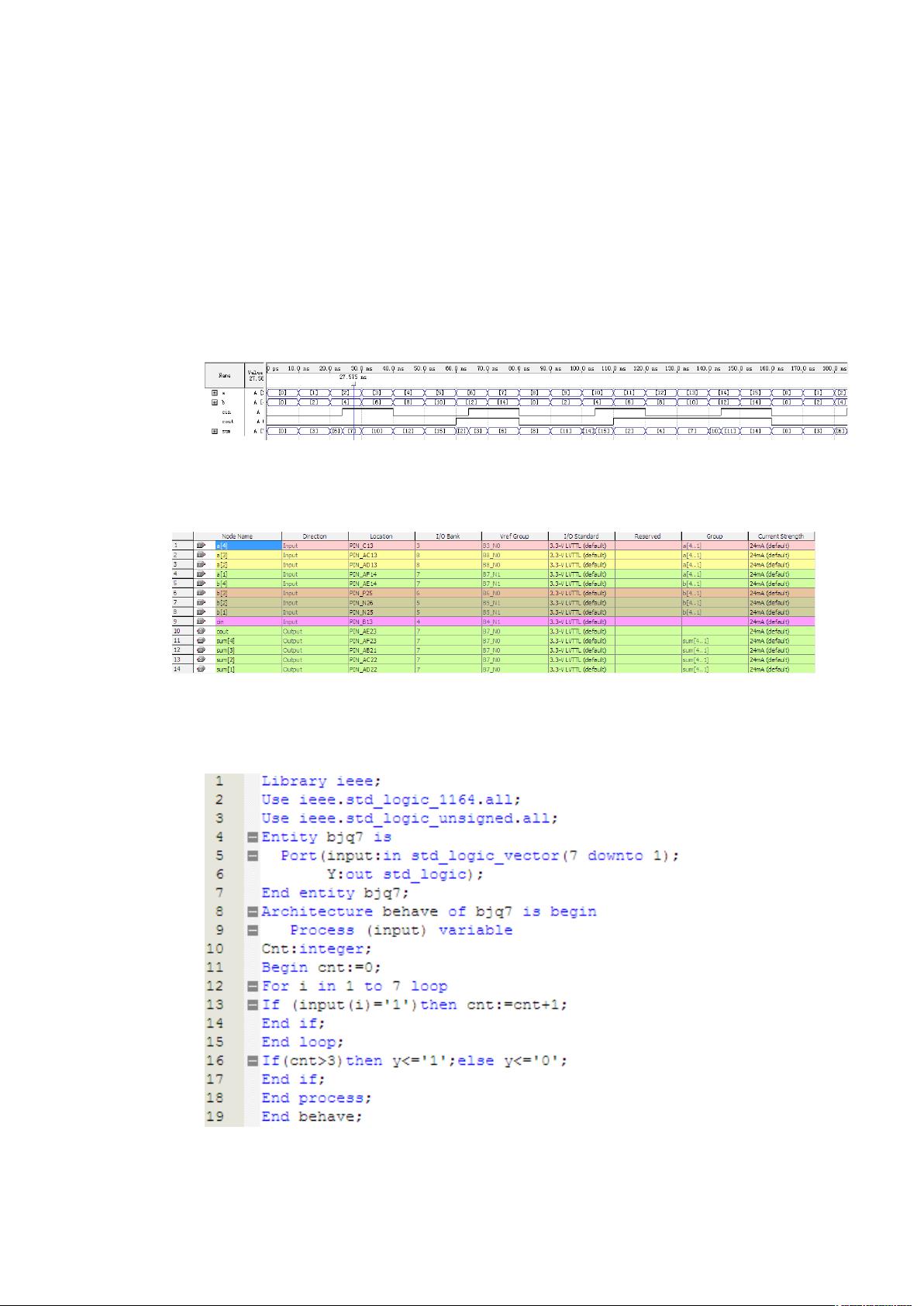

山东大学信息学院EDA基础实验总结报告,内容包含实验1 4选1数据选择器的设计;实验2 四位比较器;实验3 并行加法器设计;实验4 七人表决器;实验5 计数器设计;实验6 巴克码发生器;实验8 交通灯信号控制器设计; 根据给定的信息,我们可以将这份总结报告中的各个实验知识点进行详细的阐述。 ### 1. 14选1数据选择器的设计 #### 原理图 一个14选1的数据选择器通常由多个2选1的数据选择器组合而成。通过控制输入端(地址线)来选择其中一路作为输出。对于本实验,需要设计一个能够根据输入地址从14个不同的输入信号中选择一个作为输出的电路。 #### 仿真波形 在设计完成后,需要对数据选择器进行仿真测试,确保其功能正确无误。波形图可以直观地展示输入地址变化时,数据选择器如何选择正确的输出信号。 #### 管脚分配 管脚分配是指在硬件设计中为每个信号指定特定的物理引脚的过程。例如,对于14选1数据选择器,可能需要分配地址输入、数据输入和输出等引脚。 ### 2. 四位比较器 #### 源代码 ```vhdl library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity comp4 is Port ( A : in STD_LOGIC_VECTOR (3 downto 0); B : in STD_LOGIC_VECTOR (3 downto 0); M : out STD_LOGIC; G : out STD_LOGIC; L : out STD_LOGIC); end comp4; architecture behave of comp4 is begin p1: process (A, B) begin if (A = B) then M <= '1'; G <= '0'; L <= '0'; elsif (A > B) then M <= '0'; G <= '1'; L <= '0'; elsif (A < B) then M <= '0'; G <= '0'; L <= '1'; end if; end process p1; end behave; ``` 这段VHDL代码实现了一个四位数值比较器,能够判断两个四位二进制数之间的大小关系,并输出三个结果:等于(M)、大于(G)、小于(L)。 #### 仿真波形 仿真波形可以用来验证比较器的功能是否符合预期。通过观察不同输入组合下的输出变化,可以确保比较器的行为是正确的。 #### 管脚分配 管脚分配需要明确哪些物理引脚对应于比较器的输入输出信号。例如,`A`和`B`分别连接到输入端,而`M`、`G`、`L`则连接到输出端。 ### 3. 并行加法器设计 #### 源代码 ```vhdl library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity add4 is Port ( a : in STD_LOGIC_VECTOR (4 downto 1); b : in STD_LOGIC_VECTOR (4 downto 1); cin : in STD_LOGIC; sum : out STD_LOGIC_VECTOR (4 downto 1); cout : out STD_LOGIC); end add4; architecture behavioral of add4 is begin p1: process (a, b, cin) variable vsum : STD_LOGIC_VECTOR (4 downto 1); variable carry : STD_LOGIC; begin carry := cin; for i in 1 to 4 loop vsum(i) := (a(i) xor b(i)) xor carry; carry := (a(i) and b(i)) or (carry and (a(i) or b(i))); end loop; sum <= vsum; cout <= carry; end process p1; end behavioral; ``` 这段VHDL代码实现了一个并行加法器,它能够同时处理四个比特位的加法操作,并考虑到进位的影响。通过这种方式,可以在单个时钟周期内完成加法运算。 #### 仿真波形 仿真波形用于验证并行加法器的功能。通过对不同输入组合的测试,可以检查输出是否与预期相符。 #### 管脚分配 管脚分配指明了物理引脚与加法器内部信号之间的对应关系。例如,输入`a`和`b`分别代表被加数和加数,而`sum`和`cout`则表示加法结果及其产生的进位。 ### 4. 七人表决器 #### 源代码 ```vhdl library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity bjq7 is Port ( input : in STD_LOGIC_VECTOR (7 downto 1); Y : out STD_LOGIC); end entity bjq7; architecture behave of bjq7 is begin process (input) variable cnt : integer; begin cnt := 0; for i in 1 to 7 loop if (input(i) = '1') then cnt := cnt + 1; end if; end loop; if (cnt > 3) then Y <= '1'; else Y <= '0'; end if; end process; end behave; ``` 这段VHDL代码实现了一个七人表决器,当有超过半数的人投票支持某个决定时,输出为`1`,否则为`0`。 #### 仿真波形 仿真波形可以用来验证表决器的功能是否正确。通过模拟不同的投票情况,可以检查输出是否反映了多数人的意见。 #### 管脚分配 管脚分配定义了表决器的输入输出信号与物理引脚之间的对应关系。例如,`input`信号连接到七个投票人的输入端,而`Y`则表示最终的表决结果。 以上是对给定的几个实验内容的详细解析,包括了实验的设计原理、VHDL源代码、仿真波形以及管脚分配等方面的知识点。这些实验不仅帮助学生掌握了EDA的基本技能,也为后续更复杂的数字系统设计打下了坚实的基础。

剩余17页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- ap5030dn-openwrt-ath79-generic-huawei-ap5030dn-initramfs-kernel

- 华为AP无线接入控制器学习资料

- 金铲铲S13双城之战自动拿牌助手2.0

- Sigrity Power SI 仿真分析教程与实例分析.rar

- 基于Vue和JavaScript的掌上生活超市小程序配送解决方案设计源码

- 基于Java和安卓基础知识的简易记事本设计源码

- 基于SaToken轻量级Java权限认证的XrSaTokenVue Vue设计源码

- 基于Java语言的RxTool设计源码集合

- PHP性能检测扩展XHProf与FirePHP线上调试工具详解

- 基于Winsock的拦截与修改64位及32位封包的PacketEditor设计源码

信息提交成功

信息提交成功