没有合适的资源?快使用搜索试试~ 我知道了~

TI-DS90C124-Q1.pdf

温馨提示

试读

40页

FPD-Link解串器

资源推荐

资源详情

资源评论

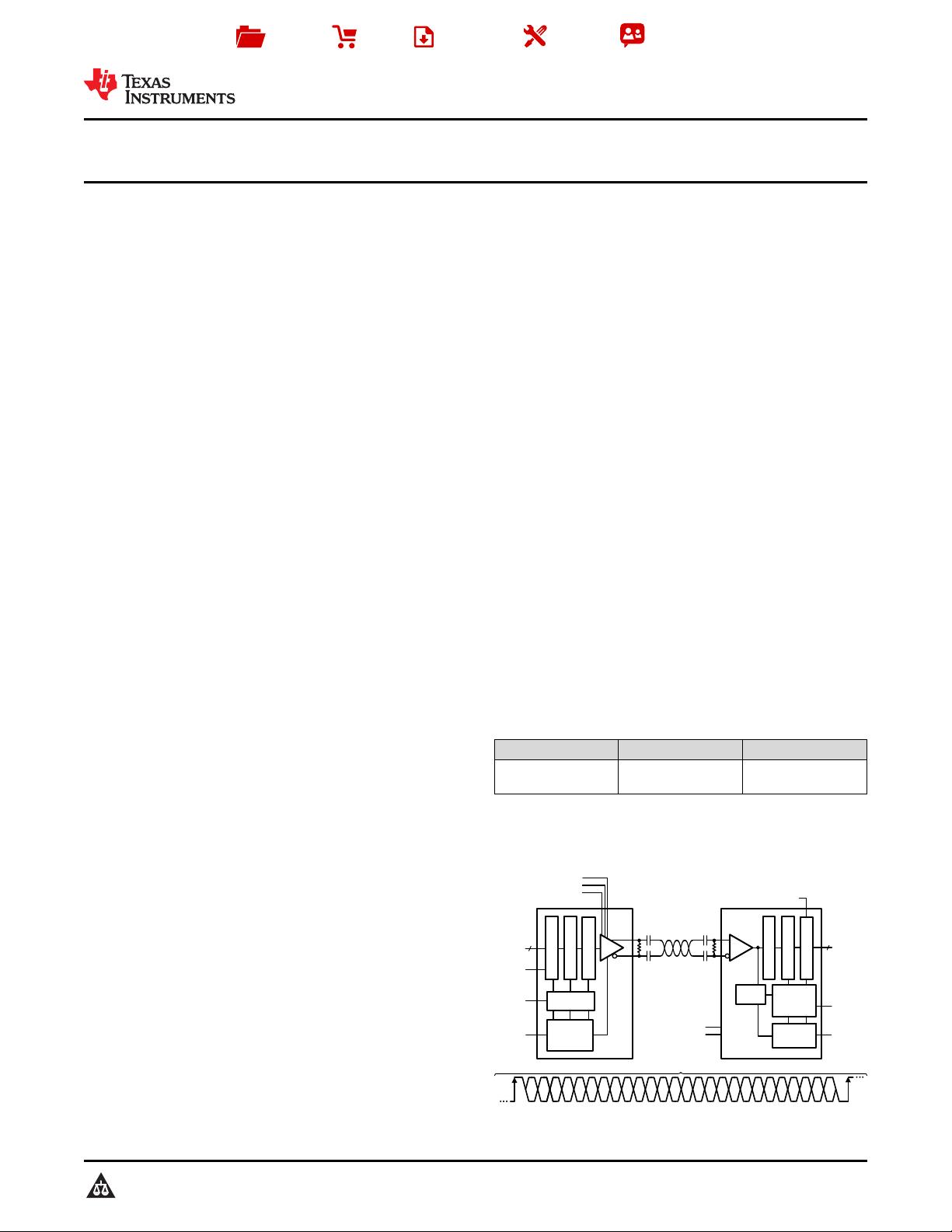

DEN

VODSEL

D

IN

TRFB

24

REN

RRFB

RPWDNB

TCLK

TPWDNB

SERIALIZER ± DS90C241

PLL

Timing

and

Control

D

OUT

-

R

T

=

100

:

R

T

=

100

:

R

IN

-

DESERIALIZER ± DS90C124

D

OUT

+ R

IN

+

PLL

Timing

and

Control

24

R

OUT

LOCK

RCLK

Clock

Recovery

Output Latch

Serial to Parallel

DC Balance Decode

Input Latch

Parallel to Serial

DC Balance Encode

CLK1

bit0

bit1

bit2

bit3

bit4

bit5

bit

6

bit

7

bit

8

bit

9

bit

10

bit

11

DCA

DCB

bit

12

bit

13

bit

14

bit

15

bit

16

bit

17

bit

18

bit

19

bit

20

bit

21

bit

22

bit

23

CLK0

PRE

Copyright © 2017, Texas Instruments Incorporated

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

DS90C124

,

DS90C241

SNLS209M –NOVEMBER 2005–REVISED JANUARY 2017

DS90C241 and DS90C124 5-MHz to 35-MHz DC-Balanced 24-Bit

FPD-Link II Serializer and Deserializer

1

1 Features

1

• 5-MHz to 35-MHz Clock Embedded and DC-

Balancing 24:1 and 1:24 Data Transmissions

• User Defined Pre-Emphasis Driving Ability

Through External Resistor on LVDS Outputs and

Capable to Drive Up to 10-Meter Shielded

Twisted-Pair Cable

• User-Selectable Clock Edge for Parallel Data on

Both Transmitter and Receiver

• Internal DC Balancing Encode and Decode

(Supports AC-Coupling Interface With No External

Coding Required)

• Individual Power-Down Controls for Both

Transmitter and Receiver

• Embedded Clock CDR (Clock and Data Recovery)

on Receiver and No External Source of Reference

Clock Required

• All Codes RDL (Random Data Lock) to Support

Live-Pluggable Applications

• LOCK Output Flag to Ensure Data Integrity at

Receiver Side

• Balanced T

SETUP

and T

HOLD

Between RCLK and

RDATA on Receiver Side

• PTO (Progressive Turnon) LVCMOS Outputs to

Reduce EMI and Minimize SSO Effects

• All LVCMOS Inputs and Control Pins Have

Internal Pulldown

• On-Chip Filters for PLLs on Transmitter and

Receiver

• Temperature Range: –40°C to 105°C

• Greater Than 8-kV HBM ESD Tolerant

• Meets AEC-Q100 Compliance

• Power Supply Range: 3.3 V ± 10%

• 48-Pin TQFP Package

2 Applications

• Automotive Central Information Displays

• Automotive Instrument Cluster Displays

• Automotive Heads-Up Displays

• Remote Camera-Based Driver Assistance

Systems

3 Description

The DS90C241 and DS90C124 chipset translates a

24-bit parallel bus into a fully transparent data and

control LVDS serial stream with embedded clock

information. This single serial stream simplifies

transferring a 24-bit bus over PCB traces or over

cable by eliminating the skew problems between

parallel data and clock paths. It saves system cost by

narrowing data paths, which in turn reduces PCB

layers, cable width, and connector size and pins.

The DS90C241 and DS90C124 incorporate LVDS

signaling on the high-speed I/O. LVDS provides a

low-power and low-noise environment for reliably

transferring data over a serial transmission path. By

optimizing the serializer output edge rate for the

operating frequency range, EMI is further reduced.

In addition, the device features pre-emphasis to boost

signals over longer distances using lossy cables.

Internal DC balanced encoding and decoding

supports AC-coupled interconnects.

Device Information

(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

DS90C124

DS90C241

TQFP (48) 7.00 mm x 7.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Block Diagram

2

DS90C124

,

DS90C241

SNLS209M –NOVEMBER 2005–REVISED JANUARY 2017

www.ti.com

Product Folder Links: DS90C124 DS90C241

Submit Documentation Feedback Copyright © 2005–2017, Texas Instruments Incorporated

Table of Contents

1 Features.................................................................. 1

2 Applications ........................................................... 1

3 Description ............................................................. 1

4 Revision History..................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 7

6.1 Absolute Maximum Ratings ..................................... 7

6.2 ESD Ratings.............................................................. 7

6.3 Recommended Operating Conditions....................... 7

6.4 Thermal Information.................................................. 8

6.5 Electrical Characteristics........................................... 8

6.6 Timing Requirements – Serializer............................. 9

6.7 Switching Characteristics – Serializer..................... 10

6.8 Switching Characteristics – Deserializer................. 10

6.9 Typical Characteristics............................................ 11

7 Parameter Measurement Information ................ 12

8 Detailed Description............................................ 17

8.1 Overview ................................................................. 17

8.2 Functional Block Diagram ....................................... 17

8.3 Feature Description................................................. 17

8.4 Device Functional Modes........................................ 20

9 Applications and Implementation ...................... 22

9.1 Application Information............................................ 22

9.2 Typical Application ................................................. 22

10 Power Supply Recommendations ..................... 27

11 Layout................................................................... 28

11.1 Layout Guidelines ................................................. 28

11.2 Layout Example .................................................... 29

12 Device and Documentation Support ................. 32

12.1 Documentation Support ........................................ 32

12.2 Related Links ........................................................ 32

12.3 Receiving Notification of Documentation Updates 32

12.4 Community Resources.......................................... 32

12.5 Trademarks........................................................... 32

12.6 Electrostatic Discharge Caution............................ 32

12.7 Glossary................................................................ 32

13 Mechanical, Packaging, and Orderable

Information ........................................................... 33

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision L (April 2013) to Revision M Page

• Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation

section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and

Mechanical, Packaging, and Orderable Information section.................................................................................................. 1

• Deleted Lead temperature, soldering (260°C maximum) from Absolute Maximum Ratings.................................................. 7

• Added Thermal Information table ........................................................................................................................................... 8

• Added Typical Characteristics (PCLK = 5 MHz and PCLK = 25 MHz plus pre-emphasis).................................................. 11

Changes from Revision K (April 2013) to Revision L Page

• Changed layout of National Semiconductor Data Sheet to TI format .................................................................................... 1

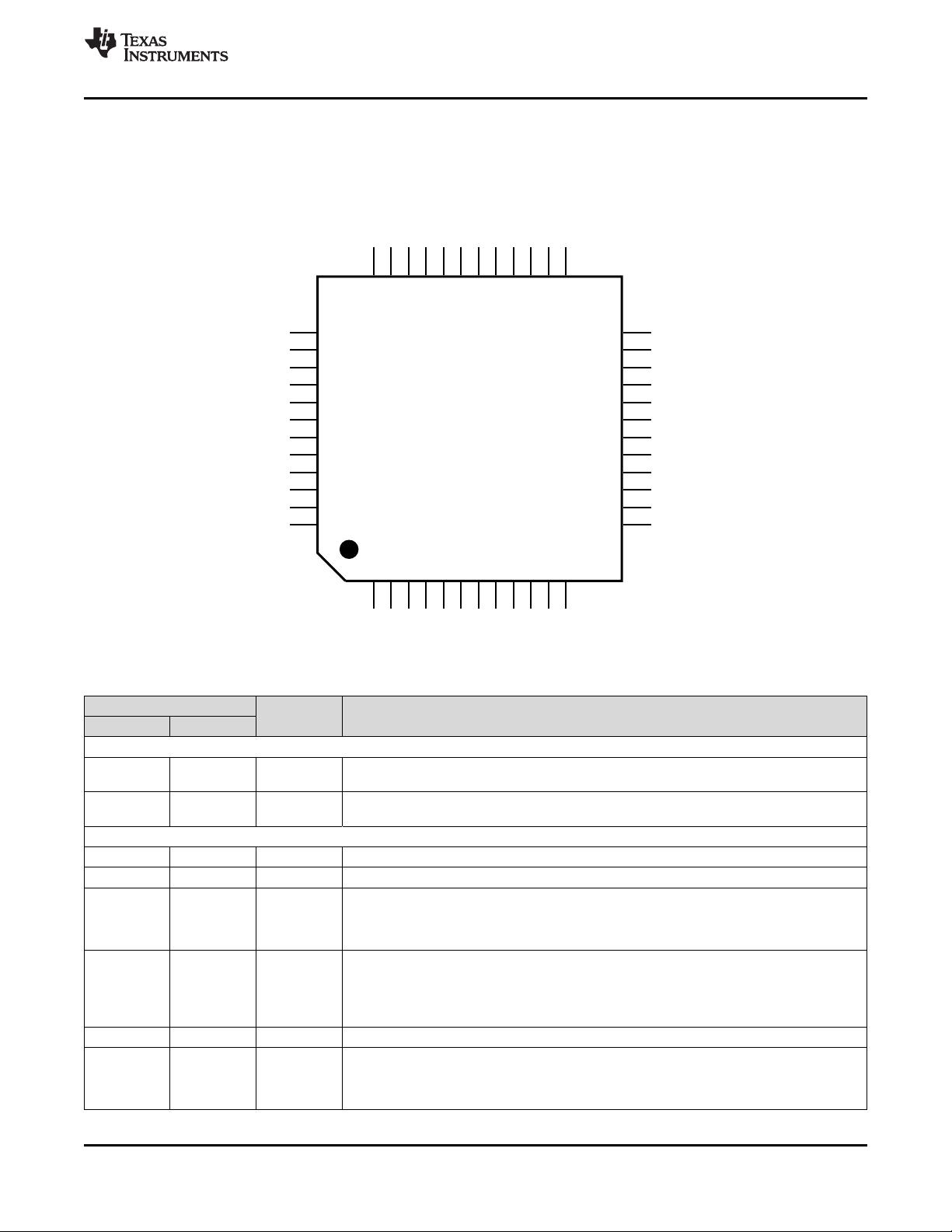

48DIN[19]

47DIN[18]

46DIN[17]

45DIN[16]

44DIN[15]

43

V

SS

IT

42

V

DD

IT

41DIN[14]

40DIN[13]

39DIN[12]

38DIN[11]

37DIN[10]

13

14

15

16

17

18

19

20

21

22

23

24

RESRVD

V

DD

PT1

V

SS

PT1

V

DD

PT0

V

SS

PT0

DEN

DOUT-

DOUT+

V

SS

DR

V

DD

DR

PRE

V

SS

12VODSEL

11TRFB

10TCLK

9TPWDNB

8DCBOFF

7

V

DD

L

6

V

SS

L

5DCAOFF

4DIN[23]

3DIN[22]

2DIN[21]

1DIN[20]

25

26

27

28

29

30

31

32

33

34

35

36

DIN[0]

DIN[1]

DIN[2]

DIN[3]

DIN[4]

V

DD

T

V

SS

T

DIN[5]

DIN[6]

DIN[7]

DIN[8]

DIN[9]

DS90C241

48 PIN TQFP

3

DS90C124

,

DS90C241

www.ti.com

SNLS209M –NOVEMBER 2005–REVISED JANUARY 2017

Product Folder Links: DS90C124 DS90C241

Submit Documentation FeedbackCopyright © 2005–2017, Texas Instruments Incorporated

(1) G = Ground, I = Input, O = Output, P = Power

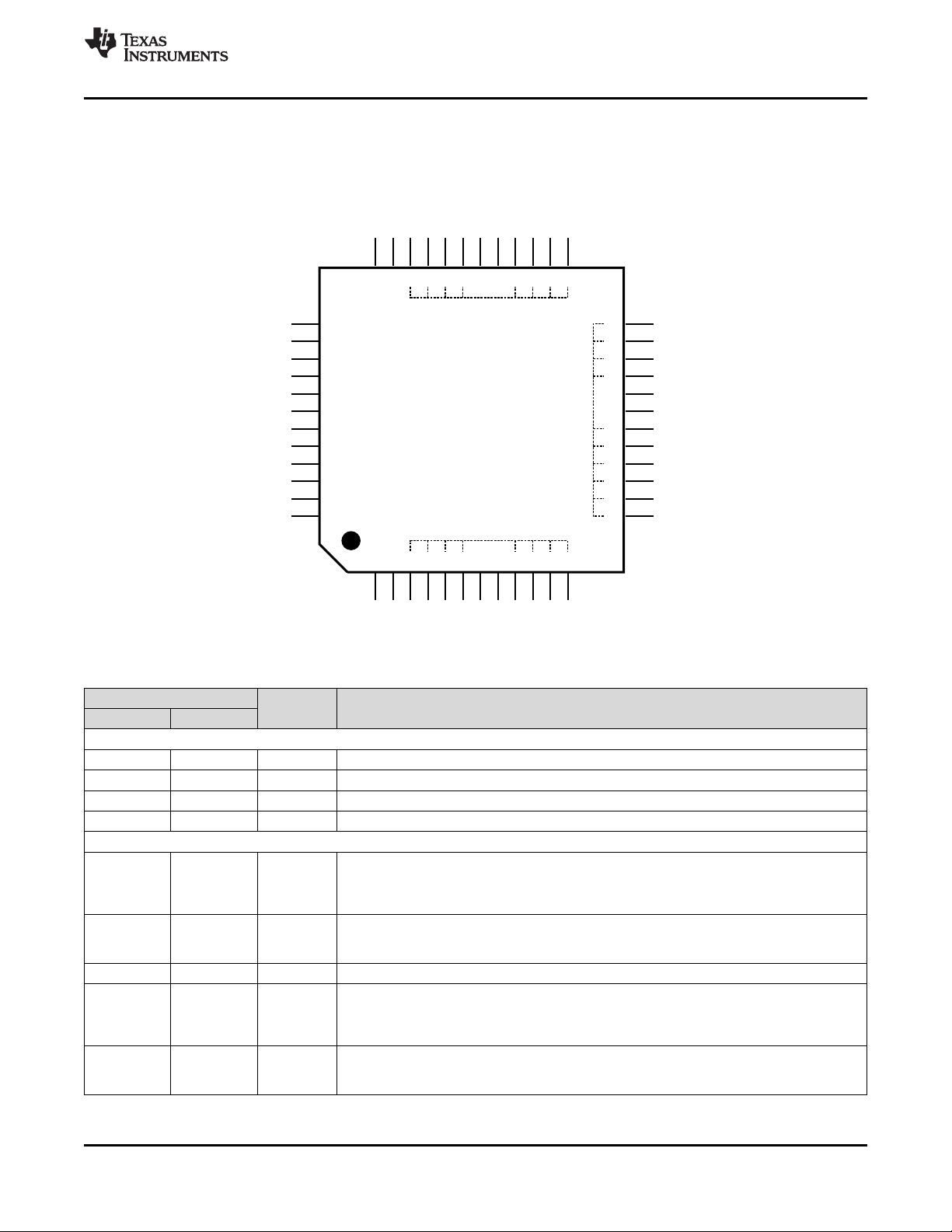

5 Pin Configuration and Functions

DS90C241 Serializer PFB Package

48-Pin TQFP

Top View

Pin Functions – DS90C241 Serializer

PIN

TYPE

(1)

DESCRIPTION

NAME NO.

LVCMOS PARALLEL INTERFACE PINS

DIN[23:0]

4-1, 48-44,

41-32, 29-25

I LVCMOS, Transmitter parallel interface data input pins. Tie LOW if unused, do not float.

TCLK 10 I

LVCMOS, Transmitter parallel interface clock input pin. Strobe edge set by TRFB

configuration pin.

CONTROL AND CONFIGURATION PINS

DCAOFF 5 I LVCMOS, Reserved. This pin must be tied LOW.

DCBOFF 8 I LVCMOS, Reserved. This pin must be tied LOW.

DEN 18 I

LVCMOS, Transmitter data enable.

DEN = H; LVDS driver outputs are enabled (ON).

DEN = L; LVDS driver outputs are disabled (OFF), Transmitter LVDS driver D

OUT

(±) outputs

are in TRI-STATE, PLL still operational and locked to TCLK.

PRE 23 I

LVCMOS, Pre-emphasis level select.

PRE = NC (No Connect); Pre-emphasis is disabled (OFF).

Pre-emphasis is active when input is tied to VSS through external resistor R

PRE

. Resistor

value determines pre-emphasis level. Recommended value R

PRE

≥ 3 kΩ; I

max

= [(1.2/R) ×

20], R

min

= 3 kΩ

RESRVD 13 I LVCMOS, Reserved. This pin must be tied LOW.

TPWDNB 9 I

LVCMOS, Transmitter power down bar.

TPWDNB = H; Transmitter is enabled and ON

TPWDNB = L; Transmitter is in power down mode (Sleep), LVDS driver D

OUT

(±) outputs are

in TRI-STATE stand-by mode, PLL is shutdown to minimize power consumption.

4

DS90C124

,

DS90C241

SNLS209M –NOVEMBER 2005–REVISED JANUARY 2017

www.ti.com

Product Folder Links: DS90C124 DS90C241

Submit Documentation Feedback Copyright © 2005–2017, Texas Instruments Incorporated

Pin Functions – DS90C241 Serializer (continued)

PIN

TYPE

(1)

DESCRIPTION

NAME NO.

TRFB 11 I

LVCMOS, Transmitter clock edge select pin.

TRFB = H; Parallel interface data is strobed on the rising clock edge.

TRFB = L; Parallel interface data is strobed on the falling clock edge.

VODSEL 12 I

LVCMOS, VOD Level select

VODSEL = L; LVDS driver output is approximately ± 400 mV (R

L

= 100 Ω)

VODSEL = H; LVDS driver output is approximately ± 750 mV (R

L

= 100 Ω)

For normal applications, set this pin LOW. For long cable applications where a larger VOD is

required, set this pin HIGH.

LVDS SERIAL INTERFACE PINS

DOUT− 19 O

LVDS, Transmitter LVDS inverted (-) output

This output is intended to be loaded with a 100-Ω load to the D

OUT-

pin. The interconnect

must be AC-coupled to this pin with a 100-nF capacitor.

DOUT+ 20 O

LVDS, Transmitter LVDS true (+) output.

This output is intended to be loaded with a 100-Ω load to the D

OUT+

pin. The interconnect

must be AC-coupled to this pin with a 100-nF capacitor.

POWER OR GROUND PINS

VDDDR 22 P VDD, Analog voltage supply, LVDS output power

VDDIT 42 P VDD, Digital voltage supply, Tx input power

VDDL 7 P VDD, Digital voltage supply, Tx logic power

VDDPT0 16 P VDD, Analog voltage supply, VCO power

VDDPT1 14 P VDD, Analog voltage supply, PLL power

VDDT 30 P VDD, Digital voltage supply, Tx serializer power

VSS 24 G ESD ground

VSSDR 21 G Analog ground, LVDS output ground

VSSIT 43 G Digital ground, Tx input ground

VSSL 6 G Digital ground, Tx logic ground

VSSPT0 17 G Analog ground, VCO ground

VSSPT1 15 G Analog ground, PLL ground

VSST 31 G Digital ground, Tx serializer ground

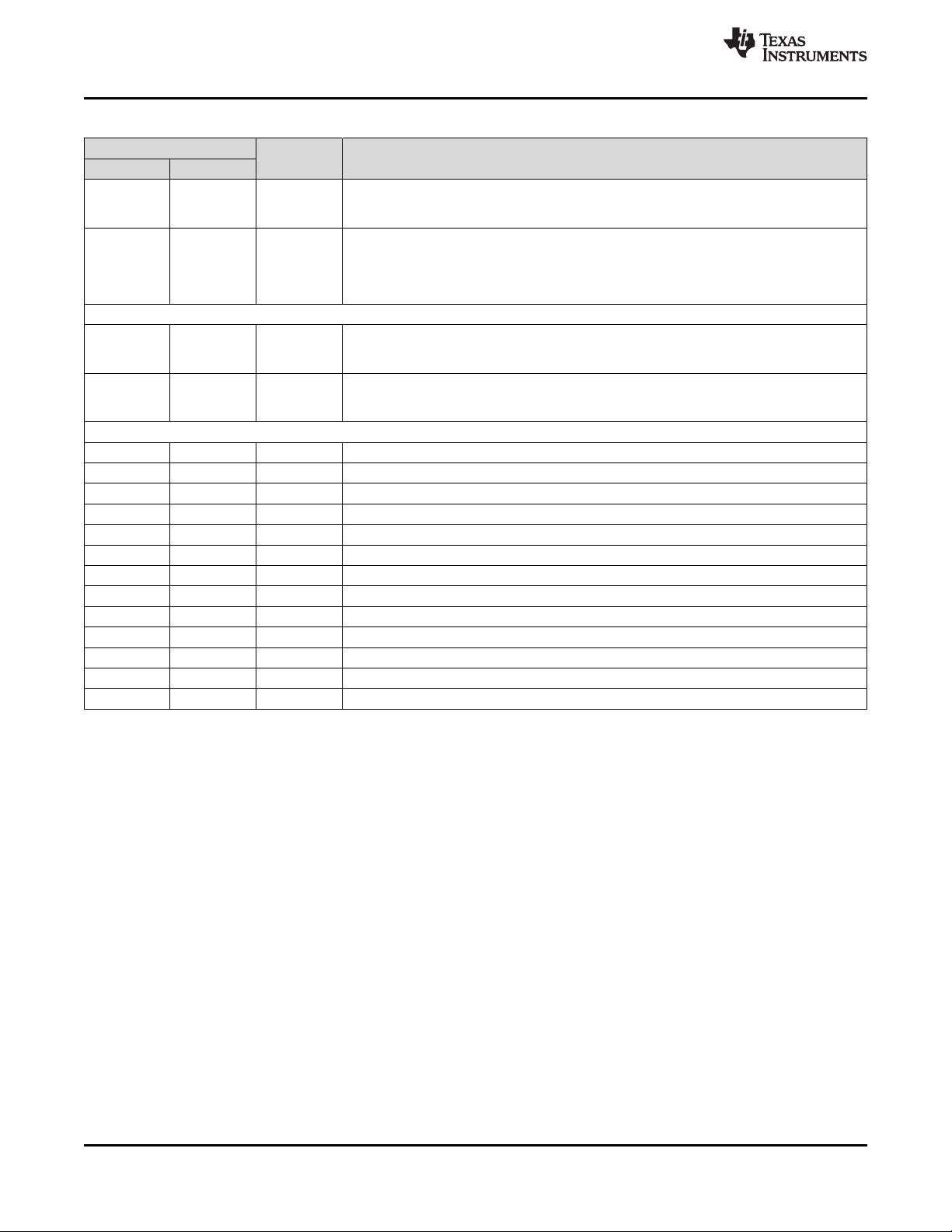

48REN

47

V

DD

PR0

46

V

SS

PR0

45

V

DD

PR1

44

V

SS

PR1

43RRFB

42RIN-

41RIN+

40

V

SS

IR

39

V

DD

IR

38

V

SS

R1

37

V

DD

R1

13

14

15

16

17

18

19

20

21

22

23

24

ROUT[15]

ROUT[14]

ROUT[13]

ROUT[12]

LOCK

RCLK

V

SS

OR2

V

DD

OR2

ROUT[11]

ROUT[10]

ROUT[9]

ROUT[8]

12ROUT[16]

11ROUT[17]

10ROUT[18]

9ROUT[19]

8

V

SS

OR3

7

V

DD

OR3

6ROUT[20]

5ROUT[21]

4ROUT[22]

3ROUT[23]

2RESRVD

1RPWDNB

25

26

27

28

29

30

31

32

33

34

35

36

ROUT[7]

ROUT[6]

ROUT[5]

ROUT[4]

V

SS

OR1

V

DD

OR1

ROUT[3]

ROUT[2]

ROUT[1]

ROUT[0]

V

SS

R0

V

DD

R0

DS90C124

48 PIN TQFP

PTO GROUP 3

PTO GROUP 1

PTO GROUP 2

5

DS90C124

,

DS90C241

www.ti.com

SNLS209M –NOVEMBER 2005–REVISED JANUARY 2017

Product Folder Links: DS90C124 DS90C241

Submit Documentation FeedbackCopyright © 2005–2017, Texas Instruments Incorporated

(1) G = Ground, I = Input, O = Output, P = Power

DS90C124 Deserializer PFB Package

48-Pin TQFP

Top View

Pin Functions – DS90C124 Deserializer

PIN

TYPE

(1)

DESCRIPTION

NAME NO.

LVCMOS PARALLEL INTERFACE PINS

RCLK 18 O LVCMOS, Parallel interface clock output pin. Strobe edge set by RRFB configuration pin.

ROUT[7:0] 25-28, 31-34 O LVCMOS, Receiver LVCMOS level outputs – Group 1

ROUT[15:8] 13-16, 21-24 O LVCMOS, Receiver LVCMOS level outputs – Group 2

ROUT[23:16] 3-6, 9-12 O LVCMOS, Receiver LVCMOS level outputs – Group 3

CONTROL AND CONFIGURATION PINS

REN 48 I

LVCMOS, Receiver data enable

REN = H; R

OUT

[23:0] and RCLK are enabled (ON).

REN = L; R

OUT

[23:0] and RCLK are disabled (OFF), receiver R

OUT

[23:0] and RCLK outputs

are in TRI-STATE, PLL still operational and locked to TCLK.

LOCK 17 O

LVCMOS, LOCK indicates the status of the receiver PLL

LOCK = H; receiver PLL is locked

LOCK = L; receiver PLL is unlocked, R

OUT

[23:0] and RCLK are TRI-STATED

RESRVD 2 I LVCMOS, Reserved. This pin must be tied LOW.

RPWDNB 1 I

LVCMOS, Receiver power down bar.

RPWDNB = H; Receiver is enabled and ON

RPWDNB = L; Receiver is in power down mode (Sleep), R

OUT

[23:0], RCLK, and LOCK are in

TRI-STATE standby mode, PLL is shutdown to minimize power consumption.

RRFB 43 I

LVCMOS, Receiver clock edge select pin.

RRFB = H; R

OUT

LVCMOS outputs strobed on the rising clock edge.

RRFB = L; R

OUT

LVCMOS outputs strobed on the falling clock edge.

剩余39页未读,继续阅读

资源评论

qq_335607272023-02-02#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

qq_335607272023-02-02#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 m0_745259962023-02-02#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

m0_745259962023-02-02#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

不觉明了

- 粉丝: 3102

- 资源: 5337

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Screenshot_20240427_031602.jpg

- 网页PDF_2024年04月26日 23-46-14_QQ浏览器网页保存_QQ浏览器转格式(6).docx

- 直接插入排序,冒泡排序,直接选择排序.zip

- 在排序2的基础上,再次对快排进行优化,其次增加快排非递归,归并排序,归并排序非递归版.zip

- 实现了7种排序算法.三种复杂度排序.三种nlogn复杂度排序(堆排序,归并排序,快速排序)一种线性复杂度的排序.zip

- 冒泡排序 直接选择排序 直接插入排序 随机快速排序 归并排序 堆排序.zip

- 课设-内部排序算法比较 包括冒泡排序、直接插入排序、简单选择排序、快速排序、希尔排序、归并排序和堆排序.zip

- Python排序算法.zip

- C语言实现直接插入排序、希尔排序、选择排序、冒泡排序、堆排序、快速排序、归并排序、计数排序,并带图详解.zip

- 常用工具集参考用于图像等数据处理

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功