4

DP83TC811R-Q1

ZHCSHX5A –NOVEMBER 2017–REVISED MARCH 2018

www.ti.com.cn

Copyright © 2017–2018, Texas Instruments Incorporated

(1) When pins are unused, follow the recommended connection requirements provided in the table above. If pins do not have required

termination, they may be left floating.

(2) Pin Type:

I = Input

O = Output

IO = Input/Output

OD = Open Drain

PD = Internal pulldown

PU = Internal pullup

S = Bootstrap configuration pin (all configuration pins have weak internal pullups or pulldowns)

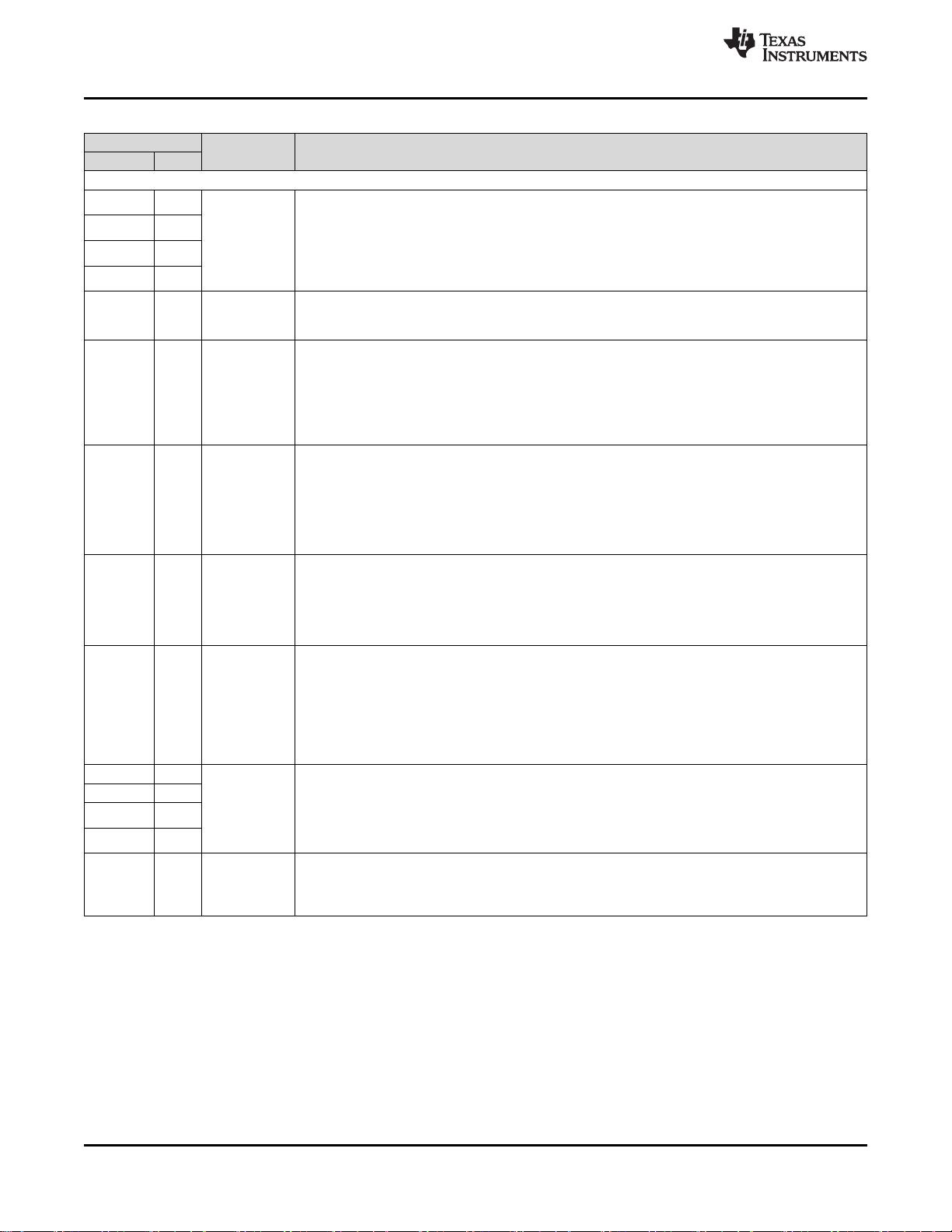

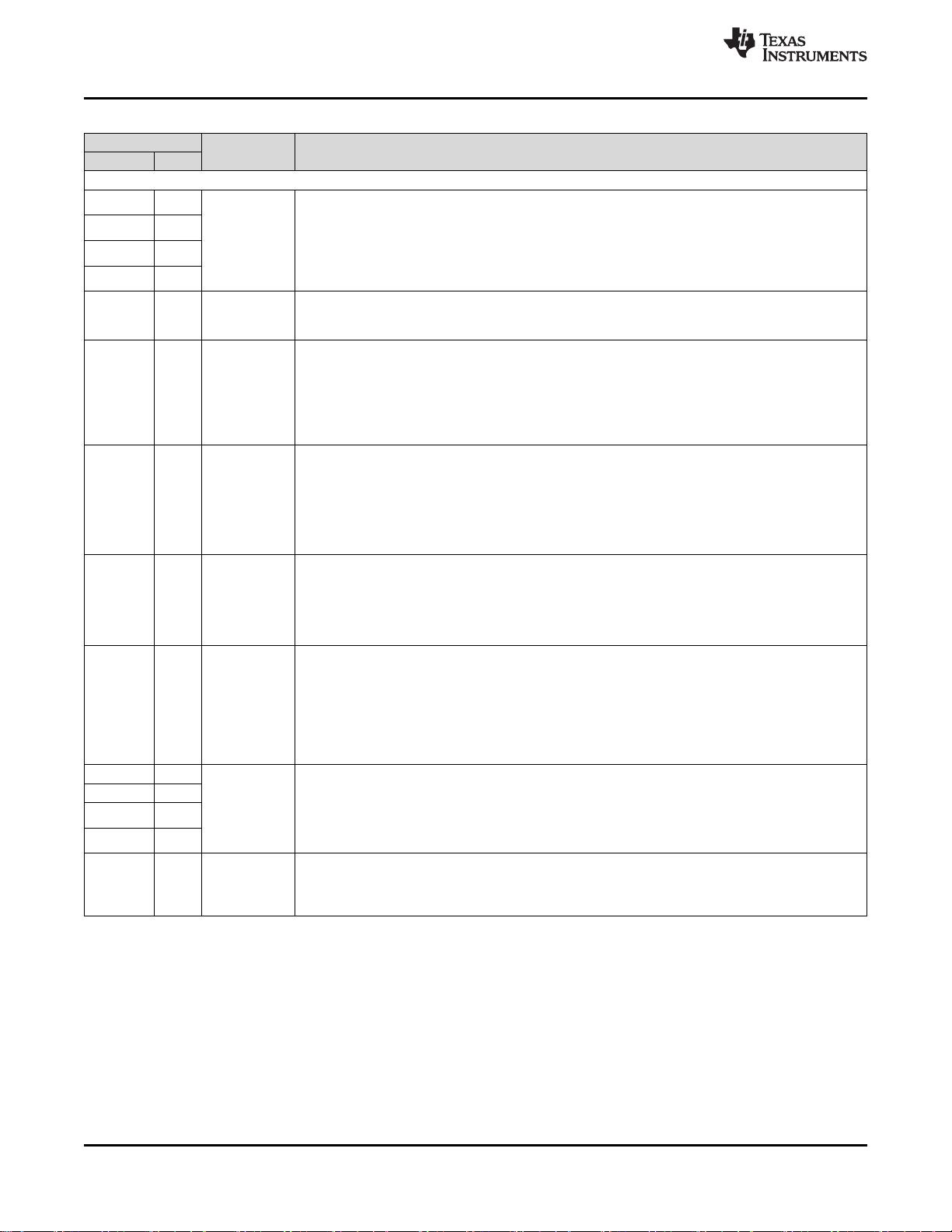

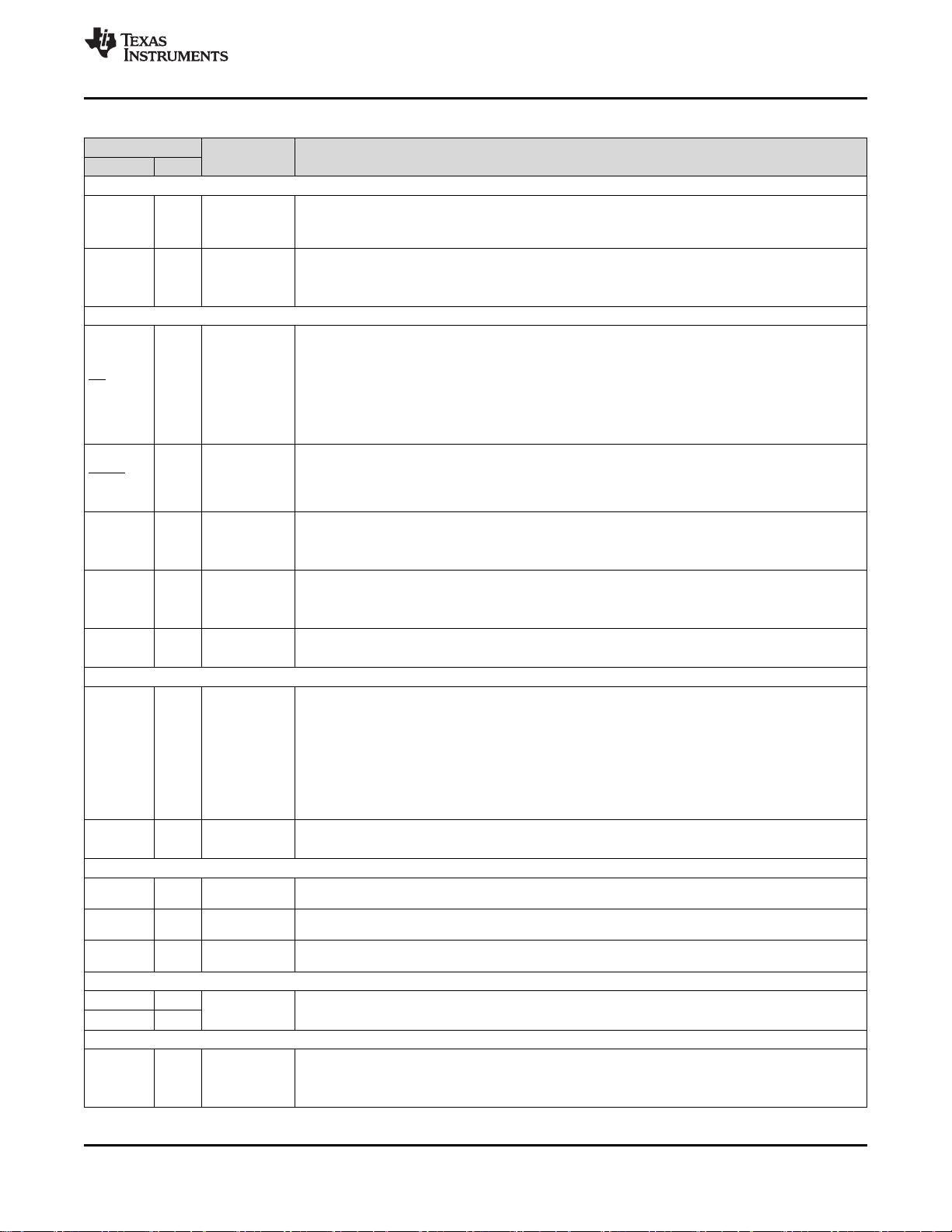

Pin Functions

(1)

PIN

STATE

(2)

DESCRIPTION

NAME NO.

MAC INTERFACE

RX_D3

23

S, PD, O

Receive Data: Symbols received on the cable are decoded and transmitted out of these pins

synchronous to the rising edge of RX_CLK. They contain valid data when RX_DV is asserted. A data

nibble, RX_D[3:0], is transmitted in MII and RGMII modes. 2 bits; RX_D[1:0], are transmitted in RMII

mode. RX_D[3:2] are not used when in RMII mode.

If the PHY is bootstrapped to RMII Master mode, a 50-MHz clock reference is automatically outputted

on RX_D3. This clock should be fed to the MAC.

RX_D2

24

RX_D1

25

RX_D0

26

RX_CLK 27 O

Receive Clock: In MII and RGMII modes, the receive clock provides a 25-MHz reference clock.

Unused in RMII mode

RX_ER 14 S, PD, O

Receive Error: In MII and RMII modes, this pin indicates a receive error symbol has been detected

within a received packet. In MII mode, RX_ER is asserted high synchronously to the rising edge of

RX_CLK. In RMII mode, RX_ER is asserted high synchronously to the rising edge of the reference

clock. This pin is not required to be used by the MAC in MII or RMII because the PHY will

automatically corrupt data on a receive error.

Unused in RGMII mode

RX_DV

CRS_DV

RX_CTRL

15 S, PD, O

Receive Data Valid: This pin indicates when valid data is presented on RX_D[3:0] for MII mode.

Carrier Sense Data Valid: This pin combines carrier sense and data valid into an asynchronous

signal. When CRS_DV is asserted, data is presented on RX_D[1:0] in RMII mode.

RGMII Receive Control: Receive control combines receive data valid indication and receive error

indication into a single signal. RX_DV is presented on the rising edge of RX_CLK and RX_ER is

presented on the falling edge of RX_CLK.

TX_CLK 28 PD, I, O

Transmit Clock: In MII mode, the transmit clock is a 25-MHz output and has constant phase

referenced to the reference clock. In RGMII mode, this clock is sourced from the MAC layer to the

PHY. A 25-MHz clock should be provided (not required to have constant phase to the reference clock

unless synchronous RGMII is enabled in ).

Unused in RMII mode

TX_EN

TX_CTRL

29 PD, I

Transmit Enable: In MII mode, transmit enable is presented prior to the rising edge of the transmit

clock. TX_EN indicates the presence of valid data inputs on TX_D[3:0]. In RMII mode, transmit

enable is presented prior to the rising edge of the reference clock. TX_EN indicates the presence of

valid data inputs on TX_D[1:0].

RGMII Transmit Control: Transmit control combines transmit enable and transmit error indication

into a single signal. TX_EN is presented prior to the rising edge of TX_CLK; TX_ER is presented

prior to the falling edge of TX_CLK.

TX_D3 30

PD, I

Transmit Data: In MII and RGMII modes, the transmit data nibble, TX_D[3:0], is received from the

MAC prior to the rising edge of TX_CLK. In RMII mode, TX_D[1:0] is received from the MAC prior to

the rising edge of the reference clock. TX_D[3:2] are not used in RMII mode.

TX_D2 31

TX_D1

32

TX_D0

33

TX_ER 34 PD, I

Transmit Error: In MII mode, this pin indicates a transmit error symbol has been detected within a

transmitted packet. TX_ER is received prior to the rising edge of TX_CLK.

Unused in RMII and RGMII modes

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功