没有合适的资源?快使用搜索试试~ 我知道了~

TI-TMS28F200BZB.pdf

需积分: 0 0 下载量 142 浏览量

2022-12-10

23:13:45

上传

评论 4

收藏 406KB PDF 举报

温馨提示

试读

29页

TI-TMS28F200BZB.pdf

资源详情

资源评论

TMS28F200BZT, TMS28F200BZB

262144 BY 8-BIT/131072 BY 16-BIT

BOOT-BLOCK FLASH MEMORIES

SMJS200E – JUNE 1994 – REVISED JANUARY 1998

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

D

Organization... 262144 by 8 bits

131072 by 16 bits

D

Array-Blocking Architecture

– Two 8K-Byte Parameter Blocks

– One 96K-Byte Main Block

– One 128K-Byte Main Block

– One 16K-Byte Protected Boot Block

– Top or Bottom Boot Locations

D

All Inputs/Outputs TTL Compatible

D

Maximum Access/Minimum Cycle Time

V

CC

± 10%

’28F200BZx70 70 ns

’28F200BZx80 80 ns

’28F200BZx90 90 ns

(x = top (T) or bottom (B) boot-block

configurations ordered)

D

10000 Program/Erase-Cycles

D

Three Temperature Ranges

– Commercial...0°C to 70°C

– Extended...– 40°C to 85°C

– Automotive...– 40°C to 125°C

D

Low Power Dissipation (V

CC

= 5.5 V)

– Active Write . . . 330 mW (Byte-Write)

– Active Read...330 mW (Byte-Read)

– Active Write . . . 358 mW (Word-Write)

– Active Read...330 mW (Word-Read)

– Block-Erase...165 mW

– Standby...0.55 mW (CMOS-Input

Levels)

– Deep Power-Down Mode...0.0066 mW

D

Fully Automated On-Chip Erase and

Word/Byte-Program Operations

D

Write-Protection for Boot Block

D

Industry-Standard Command State Machine

(CSM)

– Erase-Suspend/Resume

– Algorithm-Selection Identifier

description

The TMS28F200BZx is a 262144 by 8-bit/131072 by 16-bit (2097152-bit), boot-block flash memory that can

be electrically block-erased and reprogrammed. The TMS28F200BZx is organized in a blocked architecture

consisting of one 16K-byte protected boot block, two 8K-byte parameter blocks, one 96K-byte main block, and

one 128K-byte main block. The device can be ordered with either a top or bottom boot-block configuration.

Operation as a 256K-by 8-bit or a 128K-by16-bit organization is user-definable.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

23

V

CC

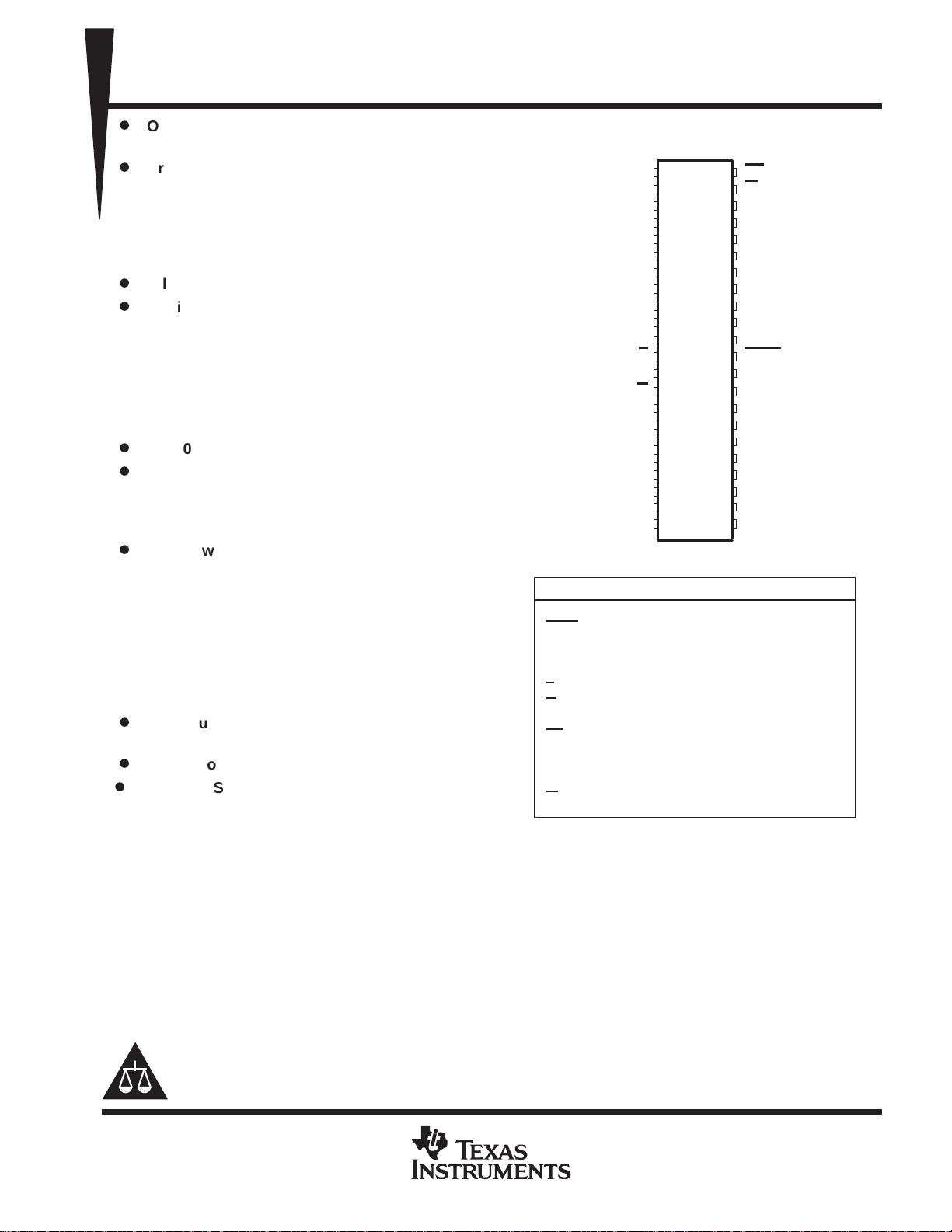

PIN NOMENCLATURE

A0–A16 Address Inputs

BYTE Byte Enable

DQ0–DQ14 Data In/ Out

DQ15/A

–1

Data In/ Out (word-wide mode),

Low-Order Address (byte-wide mode)

E

Chip Enable

G

Output Enable

NC No Internal Connection

RP

Reset/Deep Power-Down

V

CC

5-V Power Supply

V

PP

12-V Power Supply for Program/ Erase

V

SS

Ground

W

Write Enable

DBJ PACKAGE

(TOP VIEW)

V

PP

NC

NC

A7

A6

A5

A4

A3

A2

A1

A0

E

V

SS

G

DQ0

DQ8

DQ1

DQ9

DQ2

DQ10

RP

W

A8

A9

A10

A11

A12

A13

A14

A15

A16

BYTE

V

SS

DQ15/A

–1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

19

20

26

25

DQ3

DQ11

DQ4

21

22

24

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright 1998, Texas Instruments Incorporated

TMS28F200BZT, TMS28F200BZB

262144 BY 8-BIT/131072 BY 16-BIT

BOOT-BLOCK FLASH MEMORIES

SMJS200E – JUNE 1994 – REVISED JANUARY 1998

2

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

description (continued)

Embedded program and block-erase functions are fully automated by an on-chip write state machine (WSM),

simplifying these operations and relieving the system microcontroller of these secondary tasks. WSM status

can be monitored by the on-chip status register to determine the progress of program/erase tasks. The device

features user-selectable block-erasure.

The TMS28F200BZx flash memory is offered in a 44-pin PSOP. It is available in two temperature ranges:

0°C to 70°C and – 40°C to 85°C.

device symbol nomenclature

Temperature Range Designator

L= 0°Cto70°C

E = – 40°Cto85°C

Package Designator

DBJ = Plastic Small-Outline Package

Program/Erase Endurance

B = 10000 Cycles

Speed Designator

70 = 70 ns (±10% V

CC

tolerance)

80 = 80 ns (±10% V

CC

tolerance)

90 = 90 ns (±10% V

CC

tolerance)

70 B DBJ LTMS28F200BZT

Boot-Block Location Indicator

T = Top Location

B = Bottom Location

TMS28F200BZT, TMS28F200BZB

262144 BY 8-BIT/131072 BY 16-BIT

BOOT-BLOCK FLASH MEMORIES

SMJS200E – JUNE 1994 – REVISED JANUARY 1998

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

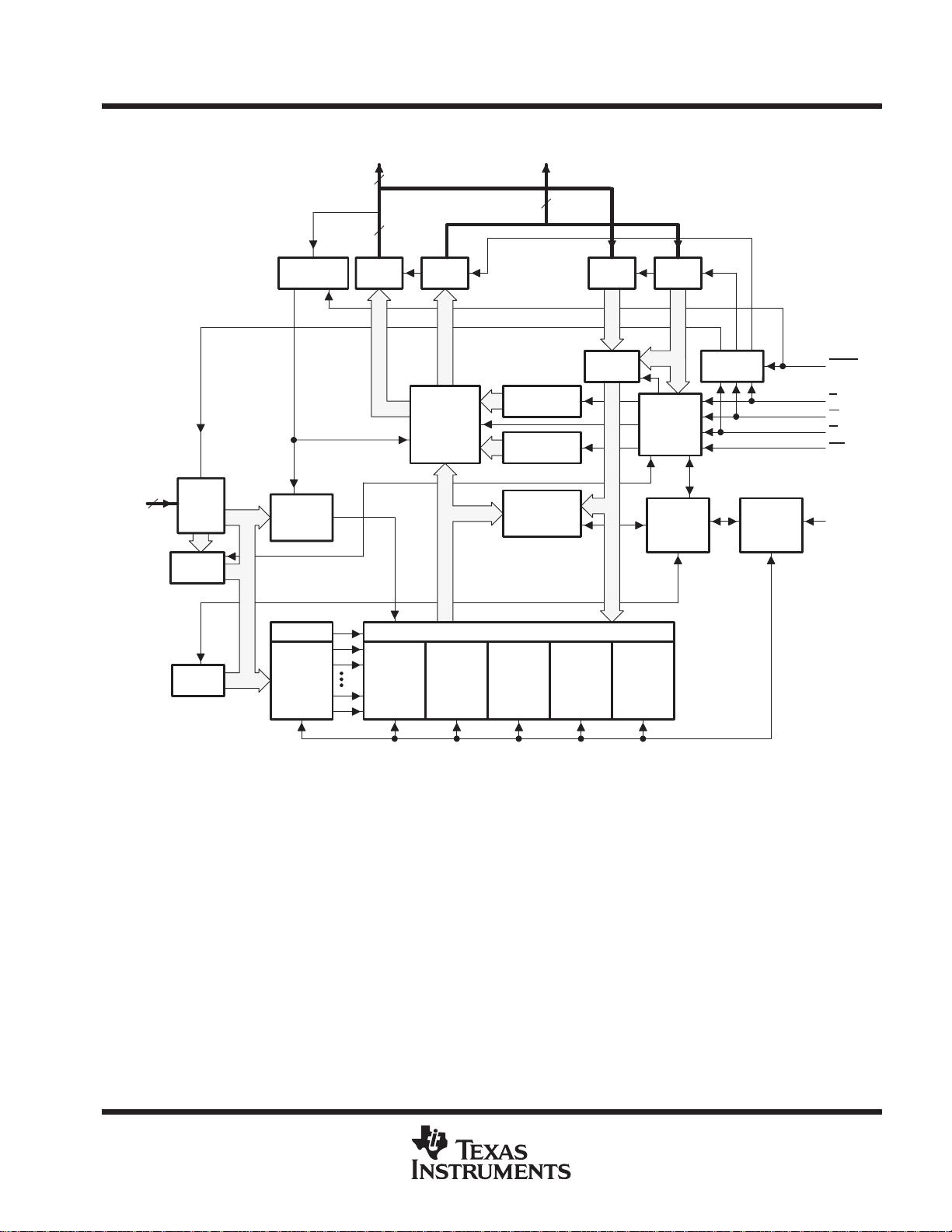

functional block diagram

Counter

Address

Address

Latch

Control

Reduction

Power-

X Decoder

Y Decoder

Y Gating/ Sensing

Block

Main

128K-Byte

Block

Main

96K-Byte

Block

Parameter

8K-Byte

Block

Parameter

8K-Byte

Block

Boot

16K-Byte

I/O Logic

Program/

Voltage

Switch

Erase

Machine

State

Write

Machine

State

Command

Data

Comparator

Register

Data

Input

Buffer

Input

Buffer

Register

Status

Register

Identification

Multiplexer

Output

Input Buffer

DQ15/A

–1

Output

Buffer

Buffer

Output

DQ8–DQ15/A

–1

DQ0–DQ7

A0–

A16

BYTE

E

W

G

RP

V

PP

Input

Buffer

17

8

8

8

architecture

The TMS28F200BZx uses a blocked architecture to allow independent erasure of selected memory blocks.The

block to be erased is selected by using any valid address within that block.

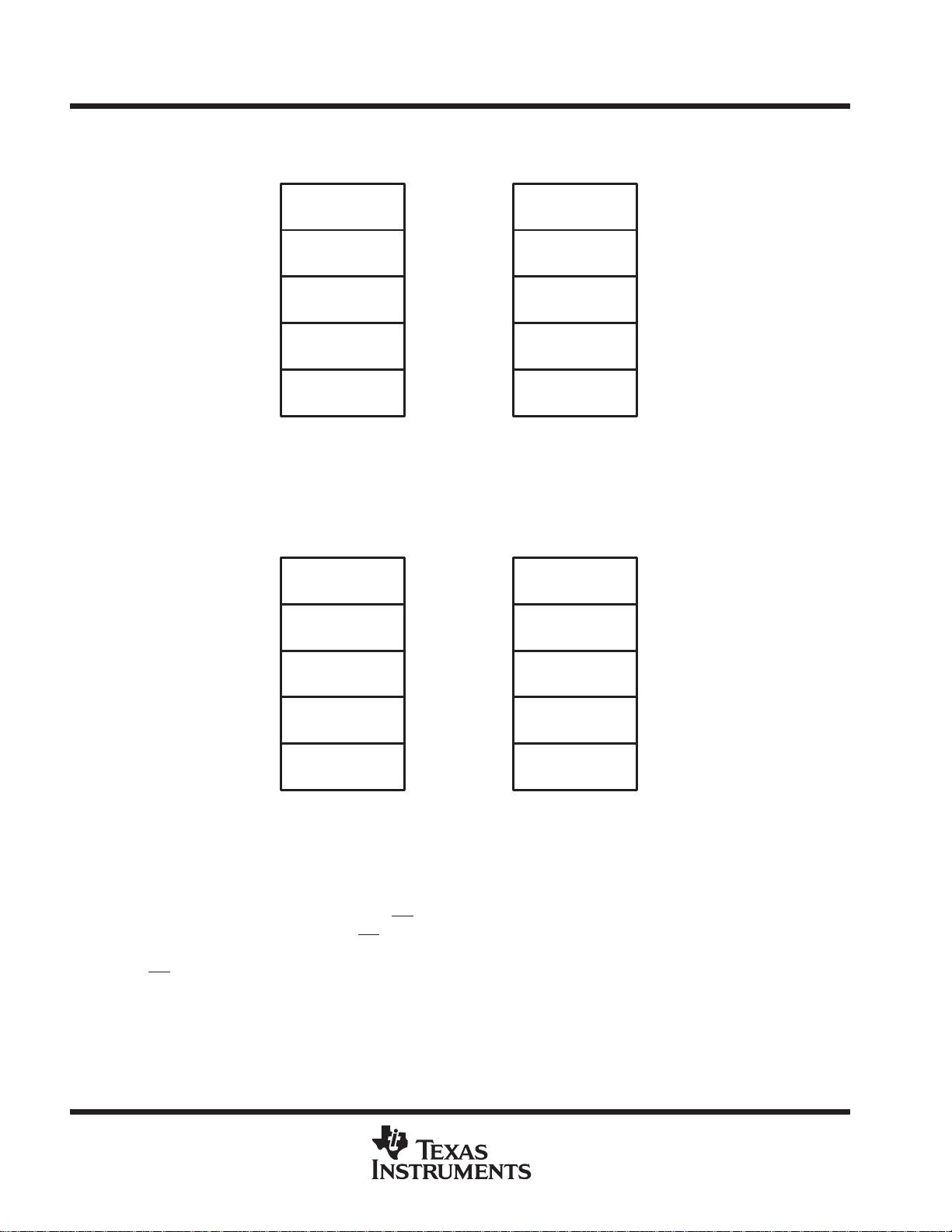

block memory maps

The TMS28F200BZx is available with the block architecture mapped in either of two configurations: the boot

block located at the top or at the bottom of the memory array, as required by different microprocessors. The

TMS28F200BZB (bottom boot block) is mapped with the 16K-byte boot block located at the low-order address

range (00000h to 01FFFh). The TMS28F200BZT (top boot block) is inverted with respect to the

TMS28F200BZB with the boot block located at the high-order address range (1E000h to 1FFFFh). Both of these

address ranges are for word-wide mode. Figure 1 and Figure 2 show the memory maps for these

configurations.

TMS28F200BZT, TMS28F200BZB

262144 BY 8-BIT/131072 BY 16-BIT

BOOT-BLOCK FLASH MEMORIES

SMJS200E – JUNE 1994 – REVISED JANUARY 1998

4

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

block memory maps (continued)

3FFFFh

3C000h

3BFFFh

3A000h

39FFFh

38000h

37FFFh

20000h

1FFFFh

00000h

Address

Range

Boot Block

16K Addresses

Parameter Block

8K Addresses

Parameter Block

8K Addresses

Main Block

96K Addresses

Main Block

128K Addresses

×8 Configuration

DQ15/A

–1

Is LSB Address

1FFFFh

1E000h

1DFFFh

1D000h

1CFFFh

1C000h

1BFFFh

10000h

0FFFFh

00000h

Address

Range

Boot Block

8K Addresses

Parameter Block

4K Addresses

Parameter Block

4K Addresses

Main Block

48K Addresses

Main Block

64K Addresses

×16 Configuration

A0 Is LSB Address

Figure 1. TMS28F200BZT (Top Boot Block) Memory Map

3FFFFh

20000h

1FFFFh

08000h

07FFFh

06000h

05FFFh

04000h

03FFFh

00000h

Address

Range

Main Block

128K Addresses

Main Block

96K Addresses

Parameter Block

8K Addresses

Parameter Block

8K Addresses

Boot Block

16K Addresses

×8 Configuration

DQ15/A

–1

Is LSB Address

1FFFFh

10000h

0FFFFh

04000h

03FFFh

03000h

02FFFh

02000h

01FFFh

00000h

Address

Range

Main Block

64K Addresses

Main Block

48K Addresses

Parameter Block

4K Addresses

Parameter Block

4K Addresses

Boot Block

8K Addresses

×16 Configuration

A0 Is LSB Address

Figure 2. TMS28F200BZB (Bottom Boot Block) Memory Map

boot-block data protection

The 16K-byte boot block can be used to store key system data that is seldom changed in normal operation. To

protect data within this memory sector, the RP pin can be used to provide a lockout to eliminate either accidental

erase or program operations. When RP

is operated with normal TTL/CMOS logic levels, the contents of the

boot block cannot be erased or reprogrammed. Changes to the contents of the boot block can be made only

when RP

is at V

HH

(nominally 12 V) during normal write/erase operations.

parameter block

Two parameter blocks of 8K bytes each can be used like a scratch pad to store frequently updated data.

Alternatively, the parameter blocks can be used for additional boot- or main-block data. If a parameter block is

used to store additional boot-block data, caution should be exercised because the parameter block does not

have the boot-block data-protection safety feature.

TMS28F200BZT, TMS28F200BZB

262144 BY 8-BIT/131072 BY 16-BIT

BOOT-BLOCK FLASH MEMORIES

SMJS200E – JUNE 1994 – REVISED JANUARY 1998

5

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

main block

Primary memory on the TMS28F200BZx is located in two main blocks. One of the blocks has a storage capacity

for 128K bytes and the other block has a storage capacity for 96K bytes.

command state machine

Commands are issued to the CSM using standard microprocessor write timings. The CSM acts as an interface

between the external microprocessor and the internal WSM. The available commands are listed in Table 1 and

the description of these commands are shown in Table 2. When a program or erase command is issued to the

CSM, the WSM controls the internal sequences and the CSM only responds to status reads. After the WSM

completes its task, the WSM status bit (SB7) is set to a logic-high level (1), allowing the CSM to respond to the

full command set again.

operation

Device operations are selected by entering standard JEDEC 8-bit command codes with conventional

microprocessor timing into an on-chip CSM through I/O pins DQ0–DQ7. When the device is powered up,

internal reset circuitry initializes the chip to a read-array mode of operation. Changing the mode of operation

requires a command code to be entered into the CSM. Table 1 lists the CSM codes for all modes of operation.

The on-chip status register allows the progress of various operations to be monitored. The status register is

interrogated by entering a read-status-register command into the CSM (cycle 1) and reading the register data

on I/O pins DQ0–DQ7 (cycle 2). Status-register bits SB0 through SB7 correspond to DQ0 through DQ7.

Table 1. Command State Machine Codes for Device Mode Selection

COMMAND

CODE ON

DQ0–DQ7

†

DEVICE MODE

00h

10h

20h

40h

50h

70h

90h

B0h

D0h

FFh

Invalid/Reserved

Alternate Program Setup

Block-Erase Setup

Program Setup

Clear Status Register

Read Status Register

Algorithm Selection

Erase-Suspend

Erase-Resume/Block-Erase Confirm

Read Array

†

DQ0 is the least significant bit. DQ8–DQ15 can be any valid 2-state

level.

剩余28页未读,继续阅读

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0

最新资源