没有合适的资源?快使用搜索试试~ 我知道了~

TI-THS7347.pdf

需积分: 10 0 下载量 108 浏览量

2022-12-04

00:11:44

上传

评论 4

收藏 833KB PDF 举报

温馨提示

试读

32页

TI-THS7347.pdf

资源推荐

资源详情

资源评论

3.3V

3.3V

2:1

Input1

0.1 Fm

0.1 Fm

0.1 Fm

In A

InB

Input2

75 W

ADC

AC

Sync

TIP

Clamp

DC

X1

DC

+Offset

AC-

BIAS

+

-

1kW 878 W

675 W

150 W

+

-

Out

SAG

47 Fm

33 Fm

75 W

75 W

Monitor

Output

75 W

SDA

SCL

Disable

= OPEN

THS7347

www.ti.com

SLOS531B –MAY 2007– REVISED OCTOBER 2011

3-Channel RGBHV Video Buffer with I

2

C™ Control, 2:1 Input Mux,

Monitor Pass-Through, and Selectable Input Bias Modes

Check for Samples: THS7347

1

FEATURES

APPLICATIONS

2345

• 3-Video Amplifiers for CVBS, S-Video, EDTV,

• Projectors

HDTV Y'P'

B

P'

R

, G'B'R', and R'G'B' Video

• Professional Video Systems

• H/V Sync Paths with Adjustable Schmitt

• LCD/ DLP

®

/LOCS Input Buffering

Trigger

• 2:1 Input Mux DESCRIPTION

Fabricated using the revolutionary complimentary

• I

2

C Control of All Functions on Each Channel

silicon-germanium (SiGe) BiCom3 process, the

• Unity-Gain Buffer Path for ADC Buffering:

THS7347 is a low-power, single-supply 2.7-V to 5-V

– 500-MHz Bandwidth, 1200-V/μs Slew Rate

3-channel integrated video buffer with horizontal (H)

and vertical (V) sync signal paths. It incorporates a

• Monitor Pass-Through Function:

500-MHz bandwidth, 1200-V/μs unity-gain buffer ideal

– 500-MHz Bandwidth, 1300-V/μs Slew Rate

for driving analog-to-digital converters (ADCs) and

– 6-dB Gain with SAG Correction Capable

video decoders. In parallel with the unity-gain buffer,

– High Output Impedance in Disable State

a monitor pass-through path allows for passing the

input signal on to other systems. This path has a

• Selectable Input Bias Modes:

6-dB gain, 500-MHz bandwidth, 1300-V/μs slew rate,

– AC-Coupled with Sync-Tip Clamp

SAG correction capability, and high output impedance

– AC-Coupled with Bias

while disabled.

– DC-Coupled with Offset Shift

Each channel of the THS7347 is individually

– DC-Coupled

I

2

C-configurable for all functions, including controlling

the 2:1 input mux. Its rail-to-rail output stage allows

• +2.7-V to +5-V Single-Supply Operation

for both ac- and dc-coupling applications.

• Total Power Consumption: 265 mW at 3.3 V

• Disable Function Reduces Current to 0.1 μA

• Rail-to-Rail Output:

– Output Swings Within 0.1 V of the Rails,

Allowing AC- or DC-Output Coupling

• Lead-free, RoHS TQFP Package

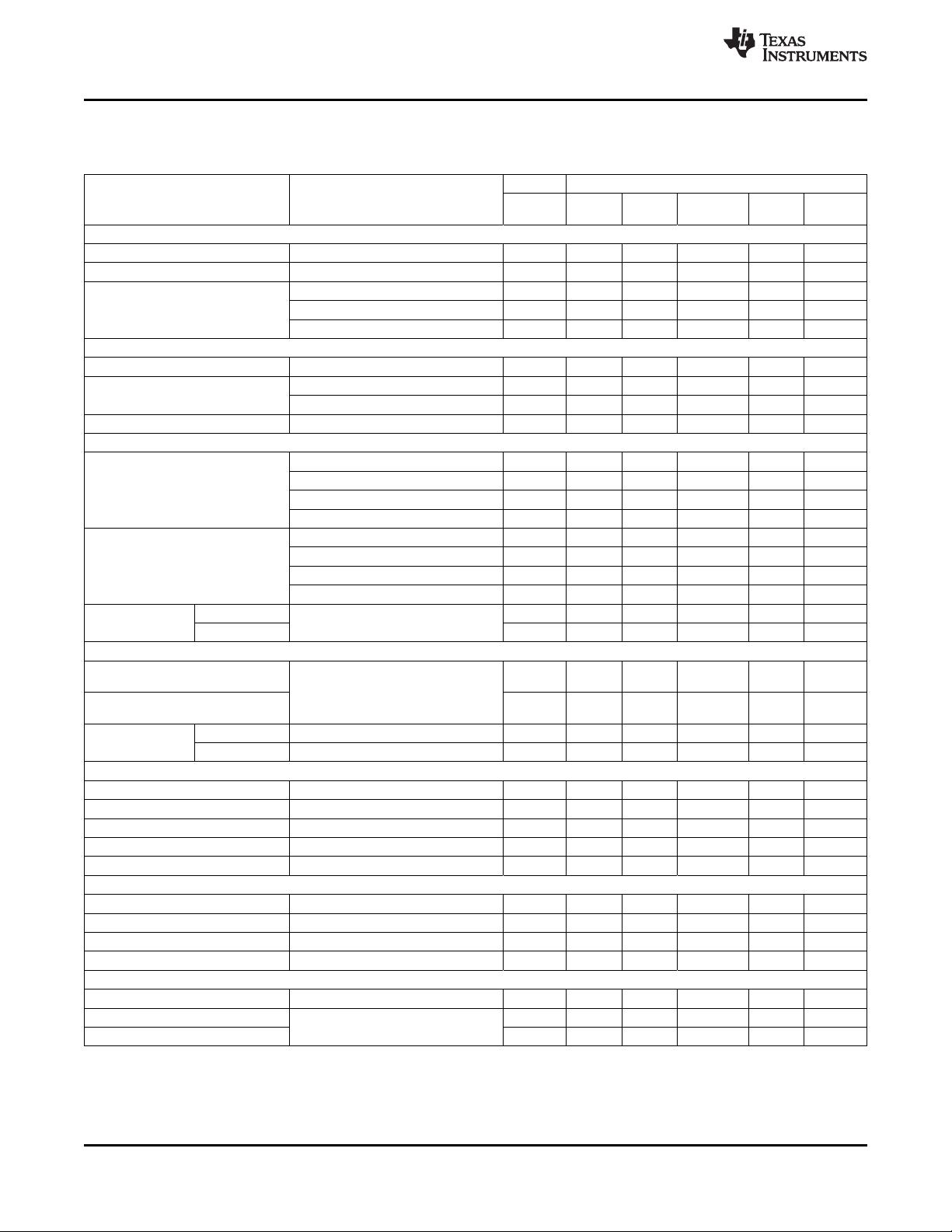

3.3 V Single-Supply Projector Input System with Monitor Pass-Through

(One of Three R'G'B' Channels Shown)

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2PowerPAD is a trademark of Texas Instruments.

3DLP is a registered trademark of Texas Instruments.

4I

2

C is a trademark of NXP Semiconductors, Inc.

5All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2007–2011, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

THS7347

SLOS531B –MAY 2007– REVISED OCTOBER 2011

www.ti.com

DESCRIPTION, CONTINUED

As part of the THS7347 flexibility, the device input can be selected for ac- or dc-coupled inputs. The ac-coupled

modes include a sync-tip clamp option for CVBS/Y'/G'B'R' with sync or a fixed bias for the C'/P'

B

/P'

R

/R'G'B'

channels without sync. The dc input options include a dc input or a dc+Offset shift to allow for a full sync

dynamic range at the output with 0-V input.

The THS7347 is available in a lead-free, RoHS-compliant TQFP package.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

PACKAGING/ORDERING INFORMATION

(1)

PACKAGED DEVICES PACKAGE TYPE TRANSPORT MEDIA, QUANTITY

THS7347IPHP Tray, 250

HTQFP-48 PowerPAD™

THS7347IPHPR Tape and Reel, 1000

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

ABSOLUTE MAXIMUM RATINGS

(1)

Over operating free-air temperature range (unless otherwise noted).

THS7347 UNIT

V

SS

Supply voltage, GND to V

A

or GND to V

DD

5.5 V

V

I

Input voltage –0.4 to V

A

or V

DD

V

I

O

Continuous output current ±80 mA

Continuous power dissipation See Dissipation Rating Table

T

J

Maximum junction temperature, any condition

(2)

+150 °C

T

J

Maximum junction temperature, continuous operation, long term reliability

(3)

+125 °C

T

stg

Storage temperature range –65 to +150 °C

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 300 °C

HBM 1500 V

ESD ratings CDM 1500 V

MM 100 V

(1) Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied Exposure to absolute maximum rated conditions for extended periods may degrade device reliability.

(2) The absolute maximum junction temperature under any condition is limited by the constraints of the silicon process.

(3) The absolute maximum junction temperature for continuous operation is limited by the package constraints. Operation above this

temperature may result in reduced reliability and/or lifetime of the device.

DISSIPATION RATINGS

POWER RATING

(1) (2)

(T

J

= +125°C)

θ

JC

θ

JA

PACKAGE (°C/W) (°C/W) T

A

= +25°C T

A

= +85°C

HTQFP-48 with PowerPAD (PHP) 1.2 35 2.85 W 1.14 W

(1) This data was taken with a PowerPAD standard 3-inch by 3-inch, 4-layer printed circuit board (PCB) with internal ground plane

connections to the PowerPAD.

(2) Power rating is determined with a junction temperature of +125°C. This temperature is the point where distortion starts to substantially

increase and long-term reliability starts to be reduced. Thermal management of the final PCB should strive to keep the junction

temperature at or below +125°C for best performance and reliability.

2 Copyright © 2007–2011, Texas Instruments Incorporated

THS7347

www.ti.com

SLOS531B –MAY 2007– REVISED OCTOBER 2011

RECOMMENDED OPERATING CONDITIONS

MIN NOM MAX UNIT

V

DD

Digital supply voltage 2.7 5 V

V

A

Analog supply voltage. Must be equal to or greater than V

DD

V

DD

5 V

T

A

Ambient temperature –40 +85 °C

ELECTRICAL CHARACTERISTICS, V

A

= V

DD

= 3.3 V

R

L

= 150 Ω ∥ 5 pF to GND for Monitor Output, 19 kΩ || 8 pF Load to GND for Buffer Output, SAG pin shorted to Monitor

Output Pin, unless otherwise noted.

TYP OVER TEMPERATURE

0°C to –40°C to MIN/MAX/

PARAMETER TEST CONDITIONS +25°C +25°C +70°C +85°C UNIT TYP

AC PERFORMANCE

Buffer output 500 MHz Typ

Small-signal

V

O

= 0.2 V

PP

bandwidth (–3 dB)

Monitor output 450 MHz Typ

Buffer output 425 MHz Typ

–1 dB flatness V

O

= 0.2 V

PP

Monitor output 375 MHz Typ

Buffer output V

O

= 1 V

PP

475 MHz Typ

Large-signal

bandwidth (–3 dB)

Monitor output V

O

= 2 V

PP

240 MHz Typ

Buffer output V

O

= 1 V

PP

1050 V/μs Typ

Slew rate

Monitor output V

O

= 2 V

PP

1050 V/μs Typ

Buffer output 1.2 ns Typ

Group delay at

100 kHz

Monitor output 1.2 ns Typ

Buffer output 0.05/0.05 % Typ

Differential gain NTSC/PAL

Monitor output 0.1/0.1 % Typ

Buffer output 0.1/0.15 degrees Typ

Differential phase NTSC/PAL

Monitor output 0.15/0.2 degrees Typ

Buffer output V

O

= 1 V

PP

–58 dB Typ

Total harmonic

distortion f = 1 MHz

Monitor output V

O

= 2 V

PP

–57 dB Typ

Buffer output 63 dB Typ

Signal-to-noise ratio No weighting, up to 100 MHz

Monitor output 65 dB Typ

Buffer output –40 dB Typ

Channel-to-channel

f = 100 MHz

crosstalk

Monitor output –36 dB Typ

Buffer output 64 dB Typ

MUX isolation f = 100 MHz

Monitor output 66 dB Typ

Buffer output f = 100 kHz; V

O

= 1 V

PP

0 dB Typ

Gain

Monitor output f = 100 kHz; V

O

= 2 V

PP

6 5.8/6.25 5.75/6.3 5.75/6.35 dB Min/Max

Buffer output 6 ns Typ

Settling time V

IN

= 1 V

PP

; 0.5% settling

Monitor output 6 ns Typ

Buffer output 0.3 Ω Typ

Output impedance f = 10 MHz

Monitor output 0.4 Ω Typ

DC PERFORMANCE

Buffer output 15 ±80 ±85 ±85 mV Max

Output offset voltage Bias = dc

Monitor output 20 ±120 ±125 ±125 mV Max

Buffer output 20 μV/°C Typ

Average offset

Bias = dc

voltage drift

Monitor output 20 μV/°C Typ

Bias = dc + shift, V

IN

= 0 V 255 175/355 165/365 160/370 mV Min/Max

Buffer output

Bias = ac 1.0 0.85/1.15 0.8/1.2 0.8/1.2 V Min/Max

Bias output voltage

Bias = dc + shift, V

IN

= 0 V 235 145/350 135/360 130/365 mV Min/Max

Monitor output

Bias = ac 1.7 1.55/1.85 1.5/1.9 1.5/1.9 V Min/Max

Buffer output 290 200/405 195/410 190/415 mV Min/Max

Sync tip clamp

Bias = ac STC, clamp voltage

voltage

Monitor output 300 200/400 195/405 190/410 mV Min/Max

Copyright © 2007–2011, Texas Instruments Incorporated 3

THS7347

SLOS531B –MAY 2007– REVISED OCTOBER 2011

www.ti.com

ELECTRICAL CHARACTERISTICS, V

A

= V

DD

= 3.3 V (continued)

R

L

= 150 Ω ∥ 5 pF to GND for Monitor Output, 19 kΩ || 8 pF Load to GND for Buffer Output, SAG pin shorted to Monitor

Output Pin, unless otherwise noted.

TYP OVER TEMPERATURE

0°C to –40°C to MIN/MAX/

PARAMETER TEST CONDITIONS +25°C +25°C +70°C +85°C UNIT TYP

DC PERFORMANCE, continued

Input bias current Bias = dc; (–) implies I

B

out of the pin –1.3 –3.0 –3.5 –3.5 μA Max

Average bias current drift Bias = dc 10 nA/°C Typ

Bias = ac STC, low bias 2.3 0.9/3.6 0.8/3.8 0.7/3.9 μA Min/Max

Sync tip clamp bias current Bias = ac STC, mid bias 5.8 3.8/8.0 3.7/8.2 3.6/8.3 μA Min/Max

Bias = ac STC, high bias 8.1 5.7/10.8 5.6/11.0 5.5/11.1 μA Min/Max

INPUT CHARACTERISTICS

Input voltage range Bias = dc 0 to 2 V Typ

Bias = ac bias mode 25 kΩ Typ

Input resistance

Bias = dc, dc + shift, ac STC 3 MΩ Typ

Input capacitance 1.5 pF Typ

OUTPUT CHARACTERISTICS: MONITOR OUTPUT

R

L

= 150 Ω to 1.65 V 3.15 2.9 2.8 2.8 V Min

R

L

= 150 Ω to GND 3.05 2.85 2.75 2.75 V Min

High output voltage swing

R

L

= 75 Ω to 1.65 V 3.05 V Typ

R

L

= 75 Ω to GND 2.9 V Typ

R

L

= 150 Ω to 1.65 V 0.15 0.25 0.28 0.29 V Max

R

L

= 150 Ω to GND 0.1 0.18 0.21 0.22 V Max

Low output voltage swing

R

L

= 75 Ω to 1.65 V 0.25 V Typ

R

L

= 75 Ω to GND 0.08 V Typ

Sourcing 80 50 47 45 mA Min

Output current R

L

= 10 Ω to 1.65 V

Sinking 75 50 47 45 mA Min

OUTPUT CHARACTERISTICS: BUFFER OUTPUT

High output voltage swing

2 1.8 1.75 1.75 V Min

(Limited by input range and G = 0 dB)

Load = 19 kΩ ∥ 8 pF to 1.65 V

Low Output voltage swing

0.05 0.12 0.13 0.14 V Max

(Limited by input range and G = 0 dB)

Sourcing R

L

= 10 Ω to GND 80 50 47 45 mA Min

Output Current

Sinking R

L

= 10 Ω to 1.65 V 75 50 47 45 mA Min

POWER SUPPLY: ANALOG

Maximum operating voltage V

A

3.3 5.5 5.5 5.5 V Max

Minimum operating voltage V

A

3.3 2.7 2.7 2.7 V Min

Maximum quiescent current V

A

, dc + shift mode, V

IN

= 100 mV 80 100 103 105 mA Max

Minimum quiescent current V

A

, dc + shift mode, V

IN

= 100 mV 80 60 57 55 mA Min

Power supply rejection (+PSRR) Buffer output 50 dB Typ

POWER SUPPLY: DIGITAL

Maximum operating voltage V

DD

3.3 5.5 5.5 5.5 V Max

Minimum operating voltage V

DD

3.3 2.7 2.7 2.7 V Min

Maximum quiescent current V

DD

, V

IN

= 0 V 0.65 1.2 1.3 1.4 mA Max

Minimum quiescent current V

DD

, V

IN

= 0 V 0.65 0.35 0.3 0.25 mA Min

DISABLE CHARACTERISTICS: ALL CHANNELS DISABLED

Quiescent current All channels disabled 0.1 μA Typ

Turn-on time delay (t

ON

) 5 μs Typ

Time for l

S

to reach 50% of final value

after I

2

C control is initiated

Turn-on time delay (t

OFF

) 2 μs Typ

4 Copyright © 2007–2011, Texas Instruments Incorporated

THS7347

www.ti.com

SLOS531B –MAY 2007– REVISED OCTOBER 2011

ELECTRICAL CHARACTERISTICS, V

A

= V

DD

= 3.3 V (continued)

R

L

= 150 Ω ∥ 5 pF to GND for Monitor Output, 19 kΩ || 8 pF Load to GND for Buffer Output, SAG pin shorted to Monitor

Output Pin, unless otherwise noted.

TYP OVER TEMPERATURE

0°C to –40°C to MIN/MAX/

PARAMETER TEST CONDITIONS +25°C +25°C +70°C +85°C UNIT TYP

DIGITAL CHARACTERISTICS

(1)

High level input voltage V

IH

2.3 V Typ

Low level input voltage V

IL

1.0 V Typ

H/V SYNC CHARACTERISTICS: R

Load

= 1 kΩ To GND

(2)

Schmitt trigger adjust pin voltage Reference for Schmitt trigger 1.47 1.35/1.6 1.3/1.65 1.27/1.68 V Min/Max

Schmitt trigger threshold range Allowable range for Schmitt trigger adjust 0.9 to 2 V Typ

Positive-going input voltage threshold

Schmitt trigger VT+ 0.25 V Typ

relative to Schmitt trigger threshold

Negative-going input voltage threshold

Schmitt trigger VT– –0.3 V Typ

relative to Schmitt trigger threshold

Schmitt trigger threshold pin input

Input resistance into Control pin 10 kΩ Typ

resistance

H/V Sync input impedance 10 MΩ Typ

H/V Sync high output voltage 1 kΩ to GND 3.15 3.05 3.0 3.0 V Min

H/V Sync low output voltage 1 kΩ to GND 0.01 0.05 0.1 0.1 V Max

H/V Sync source current 10 Ω to GND 50 35 30 30 mA Min

H/V Sync sink current 10 Ω to 3.3 V 35 25 23 21 mA Min

H/V Delay Delay from Input to output 6.5 ns Typ

H/V to buffer output skew 5 ns Typ

(1) Standard CMOS logic.

(2) Schmitt trigger threshold is defined by (VT+ – VT–)/2.

Copyright © 2007–2011, Texas Instruments Incorporated 5

剩余31页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3199

- 资源: 5526

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 三层独栋别墅图纸编号D066-三层-12.00&12.00米- 施工图.dwg

- 农村小别墅图纸编号D065-三层-14.40&18.55米-施工图.dwg

- 基于YOLOv8检测高铁吊弦缺陷实现的系统的Python源码+文档说明+训练源文件+模型.zip

- 三层农村小别墅图纸编号D064-三层-13.80&22.20米-施工图.dwg

- 三层别墅图纸编号D063-三层-13.57&17.40米- 施工图.dwg

- STC IAP15F2K61S2单片机i2c 接口PCF8591-ADC实验+DAC实验 KEIL例程源码+开发板硬件原理图

- Jlink-windows-v7967

- ADC直流分量影响分析

- 二层半独栋别墅结构水电施工图结构专家电.dwg

- 二层半独栋别墅结构水电施工图结构水暖图.dwg

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功