实验1-Vivado使用及组合电路的Verilog实现1

需积分: 0 91 浏览量

更新于2022-08-08

1

收藏 3.27MB DOCX 举报

【实验1-Vivado使用及组合电路的Verilog实现1】是针对初学者的一个实践教程,旨在让学习者熟悉Vivado开发环境以及如何使用Verilog实现组合逻辑电路。Vivado是Xilinx公司推出的一款集成开发环境,包含了设计、仿真、综合、布局布线等一系列功能,用于FPGA开发。

实验目的:

1. 掌握Vivado的界面和基本操作流程。

2. 熟悉Xilinx FPGA开发环境,如EGO-1实验板的特性和使用。

3. 学习Verilog的三种描述方法:结构描述、数据流描述和行为描述。

4. 通过具体实验,使用Verilog设计和实现8位拨码开关控制8位LED灯的组合电路,并在EGO-1开发板上验证结果。

实验设备:

EGO-1开发板,其主芯片为XC7A35T-CSGD324-1,需要64位的Vivado 2015.4或更高版本。推荐使用2018.3、2019.1、2019.2等较新版本的Vivado Webpack版,该版本是免费的,但对支持的芯片有限制。

实验步骤:

1. 安装Vivado:Vivado可通过官网下载,也可以通过提供的网盘链接获取安装包。有本地安装和在线安装两种方式,考虑到安装包较大,通常推荐本地安装。安装完成后,占用空间约为20GB。

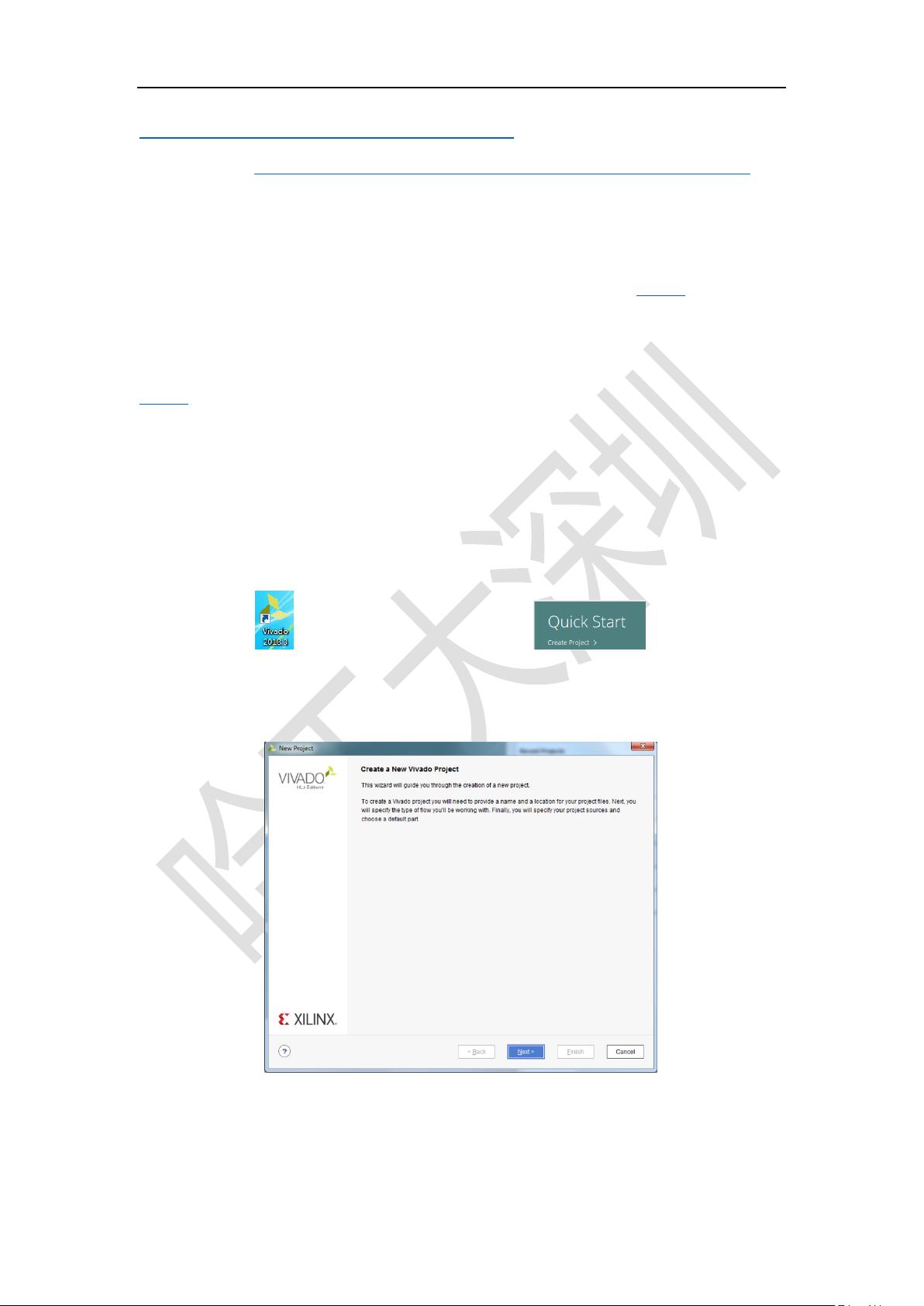

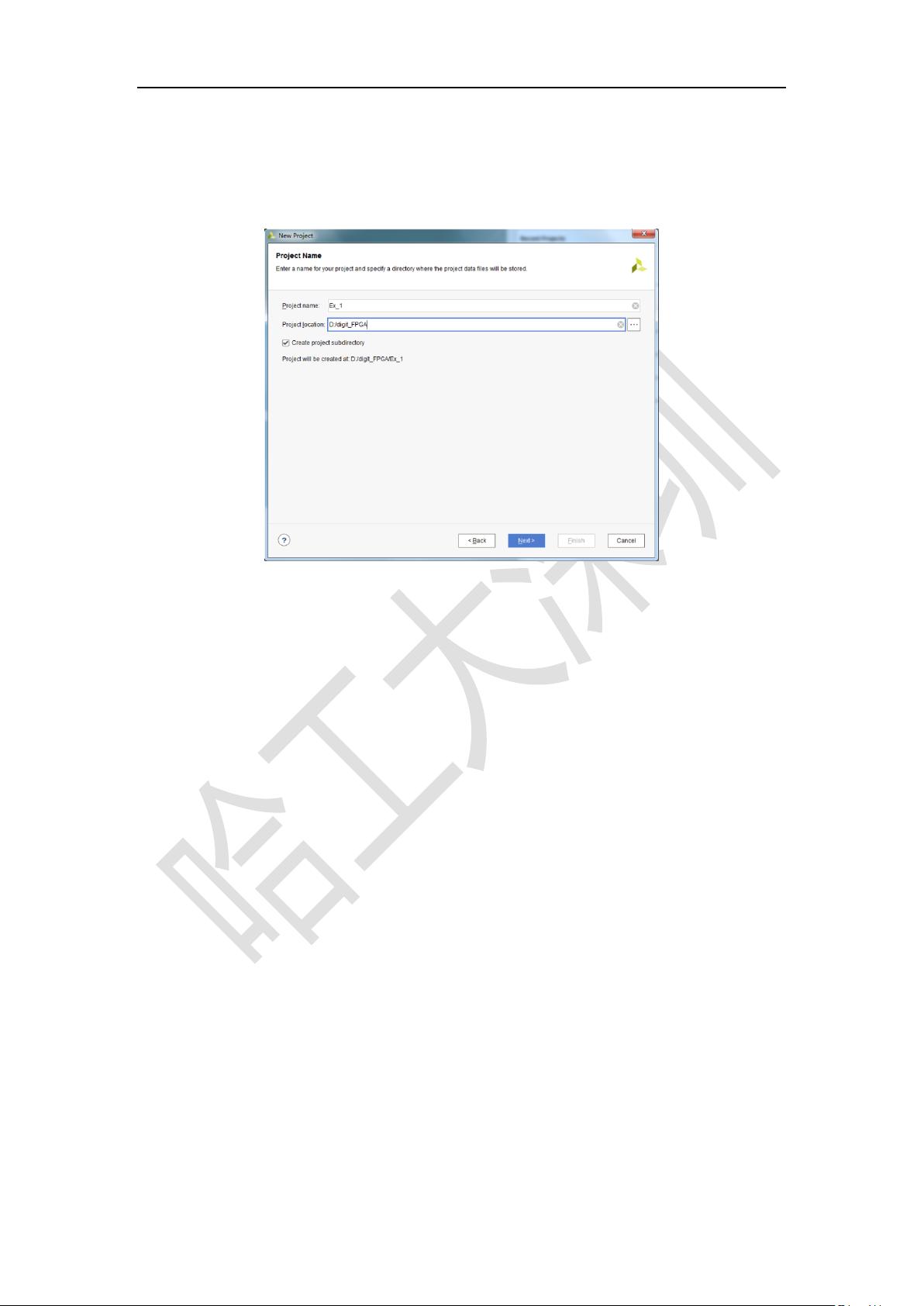

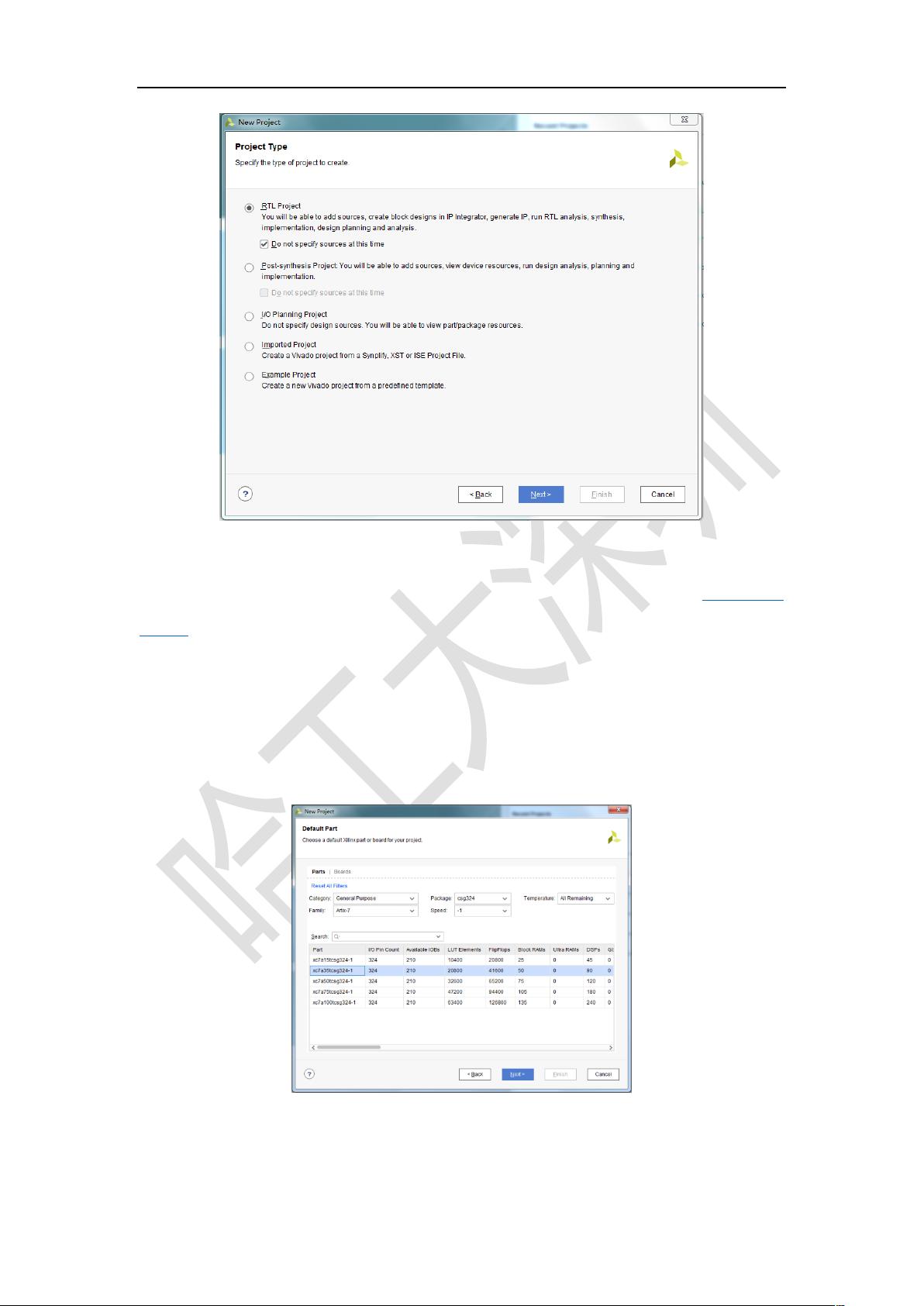

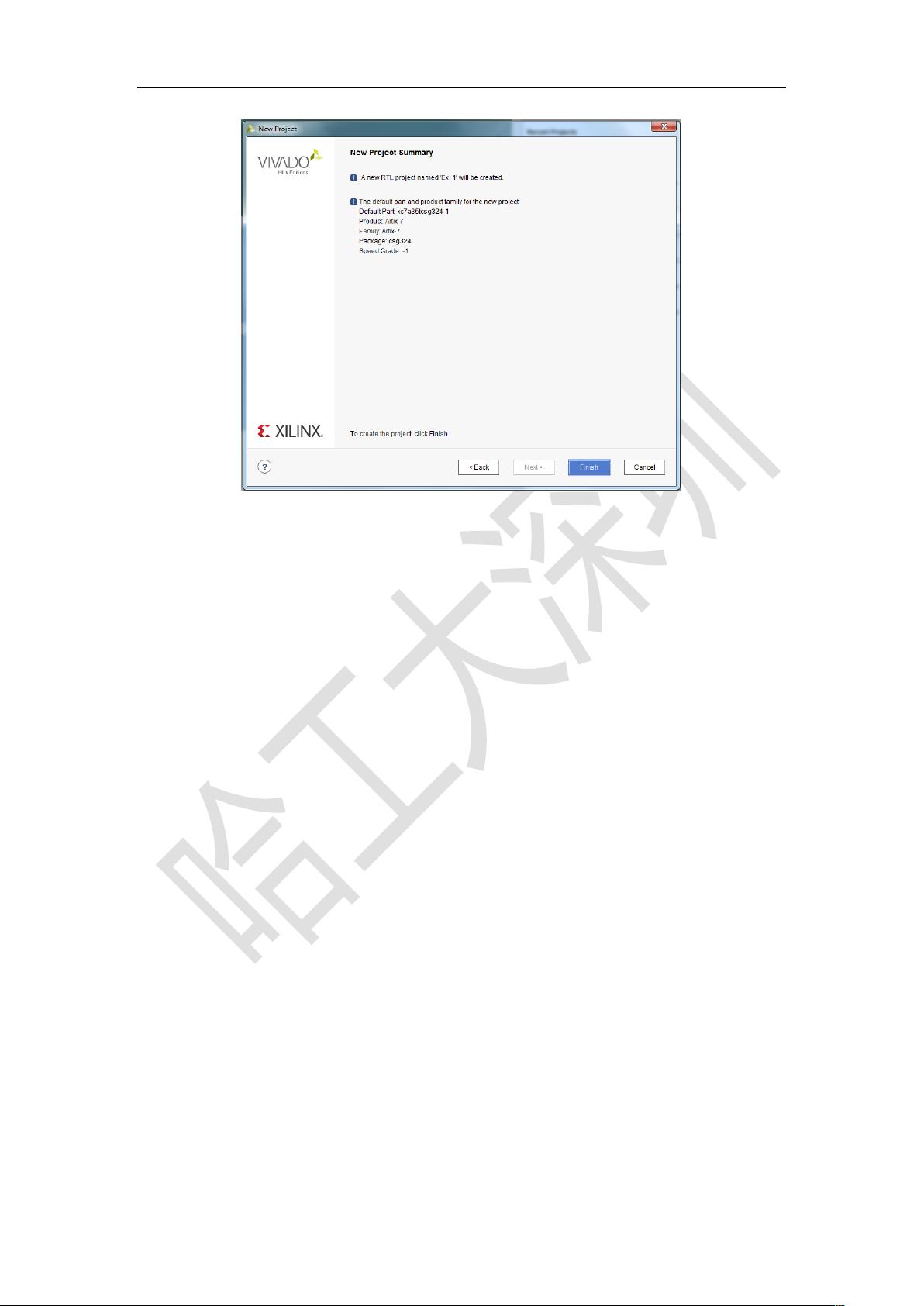

2. 创建新项目:在Vivado启动后,选择“Create Project”,并设置项目名称和路径,避免使用中文和空格。选择项目类型为“RTL Project”,并勾选“Do not specify sources at this time”。

接下来的步骤涉及选择目标器件,对于本实验,需要选择与EGO-1开发板匹配的XC7A35T芯片。在项目设置中指定器件后,可以开始编写Verilog代码来实现拨码开关控制LED的功能。

Verilog编程:

1. 定义输入(拨码开关)和输出(LED)端口,如`input [7:0] switch, output [7:0] led`。

2. 编写逻辑函数,根据拨码开关的值确定LED的状态。

3. 将逻辑函数与端口连接,如`assign led = switch;`。

完成Verilog代码编写后,需要进行编译和仿真验证。在Vivado的Flow Navigator中,选择Synthesis进行逻辑综合,然后选择Implementation进行布局布线。生成Bitstream文件并下载到EGO-1开发板上进行硬件验证。

通过这个实验,学习者不仅可以掌握Vivado的基本操作,还能深入了解Verilog语言在FPGA设计中的应用。同时,对FPGA市场的主要厂商,如Xilinx和Intel(通过收购Altera)的产品线也会有初步的认识。这对于进一步深入FPGA学习和开发是非常有益的。

XU美伢

- 粉丝: 775

- 资源: 340

最新资源

- 毕设-java-[信息办公]简易java开源订销管理系统_javainfo30.zip

- 毕设-java-[其他类别]MeyboMail Web(Java)开源简化_meybomailweb24.zip

- 毕设-java-[其他类别]UrlRewriter Java v2.0 RC1_urlrewriterjava25.zip

- 毕设-java-[其他类别]jsp+servlet+javaBean实现MVC_jspmvc23.zip

- 毕设-java-[企业]Java企业进销存管理系统源码_jxc_j26.zip

- Java源码jsp考试安排系统-毕业设计-期末大作业.zip

- Java源码jsp口腔医院网络预约系统-毕业设计-期末大作业.zip

- Java源码jsp课程设计系统-毕业设计-期末大作业.zip

- 同轴剥皮机sw18可编辑全套技术资料100%好用.zip

- AnderWeb-android-packages-apps-Launcher-4458ee4-仅用于Android项目学习

- postgis-bundle-pg13x64-setup-3.5.0-1.exe

- Java源码jsp连锁酒店管理系统-毕业设计-期末大作业.zip

- andorid 源码北京公交线路查询(离线)-仅用于Android项目学习

- Java源码jsp离退休干部综合信息管理系统-毕业设计-期末大作业.zip

- Java源码jsp狼牙山中心小学校园网-毕业设计-期末大作业.zip

- share5149655557007223706.jpg