Vivado 的安装

本附录基于 Vivado2019.2 进行说明,对其他版本的 Vivado 的安装也同样适用。在学习

本部分内容前,你需要准备以下环境:

1) 装有 Windows 或 Linux 操作系统的电脑一台。

2) 连通的网络。

如果已有 Vivado 对应版本的本地安装包,可以直接从 B.2 节开始学习。

如果本地电脑没有 Vivado 安装包,可拷贝或下载。安装包下载地址可以在 Xilinx 官网上

( http://china.xilinx.com/support.download.html 或 https://www.xilinx.com/support/dow nl

oad.html)找到。

Vivado 的安装支持本地安装与在线安装方式,它们的对比如表 B-1 所示。

表B-1 Vivado本地安装与在线安装优劣势对比

B.1 Vivado 简介

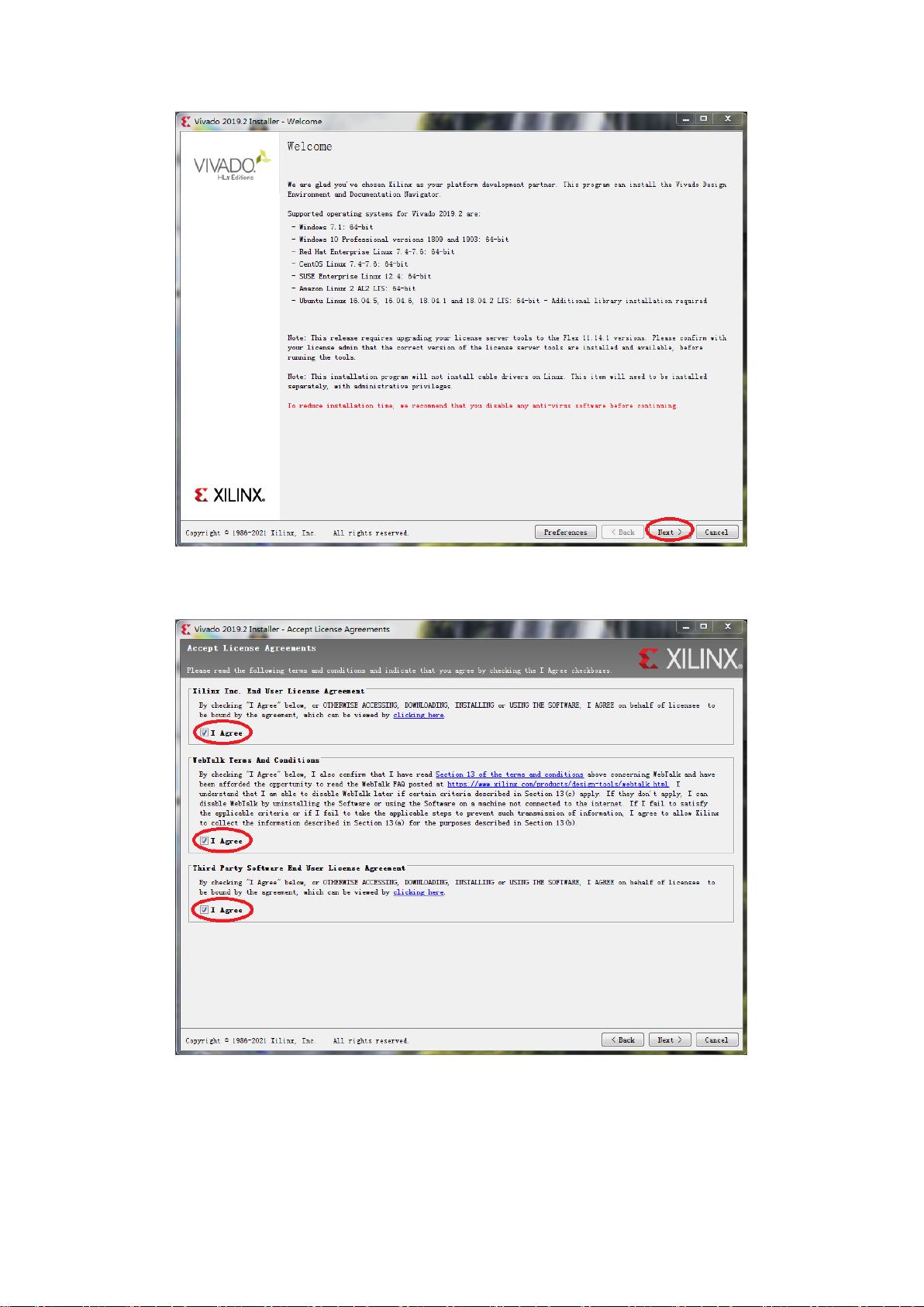

Vivado 是 Xilinx 公司开发的一款 EDA 工具。可以在 Windows 上安装 Vivado2019.2 的

WebPACK 版本,该版本为免 License 的 Vivado 版本,支持的器件受限。该版本支持 Artix-7

器件的开发,足够完成本书的实验任务。安装该软件要求硬盘空间至少有 20G。Vivado2019.2

支持以下操作系统:

⚫ Windows 7.1:64-bit(Vivado2019.2 是支持 Windows 7 的最后版本)

⚫ Windows 10.0 1809/1903 Update:64-bit

⚫ Red Hat Enterprise Workstation/Server 7.4-7.6:64-bit

⚫ SUSE linux Enterprise 12.4:64-bit

⚫ CentOS 7.4-7.6:64-bit

⚫ Ubuntu Linux 16.04.5/16.04.6/18.04.1/18.04.2 LTS: 64-bit

⚫ Amazon Linux 2 LTS: 64-bit

B.2 Vivado 的本地安装

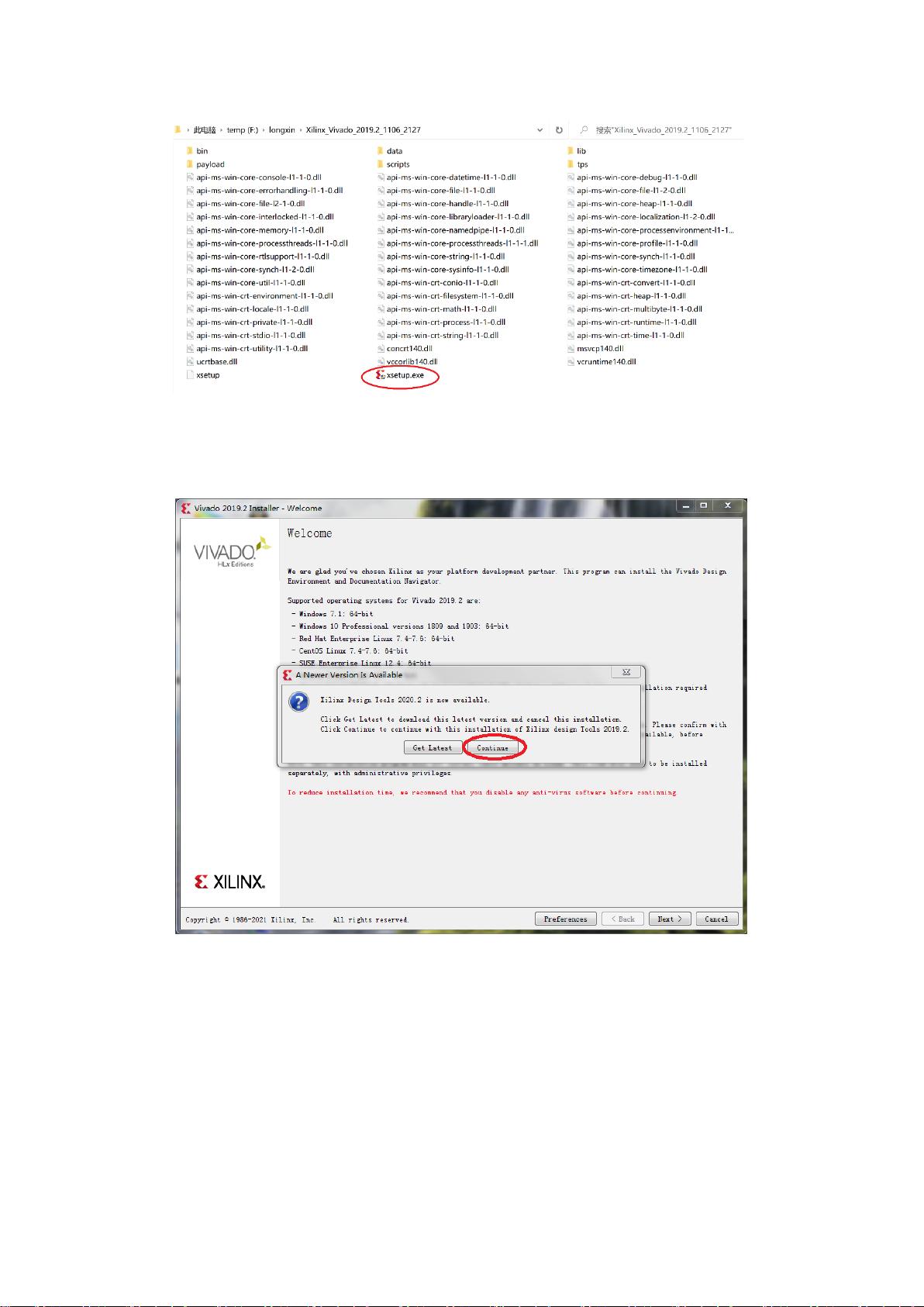

下载后,将 Vivado 安装包 Xilinx_Vivado_2019.2_1106_2127.tar.gz 解压到不含中文和空

格的路径中,注意这个解压到的路径不是 Vivado 软件安装的路径,只是安装文件的暂时路

径,如图 B-1 所示。

- 1

- 2

- 3

- 4

- 5

- 6

前往页