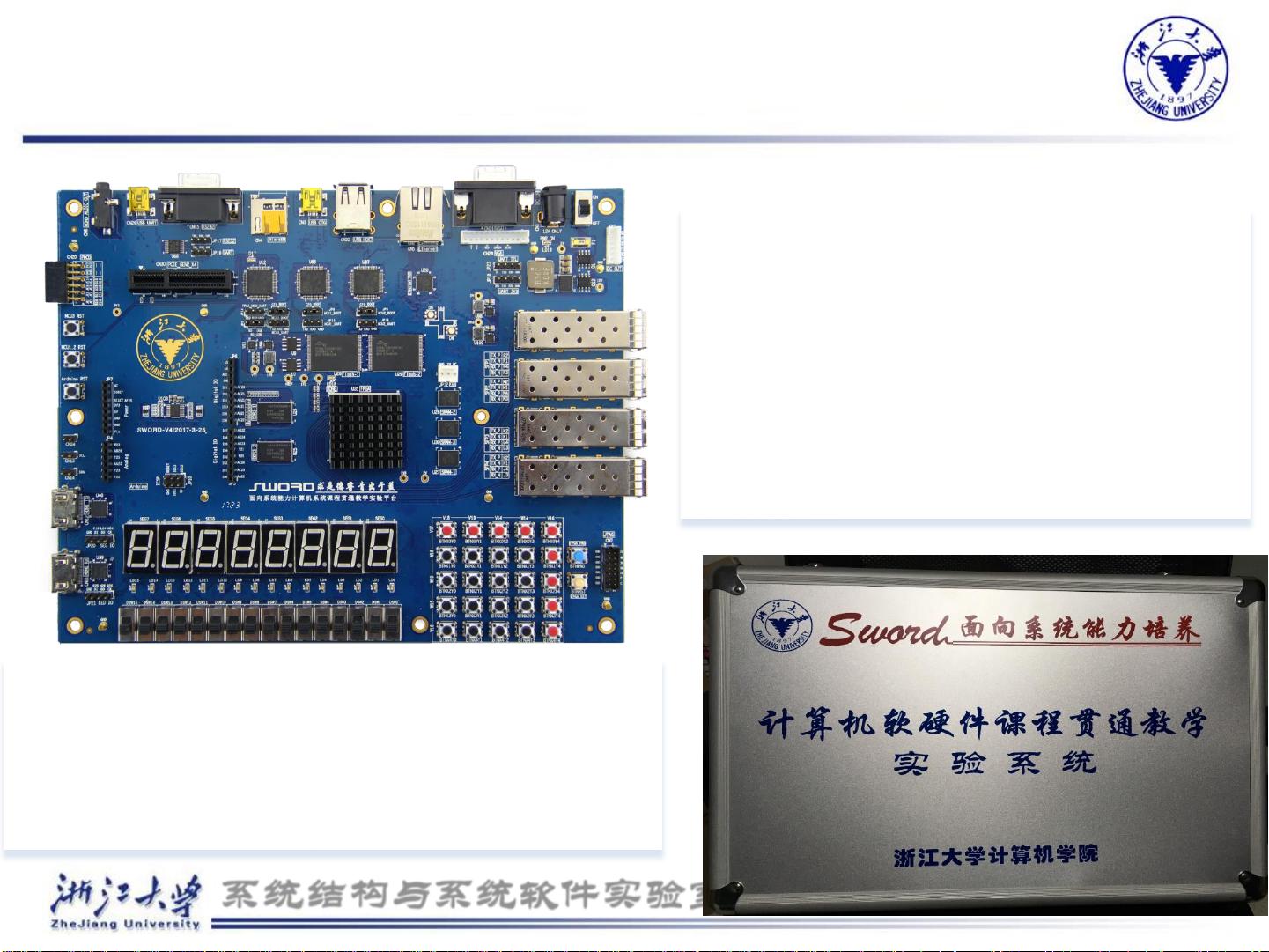

实验8“寄存器及寄存器堆设计1”是一个针对计算机软硬件课程的教学实验,旨在让学生掌握寄存器和寄存器堆的设计与实现。实验中,学生将使用计算机软硬件课程贯通教学实验系统SWORD4.0以及Xilinx ISE14.7及以上版本的开发工具进行实践。 实验环境主要包括高性能计算机、SWORD4.0实验系统和Xilinx的开发工具。SWORD4.0实验平台基于Xilinx Kintex™-7系列的XC7K325芯片,提供丰富的硬件资源,如片内存储、基本接口、标准接口和通信接口,支持多种功能的扩展,便于学生进行硬件设计和实现。 实验任务包括: 1. 设计一个32位时钟写入的寄存器,这意味着学生需要构建一个能够存储32位数据并在时钟脉冲上升沿更新的电路。 2. 设计一个8×32bits的寄存器堆,即一组包含8个32位寄存器的集合,用于存储和传输数据。 3. 集成实验环境接口,实现寄存器传输控制和ALU运算,这涉及到如何通过控制信号在寄存器之间进行数据传输以及执行基本的算术逻辑单元操作。 寄存器是计算机硬件中的核心组件,通常由一组边沿D触发器组成,每个触发器在时钟信号的上升沿更新其状态。实验中,8位基本寄存器的Verilog HDL描述展示了如何连接8个D触发器来形成一个8位寄存器,每个触发器都有时钟输入(clk),数据输入(D),清除(clear)和输出(Q)。在清除信号有效时,所有数据都会被清零,而在时钟上升沿,数据输入会被锁存到输出。 通过这个实验,学生不仅可以学习到寄存器和寄存器堆的硬件实现,还能深入理解计算机内部数据存储、传输和处理的基本机制。此外,实验还涵盖了基于总线的寄存器传输设计,这对于理解计算机系统中数据流动的方式至关重要。通过实际操作,学生可以更好地将理论知识转化为实践经验,提升计算机系统设计的能力。

剩余33页未读,继续阅读

- 粉丝: 41

- 资源: 294

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论0