没有合适的资源?快使用搜索试试~ 我知道了~

17061833於文卓_实验4寄存器堆设计实验1

需积分: 0 4 下载量 147 浏览量

2022-08-08

18:24:08

上传

评论

收藏 218KB DOCX 举报

温馨提示

试读

12页

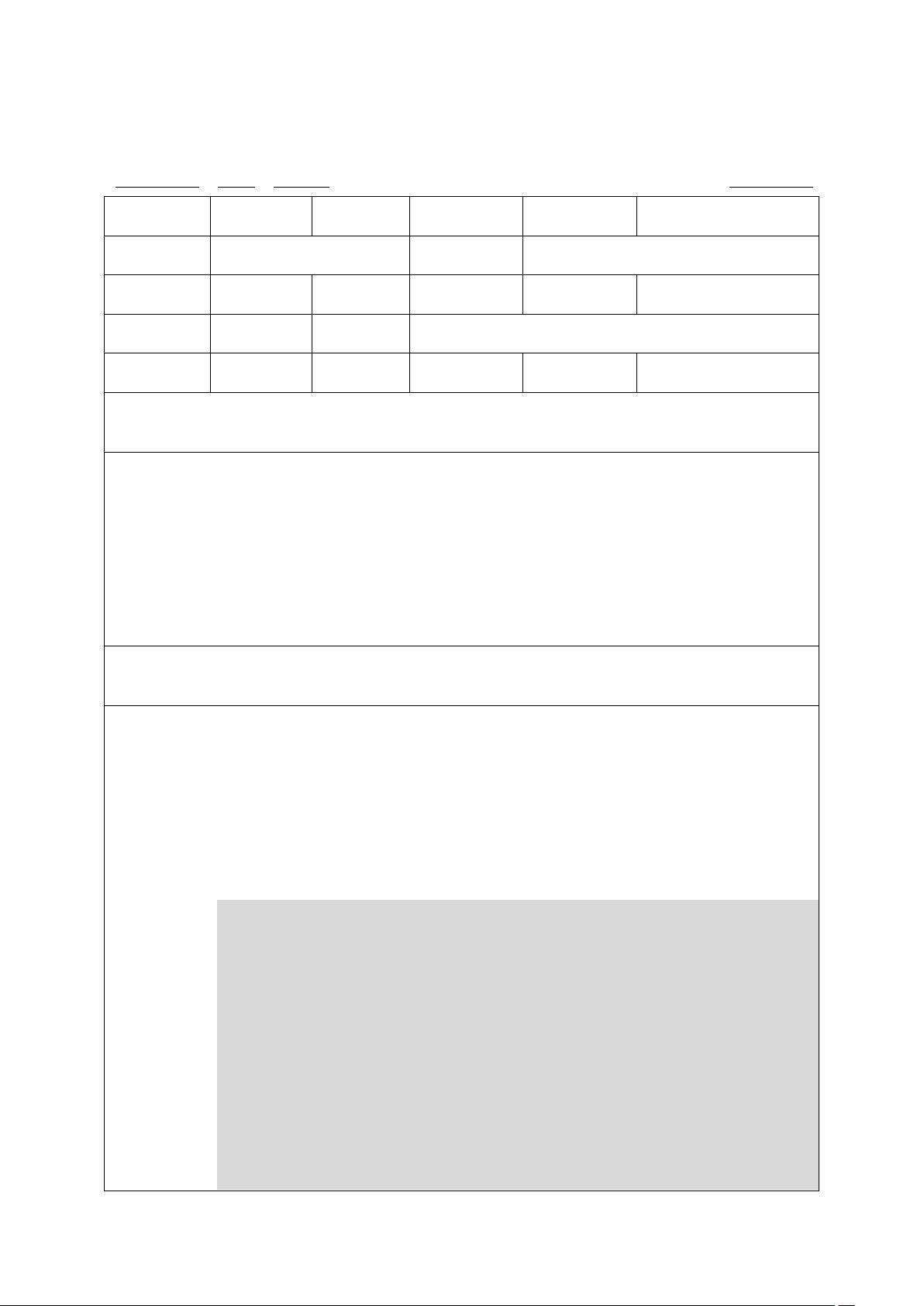

实验报告 2019 年 4 月 16 日 成绩: 姓名於文卓学号17061833班级17052317专业计算机科学与技术课程名称计算机组成原理课程设计任课老师冯

资源详情

资源评论

资源推荐

1

实验报告

2019 年 4 月 16 日 成绩:

姓名

於文卓

学号

17061833

班级

17052317

专业

计算机科学与技术

课程名称

计算机组成原理课程设计

任课老师

冯建文

指导老师

冯建文

机位号

实验序号

4

实验名称

寄存器堆设计实验

实验时间

4 月 16 日

实验地点

1-225

实验设备号

#9

一、实验目的与要求

1、 实验目的:

(1) 学习使用 Verilog HDL 语言进行时序电路的设计方法

(2) 掌握运用 Verilog HDL 进行行为描述与建模的技巧和方法

(3) 学习多端口寄存器堆的数据传送与读写工作原理,掌握多端口寄存器堆的设计方法

2、 实验要求:

(1) 设计一个 32*32 位的三端口寄存器,含有 32 个寄存器,每个寄存器 32 位。

(2) 三端口寄存器中,包含两个读端口和一个写端口,可同时读两个数据并写一个数据。

(3) 读出的数据使用数码管显示

二、实验设计与程序代码

1、 模块设计说明

(1) 设计 register_file 模块,主要输入为 5 位 R_Addr_A 读地址 A,R_Addr_B 读地址 B,W_Addr

写地址,32 位的写入数据 W_Data 和 Write_reg 信号。输出为读到的 A 和 B 的数据

(2) 构建数码管模块,使得 A 和 B 的数据显示在数码管上

(3) 构建顶层模块,调用寄存器堆模块和数码管模块。由于开关的限制,在顶层模块中用三

位的 choiceWriteData 选择八组数据送入寄存器堆中。

2、 实验程序源代码及注释等

(1) 寄存器堆模块代码

`timescale 1ns / 1ps

module register_file(

input [4:0]R_Addr_A,//读地址 A 0-32

input [4:0]R_Addr_B,//读地址 B 0-32

input [4:0]W_Addr,//写地址 0-32

input [31:0]W_Data,//写数据 32 位的数据

input Write_Reg,//写信号

input clk,

input reset_,

output [31:0]R_Data_A,//读到 A 数据

output [31:0]R_Data_B//读到 B 数据

);

2

integer i;

reg [31:0]REG_Files[0:31];//32 个寄存器堆,每个 32 位

assign R_Data_A = REG_Files[R_Addr_A];//读操作 A

assign R_Data_B = REG_Files[R_Addr_B];//读操作 B

//写操作

always@(posedge clk or negedge reset_)

begin

if(!reset_)

begin

for(i=0;i<31;i=i+1)

REG_Files[i] <= 32'h0000_0000;

end

else

begin

if(Write_Reg)

REG_Files[W_Addr] <= W_Data;

end

end

endmodule

(2) 数码管模块代码

module scan(

input clk,//100MHZ

input rst_,//reset

input [31:0]key,//通过拨动按钮控制段选

output reg [7:0]wei,//在 always 里赋值 需要用到 reg

output reg [7:0]duan

);

wire clk_4ms;//分频过后 2ms 一个方波(改过了 是 2ms 了)

reg [2:0]wei_count;//位码计数器,控制 4 个数码管

reg [7:0]segcode[0:15] = {//用数组的方式定义 左表示位数 右表示个数

8'b0000_0011,//0

8'b1001_1111,//1

8'b0010_0101,//2

8'b0000_1101,//3

8'b1001_1001,//4

8'b0100_1001,//5

8'b0100_0001,//6

8'b0001_1111,//7

8'b0000_0001,//8

8'b0000_1001,//9

3

~8'b11101110,//A

~8'b00111110,//b

~8'b10011100,//C

~8'b01111010,//d

~8'b10011110,//E

8'b01110001//F

};

div f1(rst_,clk,clk_4ms);//分频器模块

wire clk_slow;//一秒钟两次

div_slow f2(rst_,clk,clk_slow);

always @(posedge clk_4ms or negedge rst_)//每一个上升沿都使得计数器+1 做到连续扫描数码管

begin

if(!rst_)

begin

wei_count<=3'b00;

end

else

begin

wei_count<=wei_count+1'b1;

if(wei_count ==3'b111)

begin

wei_count<=3'b000;

end

end

end

reg [7:0] pos_1,pos_2,pos_3,pos_4,pos_5,pos_6,pos_7,pos_8;

//用开关控制数码管显示

always @(posedge clk_4ms or negedge rst_)

begin

if(!rst_)

begin

pos_1 <= 4'b0000;

pos_2 <= 4'b0000;

pos_3 <= 4'b0000;

pos_4 <= 4'b0000;

pos_5 <= 4'b0000;

pos_6 <= 4'b0000;

pos_7 <= 4'b0000;

pos_8 <= 4'b0000;

end

剩余11页未读,继续阅读

不能汉字字母b

- 粉丝: 13

- 资源: 291

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0