EDA课程设计报告_数字钟

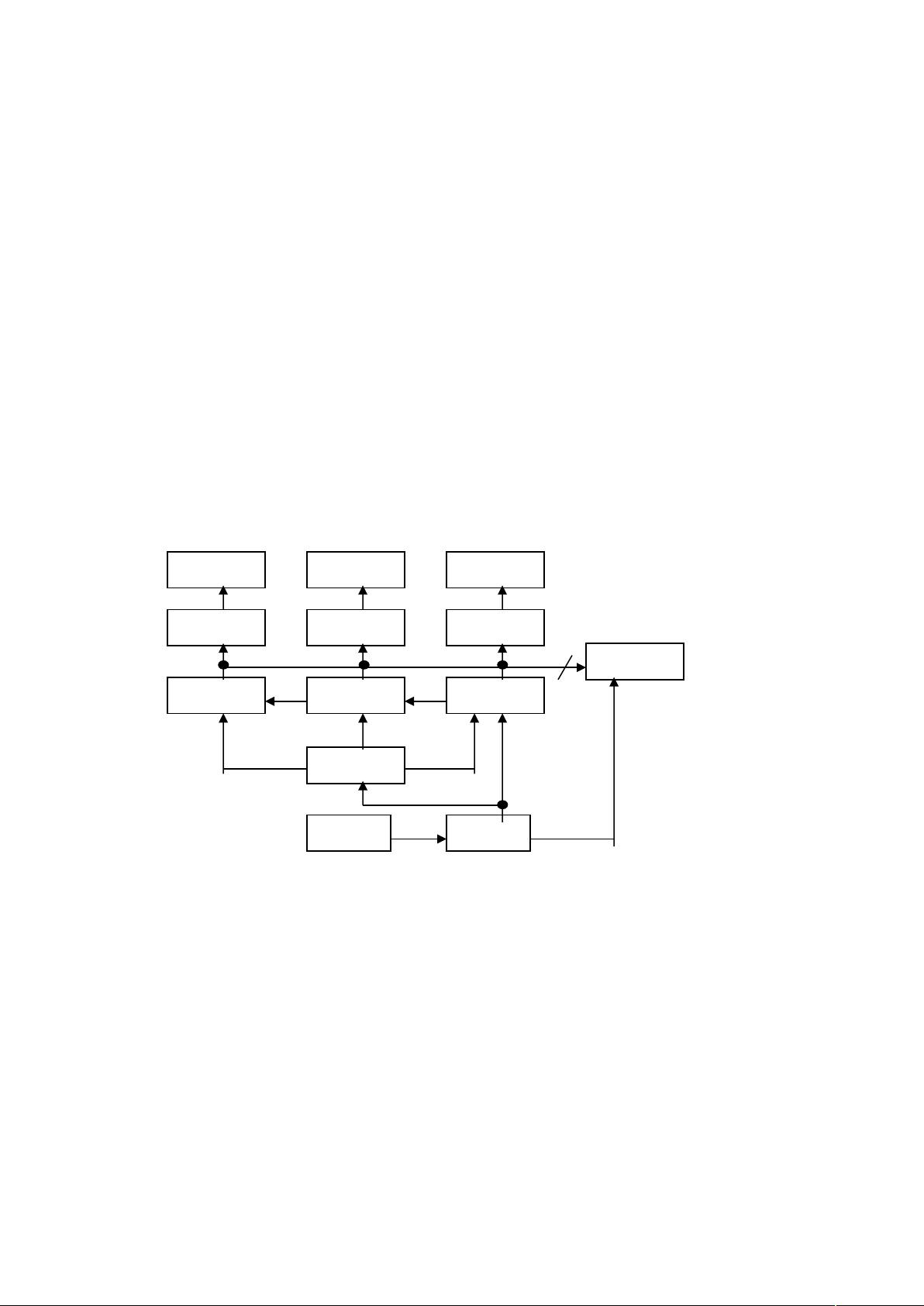

**EDA课程设计报告_数字钟**\n\n在当今信息化社会中,电子设计自动化(EDA)技术已经成为电子系统设计的核心工具。EDA技术的不断发展和普及,显著提升了电子产品的设计速度和质量,对于电子信息产业的推进起到了关键作用。学生和工程师需要掌握EDA技术,特别是VHDL或Verilog这样的硬件描述语言,以便于设计复杂电子系统。\n\n本设计项目的目标是使用EDA平台,特别是VHDL语言,来构建一个24小时制的电子数字钟。该数字钟不仅能够准确计时,还能提供校时和闹钟功能。设计中,程序由多个独立模块组合而成,包括分频器、计数器、数据选择器、显示模块以及例化模块。利用Quartus II软件进行仿真,以确保设计的正确性,最终将设计下载到EDA实验箱进行实际验证。\n\n设计任务包括:\n1. 使用实验箱的时钟信号进行分频,产生秒脉冲。\n2. 实现24进制的计时计数器。\n3. 提供手动校时功能,可分别调整时、分。\n4. 实现整点报时功能。\n5. 增加闹钟功能,当达到预设时间时,通过扬声器发出报警,持续4秒,并可提前停止。\n\n设计原理如下:\n\n- **方案选择**:数字钟基于分频计数原理。秒分计数采用60进制,时计数采用24进制。通过分频器,将1Hz信号分频为60Hz(用于分钟计数)和3600Hz(用于小时计数)。为便于校时和设置闹钟,选择了65536Hz的振荡器,经过32768分频产生秒脉冲,8192分频产生校时和闹钟设置脉冲。数据选择器用于在正常时间和闹钟时间之间切换,实验箱自带的译码器处理数码管的译码工作。\n\n- **数字钟工作原理**:数字钟由振荡器、分频器、计数器、译码器和显示器等部分构成。石英晶体振荡器产生的时基信号经过分频,进入60进制的秒计数器、60进制的分计数器和24进制的时计数器,逐级累加。计数器的输出通过译码器转化为可显示的数字,显示在数码管上。校时电路允许用户修正时间,而整点报时电路则根据计时状态在整点时触发报时信号。\n\n- **扩展功能**:闹钟功能通过比较当前时间与预设闹钟时间来触发。当计时达到预设值,扬声器发出报警声,持续4秒。用户可以随时终止闹铃。此功能增加了数字钟的实用性。\n\n通过这个EDA课程设计项目,学生可以深入理解数字系统设计方法,熟练运用VHDL语言,并且提升解决复杂设计问题的能力。设计完成后,通过电路仿真和实物验证,能够确保设计的正确性和可靠性,从而为未来电子工程领域的实践打下坚实基础。

剩余16页未读,继续阅读

- 粉丝: 160

- 资源: 50

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- anaconda和pycharm2020版本安装包

- 316L超低碳不锈钢埋弧焊焊接工艺探讨.pdf

- 316L不锈钢扩散焊接头高温蠕变性能.pdf

- 316L壳体的焊接.pdf

- 316N不锈钢管的焊接工艺探讨 - .pdf

- k8s网络通信组件cni插件cni-plugins-linux-arm64-v0.8.7.tgz

- 600MW超临界机组SA335-P91钢免根透焊接工艺控制 - .pdf

- 600MW机组管道焊接、热处理及无损检验施工.pdf

- 620℃超超临界机组用9% Cr-Mo-Co-B钢(CB2)焊接接头性能退化机制研究-学兔兔 www.xuetutu.com.pdf

- 700 MPa级低合金高强钢低匹配焊接接头组织和性能研究.pdf

- 800MPa及以上低合金高强钢焊接现状 - .pdf

- 904L材料的焊接 - .pdf

- 1000m^3LPG卧式储罐用07MnNiCrMoVDR钢的焊接与热处理.pdf

- 980MPa级高强钢焊接性的研究现状 - .pdf

- 2000 kN·m大型行星减速器焊接机体应力分析.pdf

- 机械设计奶酪生产包装线stp非常好的设计图纸100%好用.zip

信息提交成功

信息提交成功