设计和修改计数器进制的方法 (3).docx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

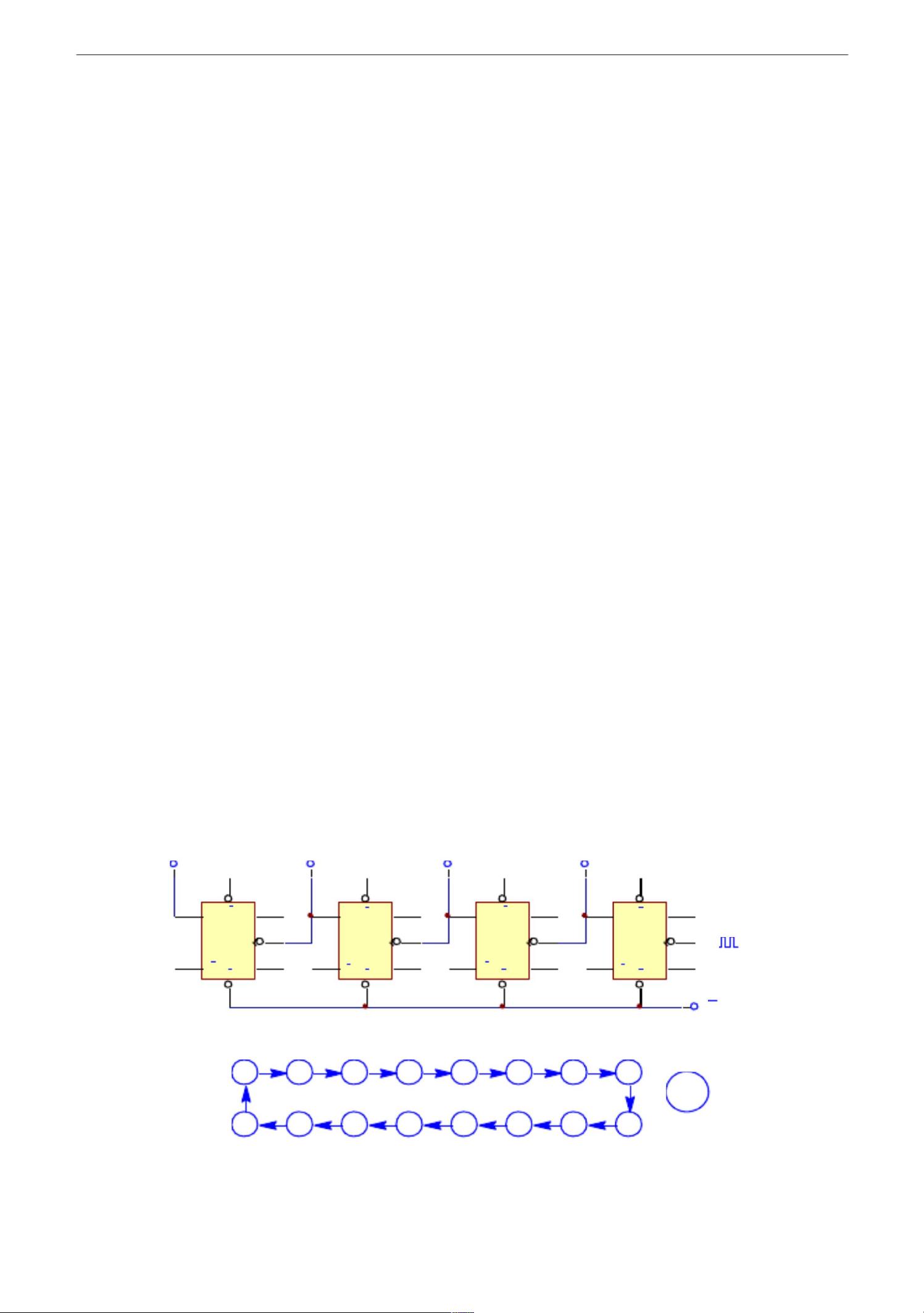

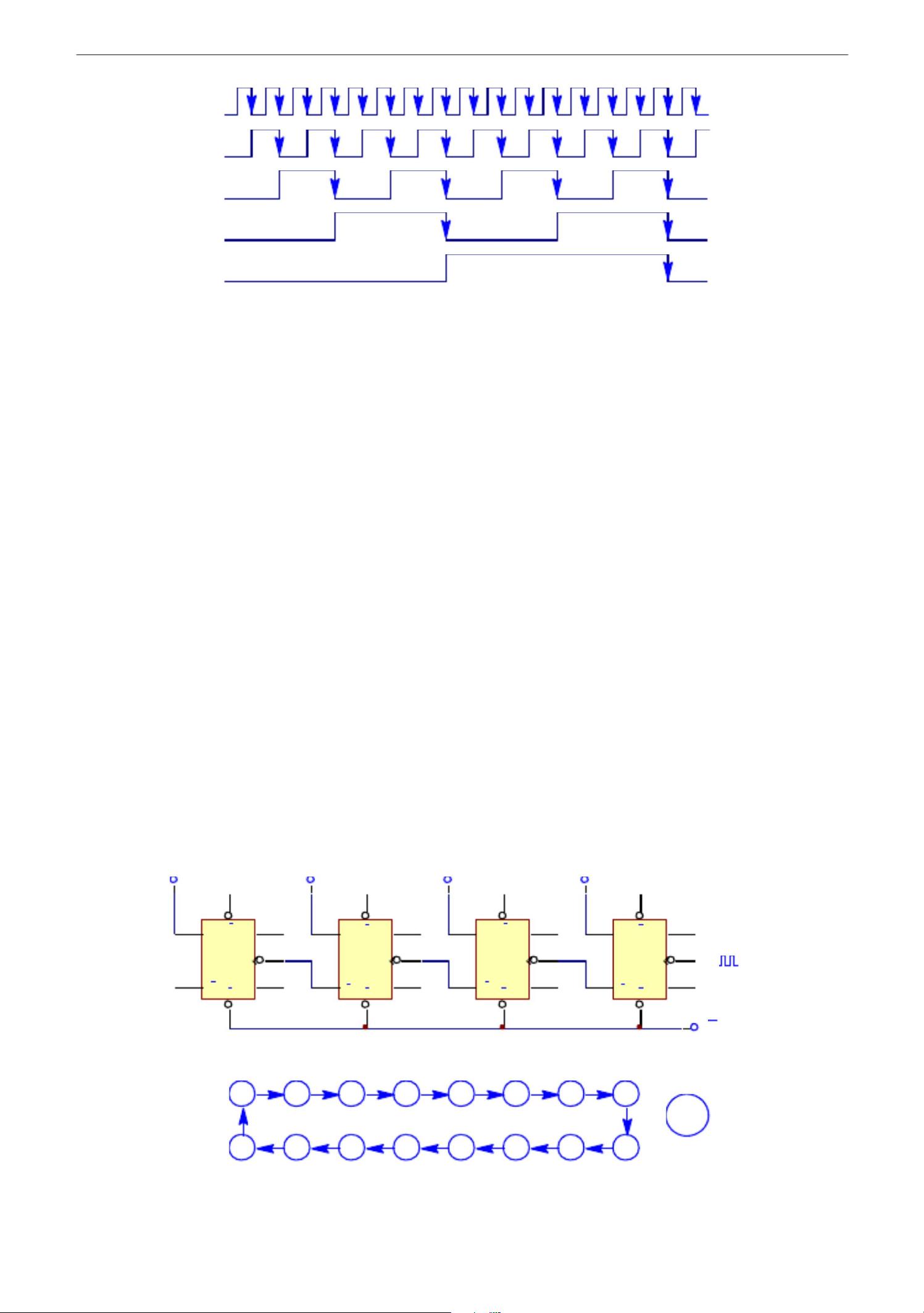

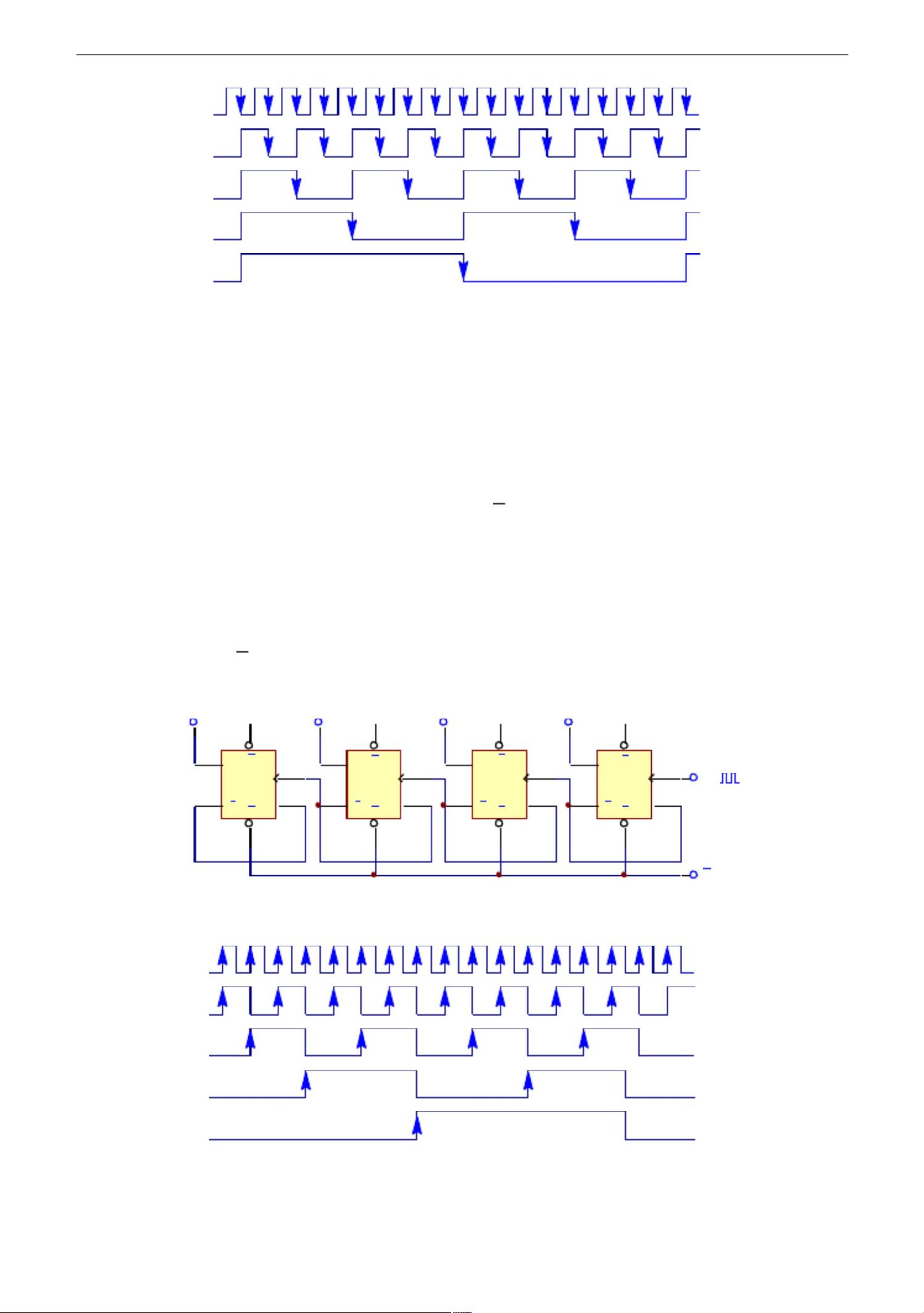

计数器是数字系统中非常重要的组成部分,它们用于统计输入脉冲的数量,或者在更复杂的系统中用作分频器和定时器。本实验重点介绍了如何设计和修改计数器的进制,主要关注二进制和非二进制计数器的实现。 实验的目的在于让学生熟悉基于集成触发器构建的计数器电路的工作原理,并熟练掌握中规模集成电路计数器的应用。实验所需的设备包括数字实验箱、各种集成电路(如74LS112、74LS74、74LS193等)、以及示波器。这些集成电路都是数字电路设计中常用的器件,其中74LS系列是经典的TTL逻辑门电路。 计数器的分类主要依据计数体制、计数方法和计数脉冲的引入方式。按照计数体制,计数器分为二进制计数器和非二进制计数器,如十进制计数器和任意进制计数器。根据计数方法,计数器可以是加法计数器(递增)、减法计数器(递减)或可逆计数器(既能递增也能递减)。而根据计数脉冲的引入方式,计数器分为同步计数器(所有触发器同时响应脉冲)和异步计数器(触发器响应脉冲的时间不一致)。 实验中详细阐述了异步二进制加法计数器的构造,以74LS112双JK触发器为例。这种计数器的结构相对简单,通过将触发器配置为T'触发器,利用CP(时钟脉冲)下降沿触发翻转。例如,图7.1(a)展示了一个4位二进制(十六进制)异步加法计数器的逻辑图,其中Q3Q2Q1Q0表示四位二进制计数值。状态图和时序图(波形图)进一步解释了计数过程,展示了每个计数脉冲下Q0至Q3状态的演变,以及各触发器状态变化与CP之间的关系。 此外,实验还涵盖了异步减法计数器的设计,如图7.2(a)所示,同样是使用74LS112构成的电路,但配置和连接方式不同,使得计数器在每个计数脉冲下递减计数。状态图和时序图展示了Q0至Q3在减法计数过程中的变化,反映了计数器从最高状态到最低状态的转换。 通过这样的实验,学生不仅能理解不同类型的计数器工作原理,还能掌握实际电路设计中的技巧,如触发器的配置和门电路的使用。这对于理解和应用数字逻辑设计的基本概念至关重要。同时,这些知识对于后续学习更复杂的计数器,如模N计数器、同步计数器、环形计数器、Johnson计数器等,奠定了坚实的基础。

剩余13页未读,继续阅读

- 粉丝: 4040

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功