没有合适的资源?快使用搜索试试~ 我知道了~

TI-SN74LVTH16245A-EP.pdf

需积分: 5 0 下载量 138 浏览量

2022-11-29

18:35:16

上传

评论 4

收藏 985KB PDF 举报

温馨提示

试读

17页

TI-SN74LVTH16245A-EP.pdf

资源推荐

资源详情

资源评论

www.ti.com

FEATURES

DGG,DGV,ORDL PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1DIR

1B1

1B2

GND

1B3

1B4

V

CC

1B5

1B6

GND

1B7

1B8

2B1

2B2

GND

2B3

2B4

V

CC

2B5

2B6

GND

2B7

2B8

2DIR

1OE

1A1

1A2

GND

1A3

1A4

V

CC

1A5

1A6

GND

1A7

1A8

2A1

2A2

GND

2A3

2A4

V

CC

2A5

2A6

GND

2A7

2A8

2OE

SN74LVTH16245A-EP

3.3-V ABT 16-BIT BUS TRANSCEIVER

WITH 3-STATE OUTPUTS

SCAS693G – APRIL 2003 – REVISED OCTOBER 2006

• Controlled Baseline

– One Assembly

– One Test Site

– One Fabrication Site

• Enhanced Diminishing Manufacturing

Sources (DMS) Support

• Enhanced Product-Change Notification

• Qualification Pedigree

(1)

• Member of the Texas Instruments Widebus™

Family

• State-of-the-Art Advanced BiCMOS

Technology (ABT) Design for 3.3-V Operation

and Low Static-Power Dissipation

• Supports Mixed-Mode Signal Operation (5-V

Input and Output Voltages With 3.3-V V

CC

)

• Supports Unregulated Battery Operation

Down to 2.7 V

• Typical V

OLP

(Output Ground Bounce) <0.8 V

at V

CC

= 3.3 V, T

A

= 25 ° C

• Distributed V

CC

and GND Pins Minimize

High-Speed Switching Noise

• Flow-Through Architecture Optimizes PCB

Layout

• I

off

and Power-Up 3-State Support Hot

Insertion

• Bus Hold on Data Inputs Eliminates the Need

for External Pullup/Pulldown Resistors

• Latch-Up Performance Exceeds 500 mA Per

JESD 17

• ESD Protection Exceeds JESD 22

– 2000-V Human-Body Model (A114-A)

– 200-V Machine Model (A115-A)

(1) Component qualification in accordance with JEDEC and

industry standards to ensure reliable operation over an

extended temperature range. This includes, but is not limited

to, Highly Accelerated Stress Test (HAST) or biased 85/85,

temperature cycle, autoclave or unbiased HAST,

electromigration, bond intermetallic life, and mold compound

life. Such qualification testing should not be viewed as

justifying use of this component beyond specified

performance and environmental limits.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Copyright © 2003–2006, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

www.ti.com

DESCRIPTION/ORDERING INFORMATION

GQL ORZQL PACKAGE

(TOP VIEW)

A

B

C

D

E

F

G

H

J

K

1 2

3

4

5 6

SN74LVTH16245A-EP

3.3-V ABT 16-BIT BUS TRANSCEIVER

WITH 3-STATE OUTPUTS

SCAS693G – APRIL 2003 – REVISED OCTOBER 2006

The SN74LVTH16245A is a 16-bit (dual-octal) noninverting 3-state transceiver designed for low-voltage (3.3-V)

V

CC

operation, but with the capability to provide a TTL interface to a 5-V system environment.

This device can be used as two 8-bit transceivers or one 16-bit transceiver. It allows data transmission from the

A bus to the B bus or from the B bus to the A bus, depending on the logic level at the direction-control (DIR)

input. The output-enable (OE) input can be used to disable the devices so that the buses effectively are isolated.

Active bus-hold circuitry holds unused or undriven inputs at a valid logic state. Use of pullup or pulldown

resistors with the bus-hold circuitry is not recommended.

When V

CC

is between 0 V and 1.5 V, the device is in the high-impedance state during power up or power down.

However, to ensure the high-impedance state above 1.5 V, OE should be tied to V

CC

through a pullup resistor;

the minimum value of the resistor is determined by the current-sinking capability of the driver.

This device is fully specified for hot-insertion applications using I

off

and power-up 3-state. The I

off

circuitry

disables the outputs, preventing damaging current backflow through the device when it is powered down. The

power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down,

which prevents driver conflict.

TERMINAL ASSIGNMENTS

(1)

1 2 3 4 5 6

A 1DIR NC NC NC NC 1 OE

B 1B2 1B1 GND GND 1A1 1A2

C 1B4 1B3 V

CC

V

CC

1A3 1A4

D 1B6 1B5 GND GND 1A5 1A6

E 1B8 1B7 1A7 1A8

F 2B1 2B2 12A2 2A1

G 2B3 2B4 GND GND 2A4 2A3

H 2B5 2B6 V

CC

V

CC

2A6 2A5

J 2B7 2B8 GND GND 2A8 2A7

K 2DIR NC NC NC NC 2 OE

(1) NC – no internal connection

ORDERING INFORMATION

T

A

PACKAGE

(1)

ORDERABLE PART NUMBER TOP-SIDE MARKING

SSOP – DL Tape and reel CLVTH16245AQDLREP LH16245AEP

–40 ° C to 125 ° C

TSSOP – DGG Tape and reel CLVTH16245AQDGGREP LH16245AEP

TVSOP – DGV Tape and reel CLVTH16245AIDGVREP LL245AEP

VFBGA – GQL CLVTH16245AIGQLREP

–40 ° C to 85 ° C

Tape and reel LL245AEP

VFBGA – ZQL

CLVTH16245AIZQLREP

(Pb-free)

–55 ° C to 125 ° C SSOP – DL Tape and reel CLVTH16245AMDLREP LH16245AEP

(1) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at

www.ti.com/sc/package.

2

Submit Documentation Feedback

www.ti.com

ToSevenOtherChannels

1DIR

1A1

1B1

1OE

ToSevenOtherChannels

2DIR

2A1

2B1

2OE

1

47

24

36

48

2

25

13

Absolute Maximum Ratings

(1)

SN74LVTH16245A-EP

3.3-V ABT 16-BIT BUS TRANSCEIVER

WITH 3-STATE OUTPUTS

SCAS693G – APRIL 2003 – REVISED OCTOBER 2006

FUNCTION TABLE

(each 8-bit section)

INPUTS OPERATION

OE DIR

L L B data to A bus

L H A data to B bus

H X Isolation

LOGIC DIAGRAM (POSITIVE LOGIC)

over operating free-air temperature range (unless otherwise noted)

MIN MAX UNIT

V

CC

Supply voltage range –0.5 4.6 V

V

I

Input voltage range

(2)

–0.5 7 V

V

O

Voltage range applied to any output in the high-impedance or power-off state

(2)

–0.5 7 V

V

O

Voltage range applied to any output in the high state

(2)

–0.5 V

CC

+ 0.5 V

SN74LVTH16245A(Q/M) 96

I

O

Current into any output in the low state mA

SN74LVTH16245AI 128

SN74LVTH16245A(Q/M) 48

I

O

Current into any output in the high state

(3)

mA

SN74LVTH16245AI 64

I

IK

Input clamp current V

I

< 0 –50 mA

I

OK

Output clamp current V

O

< 0 –50 mA

DGG package 70

DGV package 58

θ

JA

Package thermal impedance

(4)

° C/W

DL package 63

GQL/ZQL package 42

T

stg

Storage temperature range –65 150 ° C

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

(3) This current flows only when the output is in the high state and V

O

> V

CC

.

(4) The package thermal impedance is calculated in accordance with JESD 51-7.

3

Submit Documentation Feedback

www.ti.com

Recommended Operating Conditions

(1)

SN74LVTH16245A-EP

3.3-V ABT 16-BIT BUS TRANSCEIVER

WITH 3-STATE OUTPUTS

SCAS693G – APRIL 2003 – REVISED OCTOBER 2006

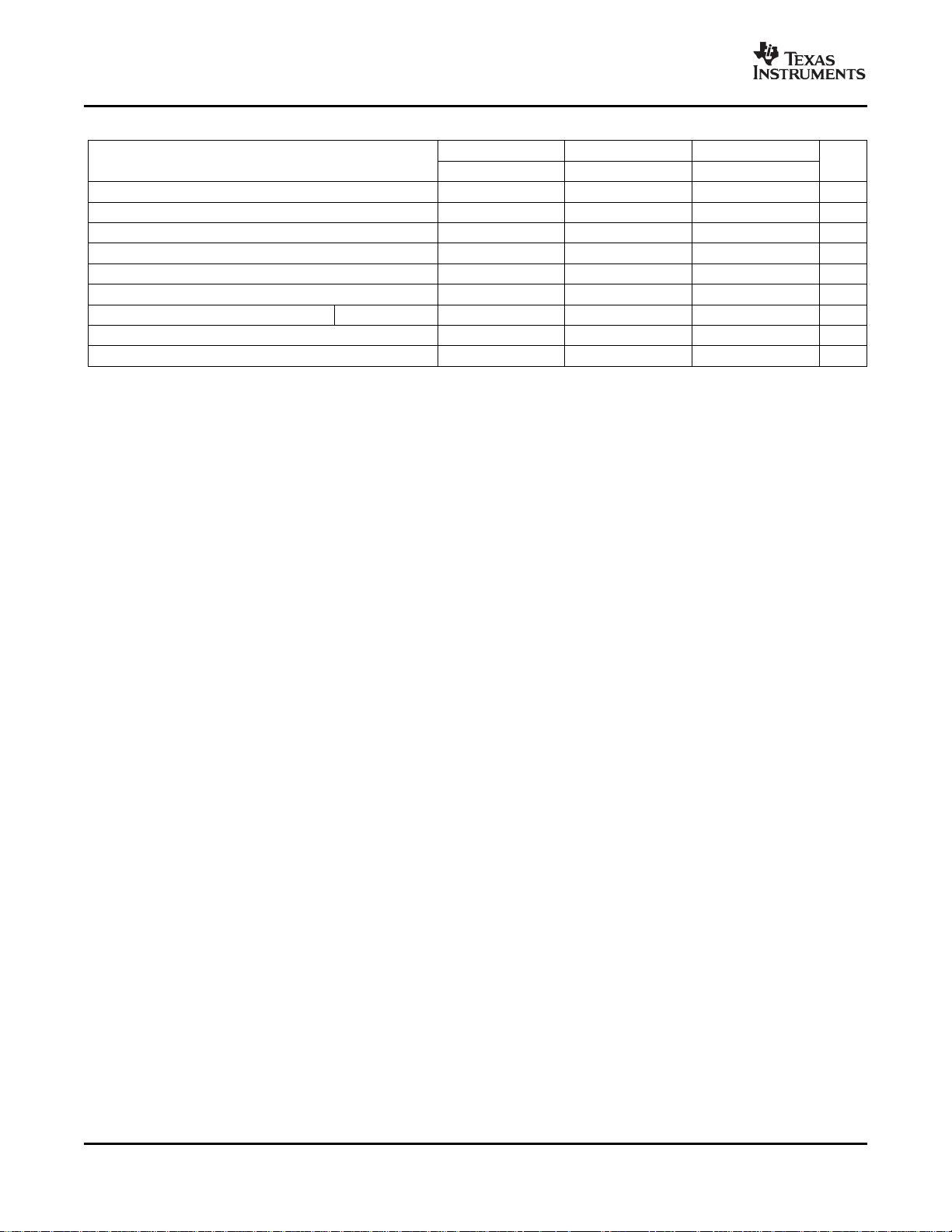

SN74LVTH16245AQ SN74LVTH16245AI SN74LVTH16245AM

UNIT

MIN MAX MIN MAX MIN MAX

V

CC

Supply voltage 2.7 3.6 2.7 3.6 2.7 3.6 V

V

IH

High-level input voltage 2 2 2 V

V

IL

Low-level input voltage 0.8 0.8 0.8 V

V

I

Input voltage 5.5 5.5 5.5 V

I

OH

High-level output current –24 –32 –24 mA

I

OL

Low-level output current 24 64 24 mA

∆ t/ ∆ v Input transition rise or fall rate Outputs enabled 10 10 10 ns/V

∆ t/ ∆ V

CC

Power-up ramp rate 200 200 200 µ s/V

T

A

Operating free-air temperature –40 125 –40 85 –55 125 ° C

(1) All unused control inputs of the device must be held at V

CC

or GND to ensure proper device operation. See the TI application report,

Implications of Slow or Floating CMOS Inputs (SCBA004).

4

Submit Documentation Feedback

剩余16页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3122

- 资源: 5370

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功